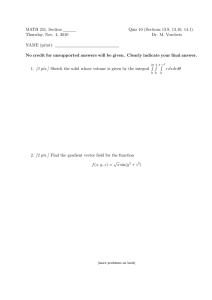

Quiz+#4-Solution

advertisement

Name: Case Network ID (Email): EECS 322 & 415 – Integrated Circuit Technology – Fall 2018 Quiz #4 (Take-Home on Tue, Nov. 20, 2018) – Due in Class, Tuesday, November 27, 2018 1. Review Chapter 6 on Thermal Oxidation. Answer the following questions. (10 pts) Assume that you were going to create a SiO2 layer to serve as the insulating layer for a modern MOS-based transistor. (a) What type of thermal oxidation process would you select, and why? (5 pts) (b) What type of oxidation system might you consider using, and why? (5pts) Answers: (a) Dry oxidation is preferred over wet and steam oxidation. This is because the key insulating layer in a MOSFET is the gate insulator. These layers are typically very thin (<50 nm) and thus should be grown using a process that affords a very high level of thickness control. Growth rates for dry oxidation processes are by far the lowest of the three, thereby giving the highest level of process control. (b) Rapid Thermal Oxidation systems are quite attractive for the growth of gate oxides because: 1. They utilize small chambers that are equipped with vacuum systems, enabling rapid control of oxidant flow/concentration. 2. Their small size combined with IR heating enables very rapid temperature ramps (up and down). Oxidation processes are highly dependent on oxidant concentration and temperature, so rapid response systems are favored in applications where ultrathin films with precise thickness control are needed. 2. Briefly explain thermal oxidation of single crystal Si in terms of defects in the lattice structure. (6 pts) Answers: Oxidation of Si results in the generation of interstitials and the consumption of vacancies. The rates are not equal and the net result is the generation of stress in the films. 3. Provide a qualitative description of the Deal-Grove model for thermal oxidation of Si. Be sure to include any assumption required of the model. (8 pts) Answers: The Deal-Grove model describes thermal oxidation in terms of three fluxes. The first flux represents the transport of the oxidant in the gas phase to the substrate surface. The second flux represents the diffusion of oxidant through the oxide film to the oxide-silicon interface. The third flux represents the rate at which the silicon is oxidized. For steady state conditions, the three fluxes are equal. -1- Name: Case Network ID (Email): The model requires that an oxide be present on the Si surface at the onset of oxidation so that the second flux is relevant and non-zero. 4. Review Chapter 7 on Dopant Diffusion. Answer the following questions (16 pts) (a) What is solid solubility? (3 pts) (b) What doping process is heavily dependent on solid solubility? (3 pts) (c) How is this doping process performed? (5 pts) (d) Explain how solid solubility relates to electrical solubility? (5 pts) Answers: (a) Solubility is defined as the maximum concentration of a dopant that can be dissolved in a substrate under equilibrium conditions without forming a precipitate. (b) Solid source diffusion is process that is heavily dependent on solid solubility. Gas phase diffusion is also heavily dependent on solid solubility. (c) Solid source diffusion is typically performed in large-scale high temperature furnaces that are constructed in much the same manner as oxidation furnaces. Both the pre-deposition and drive-in steps are performed at high temperature. The pre-deposition step is typically performed at the solid solubility limit of the dopant in silicon. (d) Electrical solubility is the maximum concentration of dopants that are electrically active. Electrically active dopants are generally at concentrations significantly lower than the solid solubility due in large measure because electrical activity requires dopants to be in lattice sites, while solid solubility accounts for dopants that are both in lattice sites as well as interstitial sites. 5. Other than their position in the Si band structure, give three reasons why As, P, and B are preferred as dopants in Si over other possible elements. (9 pts) Answers: 1. Available in gaseous and solid sources 2. High solubility relative to other dopants. 3. High diffusivity relative to other dopants. 6. We discussed two important deviations to Fick’s Laws of Diffusion that affect silicon IC processing. (11 pts) (a) Of the two, which can be advantageous for semiconductor processing? (2 pts) (b) Describe this effect. (4 pts) (c) Why would it be advantageous and where might we see it being used? (5 pts) Answers: (a) Concentration enhanced diffusion. (b) The diffusivity of a dopant is sometimes dependent on its concentration. For low concentrations, diffusion is Fickian, but for high concentration, the diffusivity is enhanced and the dopant concentration is much higher at a given depth than would be predicted by Fick’s Laws. -2- Name: Case Network ID (Email): (c) The formation of sharp junctions between heavily-doped and lightly doped regions is aided by concentration-enhanced diffusion because the enhancement suppresses the Gaussian-like leading edge associated with Fickian diffusion and instead results in a boxlike profile in the heavily doped region. Such structures may be found in source/channel and drain/channel junctions of a MOSFET and the emitter/base junction of a BJT. 7. Review Chapter 8 on Ion Implantation. Answer the following questions. (18 pts) Ion implantation is usually followed by a second processing step. (a) What is the name of this step? (2 pts) (b) Name the key processing parameter for this step and give a rough value for this parameter. (2 pts) (c) List three goals/objectives for this processing step. (6 pts) (d) List one adverse effect that the process engineer may face in performing this step. (4 pts) (e) What technique can be used to minimize this effect and why is it effective? (4 pts) Answers: (a) Drive-in (or Anneal) (b) Temperature, ~ 1000°C (c) Electrically activate dopants, reconstruct damaged lattice, redistribute dopants. (d) Transient enhanced diffusion at moderate temps (~ 800°C) during the temperature ramp up and ramp down that leads to excessive drive in and dopant redistribution. (e) Use rapid thermal annealing. The high ramp up and ramp down rates (~ 100ºC/s) minimizes the time it takes to ramp up to the annealing temperature and cool back to room temperature. 8. A process engineer finds that the distribution of dopants after an implantation step is deeper than anticipated based on first principle calculations. (10 pts) (a) What must have occurred during the implantation step? (2 pts) (b) Describe this phenomenon. (4 pts) (c) What two options does this process engineer have to mitigate this effect? (4 pts) Answers: (a) Channeling (b) Implanted ions enter the substrate in the interstitial space between lattice atoms. If the interstitial space is aligned with the ion beam, interactions with lattice atoms will occur beneath the surface. Models assume that these interactions begin to occur at the surface due to a random distribution of target atoms. (c) 1. Tilt the substrate to misalign the channels with respect to the ion beam 2. Deposit a thin amorphous layer on the substrate to induce scattering events at the surface. 9. The graph below compares implant profiles for the four most commonly used dopants in silicon. The implant energy for each ion is 200 keV: (12 pts) -3- Name: Case Network ID (Email): (a) What two important parameters are illustrated in this graph? (4 pts) (b) Compare/contrast these two parameters with respect to atomic mass. (4 pts) (c) Based on the data in this graph, what can be said about electric and nuclear stopping powers with respect to atomic mass. (4 pts) Answers: (a) Range, Straggle (b) 1. The range of is mass dependent, with lighter ions penetrating deeper than heavy ions. 2. The straggle mass dependent, with lighter ions having larger straggle than heavy ions. (c) For light ions, electric energy loss interactions take place over a longer distance into the substrate than for heavy ions. -4-