Diseño e Implementación de un Circuito Secuencial: Contador binario

advertisement

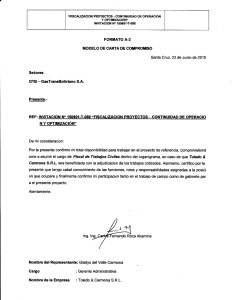

ELECTRÓNICA DIGITAL I TRABAJO PRÁCTICO 2 Diseño e Implementación de un Circuito Secuencial: Contador binario Integrantes: Rodriguez Mathieu, Alan E.__________________39499363 Fissore Lorenzo ____________________________93958203 Profesor: Ing. Cáceres, Oscar Año: 2017 Consigna: Diseñar e implementar un circuito secuencial síncrono utilizando flip flop JK los cuales deberán “contar” de manera ascendente los números binarios del 0 al 9. Los bit de salida se conectarán a un decodificador 7 segmentos para mostrar la cuenta en un display, la frecuencia del clock queda a elección del alumno. Desarrollo: Un flip flop es un circuito combinacional realimentado. Para este trabajo utilizamos Flip Flop JK los cuales presentan la siguiente configuración: La cual se forma a través de un FF S-R agregándole compuertas NAND en sus entradas, esto permite que, a diferencia de un FF S-R, este tenga condiciones validad para todas las combinaciones de entrada. A continuación se muestra la tabla de transiciones del FF JK,la cual se utiliza para la relación en la tabla de verdad Q(t) 0 0 1 1 0 1 2 3 4 5 6 Q(t+1) 0 0 0 1 Q(t) Q3 0 0 0 0 0 0 0 Q2 0 0 0 0 1 1 1 Q1 0 0 1 1 0 0 1 Q0 1 0 1 0 1 0 1 J 0 1 X X Q(t+1) Q3 Q2 0 0 0 0 0 0 0 1 0 1 0 1 0 1 Q1 0 1 1 0 0 1 1 Q0 1 0 1 0 1 0 1 K X X 1 0 J3 0 0 0 0 0 0 0 K3 X X X X X X X J2 0 0 0 1 X X X K2 X X X X 0 0 0 J1 0 1 X X 0 1 X K1 X X 0 1 X X 0 J0 1 X 1 X 1 X 1 K0 X 1 X 1 X 1 X 7 8 9 0 1 1 1 0 0 1 0 0 0 1 0 1 1 0 0 0 0 0 0 0 0 1 0 1 X X X 0 1 X 0 0 1 X X X 0 0 1 X X X 1 X 1 X 1 Seguidamente, mostramos los Mapas de Karnaugh que se plantearon en base a la tabla de verdad, las funciones lógicas obtenidas a partir de cada mapa, y su desarrollo mediante la aplicación del Teorema de De Morgan. La aplicación de este teorema nos permite optimizar las funciones lógicas y de esa manera ahorrar en el uso de compuertas. J3 00 Q1Q0 00 01 11 10 Q3Q2 01 11 10 X X 1 K3 Q1Q0 J2 00 Q1Q0 00 01 11 10 1 J1 00 Q1Q0 00 01 11 10 1 X X J0 Q1Q0 00 01 11 10 00 1 X X 1 Q3Q2 01 11 X X X X Q3Q2 01 11 K2 10 Q1Q0 K1 10 Q1Q0 1 X X Q3Q2 01 11 1 X X 1 00 01 11 10 00 01 11 10 00 X X X X 00 X X X X 00 01 11 10 00 X X 1 K0 10 1 X Q1Q0 00 01 11 10 00 X 1 1 X Q3Q2 01 11 XX X QX3Q2 X 01 11 10 1 10 X X 1 Q3Q2 01 11 X X 1 Q3Q2 01 11 X 1 1 X 10 X X 10 X 1 FUNCIONES: J3 : Q3 . Q2 . Q1 . Q0 K3: Q2 . Q1 . Q0 J2: Q3 . Q1 . Q0 K2: Q3 . Q1 . Q0 J1: Q3 . Q0 K1: Q3 . Q0 J0: Q3 + Q2 . Q1 K0: Q3 + Q2 . Q1 Mediante el uso del simulador descubrimos que la función que representa a J0 y K0 se mantenía en 1 para todos los estados del circuito, lo cual puede comprobarse también mediante los mapas de Karnaugh Los circuitos digitales SÍNCRONOS son más fáciles de diseñar y reparar, debido a que los cambios de las salidas son eventos "esperados" (ya que fácilmente podemos saber el estado de cada una de las entradas o salidas sin que estas cambien repentinamente), y los cambios dependen del control de una sola señal aplicada a todos los registros, la señal de RELOJ. La señal de reloj es una onda cuadrada o rectangular, los registros que funcionan con esta señal, sólo pueden cambiar cuando la señal de reloj hace una transición Circuito Eléctrico Aquí mostramos una imagen de la implementación de las funciones lógicas en un circuito real: Circuito Topológico Aquí se mostrará la implementación del circuito en “MultiSim” y se podrá ver que las funciones lógicas obtenidas mediantes los Mapas de Karnaugh, son correctas. Multivibrador astable (clock) Frecuencia deseada 𝑓 ≈ 200𝑚𝐻𝑧 Ciclo de trabajo: 66% 𝑓= 1.443 (𝑅1 + 2𝑅2 ) 𝐶 𝐷 = 0.66 = 𝑅1 + 𝑅2 𝑅1 + 2𝑅2 Luego 𝑅1 = 𝑅2 = 22𝑘Ω 𝐶 = 100𝜇𝐹 Circuito RC para resetear entradas R = 1𝑀Ω C = 10𝑛F τ = 10𝑚𝑠 La corriente máxima del circuito será: imax (t = 0) = 15μA Descripción de la experiencia A través de la tabla de transiciones del FF JK pudimos realizar la Tabla de Verdad y los Mapas de Karnaugh. Luego de esto, obtuvimos las funciones lógicas, donde pudimos nuevamente simplificar las expresiones para utilizar menos circuitos integrados. Una vez resuelto esto, procedemos a trasladar las funciones lógicas a un simulador mediante la aplicación de las compuertas. Para asegurar que el circuito no arranque en una combinación no deseada (para la que no está definida la tabla de verdad) implementamos un circuito RC, que envié un 1 lógico al terminal de clear de cada FF, de manera tal que el circuito siempre empiece a contar desde el 0. Para los pulsos de reloj implementamos una configuración en modo astable del CI NE555. Esta configuración emite una onda cuadrada cuya frecuencia quedará definida por los valores de resistencia y capacidad usados. Nosotros elegimos una frecuencia de aprox. 218 mHz, de manera que la cuenta se realice lentamente. Lista de materiales 2 Protoboard (tamaño mediano) 2 Circuitos integrados (4081) AND tecnología cmos 2 Flip Flop JK (4027) tecnología cmos. 1 decodificador 7 segmentos cátodo común (4511) Cables conectores de varios colores Fuente de alimentación de 15v 7 Resistencias de 1KΩ, 1 Resistencia de 1MΩ, 2 resistencias de 22KΩ 1 Capacitor de 100μF, 1 capacitor de 1nF, a capacitor de 10nF 1 Display 7 segmentos Multímetro, Pinzas, Llaves, etc.