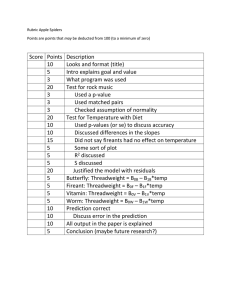

12_chapter 3

Chaptei-3

Chapter..., 3 Hardware & Software details of FPGA Based Design

Hardware & Software details of

FPGA Based Temperature Measurement and Control System

3.1 Introduction

The first step in developing a new instrument is to define very carefully what we want the instrument to do. The next step is to decide which part of the instrument to be in hardware and which part to be in software. The best way to develop the hardware is to use minimum number of components within small portions, which can be individually tested and debugged. FPGA based Temperature Measurement and Control System is developed in the present work, the details of which are given in the following sections.

FPGA based systems [1] are widely used in industry for the measurement, display and monitoring of physical quantities like temperature, pressure, speed, flow, etc., for the measurement of such quantities, transducers or sensors are used to convert real-life information into equivalent electrical signals. For example, the temperature sensors convert the physical data such as temperature into an equivalent electrical signal. The output of the sensor is a signal whose voltage level is proportional to the temperature.

3.2 Hardware Details

The block diagram of FPGA based temperature monitoring system is illustrated in

Fig.3.1. This consists of PtlOO, Water bath with motorized stirrer, Signal

Conditioning Circuit, Analog to Digital Converter (AD574), Variac of range 0-260V,

Electromechanical Relay, FPGA, Flash PROM, JTAG and LCD unit.

52

Chapter.... 3 Hardware & Software details of FPGA Based Design

Fig.3.1 Block diagram of FPGA Based Temperature Measurement and Control System

A

The target FPGA device used in the present work is Spartan-3 family

XC3S400 manufactured by Xilinx. Design development and debugging are carried on a low-cost, full-featured kit provided by Applied Digital Microsystems (ADM) Pvt.,

Ltd., Mumbai. This board provides all the tools required to quickly begin design and verifying Spartan-3 platform designs. Designs are based on 10 MHz clock. The following sections describe the complete design and development of hardware & software aspects of FPGA based temperature monitoring system. The Schematic of

FPGA based temperature measurement and control system is shown in Fig.3.2.

53

Chapter,... 3 Hardware & Software details of FPGA Based Design

Fig.3.2 Schematic of FPGA based Temperature Measurement and Control System

3.2.1 Resistance Temperature Detector - PtlOO

The RTD is a temperature sensing device whose resistance increases with temperature

[2]. RTD works on the principle that, the electrical resistance of metals changes with temperature. The change in electrical resistance vs. temperature for a material is termed as the "temperature coefficient of resistance" for that material. The temperature coefficient for most metals is positive, and for many pure metals is essentially constant over a large portion of the useful temperature range. Moreover, a resistance thermometer is the most stable, accurate, and linear device available for temperature measurement. The resistivity of metal used in an RTD (including platinum, copper, and nickel) depends on the range of temperature measurements desired. The nominal resistance of a PtlOO is 100Q at 0°C. Though PtlOOs are highly standardized, they conform to multiple standards that are not identical world wide.

Therefore, problems arise when a PtlOO built to one standard is used with an

54

Chapter,... 3 Hardware & Software details of FPGA Based Design instrument designed to a different standard [3]. The common standards for PtlOOs are shown in Table 3.1. Platinum's long-term stability, repeatability, fast response time and wide temperature range make it a useful choice in many applications. As a result,

PtlOOs are recognized as the most reliable standard available for temperature measurement.

Organization

Table 3.1 Common Standards for PtlOOs

Standard ALPHA («): Average temperature coefficient of resistance (/°C)

0.003850

Nominal resistance at

0°C (ft)

100 British Standard

Deutschen Institut fur Normung

International

Electrotechnical

Commission

Scientific Apparatus

Manufacturers of

America

Japanese Standard

American Society for Testing and

Materials

BS 1904: 1984

DIN 43760:1980

IEC751:1995

(Amend. 2)

SAMA RC-4-1966

JIS C1604-1981

ASTME1137

0.003850

0.00385055

0.003923

0.003916

0.00385055

100

100

98.129

100

100

Theoretically speaking any kind of metal can be used as a temperature sensor.

But in practice, metals with high melting points can withstand the effect of corrosion, and those with high resistivities are chosen. Copper has low resistivity but is sometimes used because of its low cost. The most commonly used RTDs are made of nickel, platinum, or nickel alloys. Nickel sensors are used in cost sensitive applications, such as consumer goods and they have a limited temperature range.

55

Chapter,.,. 3 Hardware & Software details of FPGA Based Design

Platinum is the most common RTD material, mainly because of its high resistivity and long term stability as mentioned in Table 3.2. Wire wound RTD element is used in the present work and it is as shown in Fig.3,3,

Table 3.2 Resistivities of Some RTD metals

Metal

Silver

Resistivity

(ohm/cmf)

8.8

Copper

Gold

Tungsten

Nickel

Platinum

9.26

13.00

30.00

36.00

59.00

cmf = circular mil foot

The PtlOO is described by the following generic equation, which makes obvious a nonlinear relationship between temperature and resistance

Rr = Ro (1 + AT + BT2+C(T-100)T3) where:

A = 3.9083 E-3

B = -5.775 E-7

C = -4.183 E-12 below 0°C, and zero above 0°C.

Where ‘T’ is the temperature of the platinum element in °C, R t is the temperature dependent electrical resistance and Ro is nominal value i.e., electrical resistance at

0°C.

56

Chapter.... 3 Hardware & Software details of FPGA Based Design

3.2.2 Water bath with motorized stirrer

The Photograph of the water bath with motorized stirrer is shown in Fig 3.4. The water bath contains a vessel with water, Stirrer and a heating element. The vessel is kept in a wooden box and the top is also closed with insulating cap. A small ‘L’ shaped steel rod is attached to the DC motor shaft, which acts as stirrer. The DC motor is fixed on the top of the wooden box. Here the stirrer is used for getting uniform temperature in the water bath. The PtlOO sensor and probes of the digital thermometer are also dipped in the water bath through the holes beside the DC motor on the top of the wooden box. When power is ON, DC motor gets energized to rotate along with, the stirrer is also rotated to get the uniform temperature throughout the experiment.

57

Chapter.... 3 Hardware & Software details of FPGA Based Design

3.2.3 Signal Conditioning Circuit

The signal conditioning circuit developed in the present work for temperature sensor

(PtlOO) is designed using Low Power Quad Operational Amplifier LM324. LM324 works with TTL level voltages (i.e., 0 - 5V). In signal conditioning circuit, the compensation for non-linearity is accomplished using the feedback resistor R2 that provides small amount of positive feedback. The signal conditioning circuit gives the analog voltage, which is proportional to the temperature. The output of the signal conditioning circuit is fed to the ADC (AD574), since FPGA can process only digital data [4], Hence the output voltage of PtlOO is signal conditioned and linearised using the circuit shown in Fig.3.5.

58

Chapter.... 3 Hardware & Software details of FPGA Based Design

Fig.3.5 Signal Conditioning

The resistances vs. temperature characteristics of PtlOO are stable, reproducible and have a linear positive temperature coefficient from -200°C to

+850°C as shown in Fig.3.6.

TEMPERATURE («C)

Fia.3.6 Temnerature and Resistance Characteristics of PtlOO

59

Chapter..,. 3 Hardware & Software details of FPGA Based Design

3.2.4 Analog-to-Digital Converter

Most of the physical quantities vary continuously, which is the characteristic of the analog world. Such a continuously varying quantity has to be invariably quantized in to digital format. This process calls for a module that converts the analog quantity in to its equivalent digital value. This is accomplished using analog-to-digital converter

(ADC). An ADC [5] is an important circuit building block in a mixed signal control system. In applications such as radar systems, digital telephony, process instrumentation etc., ADC is a small part of the whole system. Therefore, it should be simple and small in size. Other pre-requisites are low-power consumption and best speed performance. Further, ADCs play an important role in data acquisition systems.

There are different types of ADCs available in the market. They differ from each other basing on the bit length, conversion time and conversion technique.

The ADC used in the present work is AD574, which works on the principle of

“successive-approximation technique”. The AD574 is a complete 12-bit successive- approximation analog to digital converter [6]. A high precision voltage reference and clock are included on-chip, and the circuit gives full rated performance without external circuitry or lock signals. The Pin Diagram of AD574 ADC is shown in

Fig.3.7.

3.2.4.1 Features of AD574 ADC

1. The AD574 interfaces to most 8- or 16-bit microprocessors. Multiple-mode three-state output buffers connect directly to the data bus while the read and convert commands are taken from the control bus. The 12-bits of output data can be read either as one 12-bit word or as two 8-bit bytes (one with 8 data bits, the other with 4 data bits and 4 trailing zeros).

60

Chapter..., 3 Hardware & Software details of FPGA Based Design

2. The precision, laser-trimmed scaling and bipolar offset resistors provide four calibrated ranges: 0 volts to +10 volts and 0 volts to +20 volts unipolar; -5 volts to +5 volts and -10 volts to +10 volts bipolar. Typical bipolar offset and full-scale calibration errors of ±0.1 % can be trimmed to zero with one external component each. The internal buried Zener reference is trimmed to 10.00 volts with 0.2% maximum error and 15 ppm/°C typical T.C. The reference is available externally and can drive up to 1.5 mA beyond the requirements of the reference and bipolar offset resistors.

+SV SUPPLY

DATA MOOB SELECT m

C«K> SELECT cs

SHORT CYCLE

As?

READ-CONVERT nic. '■

CHIP ENABLE

CE

+t2F»19V SUPPLY

V«* reference

REF OUT

j

AH ALOS COMMON !

AC i

REFERENCE INPUT 1

REFIN I

-12M5V SUPPLY 1

Vi* I

BIPOLAR OFFSET I

BP OFF I wspah input

i

10V„ |

2CVSPAN INPUT 1

SOVw I

TZ7"

CONTROL

5AR

12 c N vmi

TEZ

A0574A i m ____ use

N

STATUS

I STS

I OS«1\

I MSB

0810

12

3

5

T

A

T

E

B a i.

E

A

N -

0 u

T p

8 e

U

L

E

T a

082

[ 837.

DIGITAL

DATA

OUTPUTS

R u

F p

N r

8

E

B n L

&

E

C

CSS

.

**|

MM oat

JC“ tar

I OOITAI. COMMON

I DC

Fig.3.7 Pin Diagram of AD574 Analog to Digital Converter

3.2.4.2 ADC interface connection details

Supply decoupling and layout considerations

It is critically important that the AD574 power supplies be filtered, well regulated, and free from high frequency noise. Use of noisy supplies will cause unstable output codes. Switching power supplies are not recommended for circuits attempting to

61

Chapter.... 3 Hardware & Software details of FPGA Based Design achieve 12-bit accuracy unless great care is used in filtering any switching spikes present in the output. A few millivolts of noise represent several counts of error in a

12-bit ADC. Decoupling capacitors should be used on all power supply pins; the +5V supply decoupling capacitor should be connected directly between Pin 1 and Pin 15

(digital common) and the +Vcc and -V ee pins should be decoupled directly to analog common (Pin 9). Circuit layout should attempt to locate the AD574, associated analog input circuitry, and interconnections as far as possible from logic circuitry. For this reason, the use of wire-wrap circuit construction is not recommended. Careful printed circuit construction is preferred.

Grounding considerations

The analog common at Pin 9 is the ground reference point for the internal reference and is thus the “high quality” ground for the AD574; it should be connected directly to the analog reference point of the system. In order to achieve all of the high accuracy performance available from the AD574 in an environment of high digital noise content, the analog and digital commons should be connected together at the package. In some situations, the digital common at Pin 15 can be connected to the most convenient ground reference point; analog power return is preferred.

Unipolar range connections for the AD574

The AD574 contains all the active components required to perform a complete 12-bit

A/D conversion. Thus, for most situations, all that is necessary is connection of the power supplies (+5V, +12V/+15V and -12V/-15V), the analog input, and the conversion initiation command. Analog input connections and calibration are easily accomplished; the unipolar operating mode is shown in Fig.3.8. All of the thin-film

62

Chapter.... 3 Hardware & Software details of FPGA Based Design application resistors of the AD574 are trimmed for absolute calibration. Therefore, in many applications, ho calibration trimming will be required. If the offset trim is not required, Pin 12 can be connected directly to Pin 9; the two resistors and trimmer for

Pin 12 are then not needed. If the full-scale trim is not needed, a 50 W + 1% metal film resistor should be connected between Pin 8 and Pin 10. The analog input is connected between Pin 13 and Pin 9 for a 0V to +10V input range, between 14 and

Pin 9 for a 0V to +20V input range. The AD574 easily accommodates an input signal beyond the supplies. For the 10V span input, the LSB has a nominal value of 2.44 mV.

Unipolar calibration

The AD574 is intended to have a nominal 1/2 LSB offset so that the exact analog input for a given code will be in the middle of that code (halfway between the transitions to the codes above and below it). Thus, the first transition (from 0000 0000

0000 to 0000 0000 0001) will occur for an input level of+1/2 LSB (1.22 mV for 10 V range). If Pin 12 is connected to Pin 9, the unit will behave in this manner, within specifications. If the offset trim (Rl) is used, it should be trimmed as above, although a different offset can be set for a particular system requirement. This circuit will give approximately ±15 mV of offset trim range. The full-scale trim is done by applying a signal 1 Vi LSB below the nominal full scale (9.9963V for a 10V range). Trim R2 to give the last transition (1111 1111 1110 to 1111 1111 1111). Unipolar input connections are shown in Fig.3.8.

63

Chapter.... 3 Hardware & Software details of FPGA Based Design

Fig.3.8 Unipolar input Connections

Stand-alone operation

The AD574 can be used in a “stand-alone” mode, which is useful in systems with dedicated input ports available and thus not requiring full bus interface capability. In this mode, CE and 12/8 are wired high, CS and Ao are wired low, and conversion is controlled by R/C. The three-state buffers are enabled when R/C is high and a conversion starts when R/C goes low. This allows two possible control signals - a high pulse or a low pulse. Operation with a low pulse is shown in Fig.3.9. In this case, the outputs are forced into the high impedance state in response to the falling edge of

R/C and return to valid logic levels after the conversion cycle is completed. The STS i line goes high 600 ns after R/C goes low and returns low 300 ns after data is valid. If conversion is initiated by a high pulse as shown in Fig.3.10, the data lines are enabled during the time when R/C is high. The falling edge R/C of starts the next conversion, and the datalines return to three-state (and remain three-state) until the next high pulse of R/C. Operation with high pulse as shown in Fig.3.10 is used for the present work.

64

Chapter,,., 3 Hardware & Software details of FPGA Based Design

«*

STS

£—-------

"A.

HX3HJ

\

MMVjtUO

Fig.3,9 Low Pulse for R/C - Outputs Enabled After Conversion

Fig.3.10 High Pulse for R/C - Outputs Enabled while R/C High, Other HBgh-Z

General A/D converter interface Considerations

A typical A/D converter interface routine involves several operations. First, a write to the ADC address initiates a conversion. The FPGA must then wait for the conversion cycle to complete, since most ADCs take longer than one instruction cycle to complete a conversion. Valid data can, of course, only be read after the conversion is complete. The AD574 provides an output signal (STS) which indicates when a conversion is in progress. This signal can be polled by the FPGA by reading it through an external three-state buffer (or other input port). The STS signal can also be used to generate an interrupt upon completion of conversion, if the system timing requirements are critical (bear in mind that the maximum conversion time of the

AD574 is only 35 microseconds) and FPGA has other tasks to perform during the

65

Chapter,.,. 3 Hardware & Software details of FPGA Based Design

ADC conversion cycle. Another possible time-out method is to assume that the ADC will take 35 microseconds to convert, and insert a sufficient number of “do-nothing” instructions to ensure that 35 microseconds of FPGA time is consumed. Once it is established that the conversion is finished, the data can be read. In the case of an ADC of 8-bit resolution (or less), a single data read operation is sufficient. In the case of converters with more data bits than are available on the bus, a choice of data formats is required, and multiple read operations are needed. The AD574 includes internal logic to permit direct interface to 8-bit or 16-bit data buses, selected by connection of the 12/8 input. In 16-bit bus applications (12/8 high) the data lines (DB11 through

DBO) may be connected to either the 12 most significant or 12 least significant bits of the data bus. The remaining four bits should be masked in software. The interface to an 8-bit data bus (12/8 low) is done in a left-justified format. The even address (Ao low) contains the 8 MSBs (DB11 through DB4). The odd address (Ao high) contains the 4 LSBs (DB3 through DBO) in the upper half of the byte, followed by four trailing zeroes, thus eliminating bit masking instructions.lt is not possible to rearrange the

AD574 data lines for right justified 8-bit bus interface. Truth table of the AD574 is shown in Table 3.3. The interfacing diagram of AD574 and signal conditioning circuit with FPGA is shown in Fig.3.11.

Control Logic

The AD574 contains on-chip logic to provide conversion initiation and data read operations from signals commonly available in microprocessor systems. The control signals CE, CS and R/C control the operation of the converter. The state of R/C when

CE and CS are both asserted determines whether a data read (R/C= 1) or a convert

(R/C= 0) is in progress. The register control inputs Ao and 12/8 control conversion length and data format. The A0 line is usually tied to the least significant bit of the

66

Chapter.... 3 Hardware & Software details of FPGA Based Design address bus. If a conversion is started with A0 low, a full 12-bit conversion cycle is initiated. If A0 is high during a convert start, a shorter 8-bit conversion cycle results.

During data read operations, A0 determines whether the three-state buffers containing the 8 MSBs of the conversion result (A0 = 0) or the 4 LSBs (Ac = 1) are enabled. The

12/8 pin determines whether the output data is to be organized as two 8-bit words

(12/8 tied to DIGITAL COMMON) or a single 12-bit word (12/8 tied to VLOGIC).

The 12/8 pin is not TTL-compatible and must be hard-wired to either VLOGIC or

DIGITAL COMMON. In the 8-bit mode, the byte addressed when A0 is high contains the 4 LSBs from the conversion followed by four trailing zeroes. This organization allows the data lines to be overlapped for direct interface to 8-bit buses without the need for external three-state buffers. It is not recommended that A0 change state during a data read operation. Asymmetrical enable and disable times of the three-state buffers could cause internal bus contention resulting in potential damage to the

AD574. An output signal, STS, indicates the status of the converter. STS goes high at the beginning of a conversion and returns low when the conversion cycle is complete.

Photograph of the signal conditiong circuit and ADC Unit is shown in Fig.3.12.

Photograph of the Signal conditioning circuit, ADC and Relay Unit is shown in

Fig.3.13.

67

Chapter.... 3 Hardware & Software details of FPGA Based Design

0

1

1

1

X

1

1

CE

0

0

0

0

0

1

Table 3.3 AD574 Truth Table

12/8 Ao

X cs Rye

X X X None

None X

0

0

X

X

X

0

X 1

Pin 1 X

1

1

1

Pin 15 0

Pin 15 1

Operation

Initiate 12-Bit Conversion

Initiate 8-Bit Conversion

Enable 12-Bit Parallel Output

8 Most Significant Bits

4 LSBs + 4 Trailing Zeroes

Fig.3.11 Interfacing diagram of AD574 & Signal Conditioing Circuit with FPGA

68

Chapter.... 3 Hardware & Software details of FPGA Based Design

Fig.3.12 Photograph of Signal Conditioning circuit & ADC Unit

Fig.3.I3 Photograph of the Signal conditioning circuit, ADC and Relay Unit

69

Chapter..., 3 Hardware & Software details of FPGA Based Design

3.2.5 Electromechanical Relay Interfacing Circuit

3.2.5.1 Electromechanical Relay Contact Types

Electromechanical relays [7] are made up of one or more individual switch contacts with each "contact" being referred to as a "pole". Each one of these contacts or poles can be connected or "thrown" together by energizing the relay’s coil and this gives rise to the description of the contact types as being

SPST - Single Pole Single Throw

SPDT - Single Pole Double Throw

DPST - Double Pole Single Throw

DPDT - Double Pole Double Throw with the action of the contacts being described as "Make" (M) or "Break" (B). Then a simple relay with one set of contacts can have a contact description of: "Single Pole

Double Throw - (Break before Make)", or SPDT - (B-M). Examples of some of the more common contact types for relays are shown in Fig. 3.14, but there are many more possible configurations. The SPDT (B-M) contact type relay is used for the present work.

Fig.3.14 Common contact type of Relays

70

Chapter.,.. 3 Hardware & Software details of FPGA Based Design

3.2.S.2 Relay Contact Configurations

It is not advisable to connect relay contacts in parallel to handle higher load currents.

For example, never attempt to supply a 10A load with two relays in parallel that have

5A contact ratings each as the relay contacts never close or open at exactly the same instant of time, so one relay contact is always overloaded. While relays can be used to allow low power or computer type circuits to switch a relatively high currents or voltages both "ON" or "OFF". Never mix different load voltages through adjacent contacts within the same relay such as for example, high voltage AC (240V) and low voltage DC (12V), always use separate relays.

One of the more important parts of any relay is the coil. This converts electrical current into an electromagnetic flux which is used to operate the relays contacts. The main problem with relay coils is that they are "highly inductive loads" as they are made from coils of wire. Any coil of wire has an impedance value made up of resistance (R) and inductance (L) in series (RL Series Circuit). As the current flows through the coil a self induced magnetic field is generated around it. When the current in the coil is turned "OFF", a large back emf (electromotive force) is produced as the magnetic flux collapses within the coil (transformer theory). This induced reverse voltage value may be very high in comparison to the switching voltage, and may damage any semiconductor device such as a transistor, FET or FPGA used to operate the relay coil.

One way of preventing damage to the transistor or any switching semiconductor device, is to connect a reverse biased diode across the relay coil. When the current flowing through the coil is switched "OFF", an induced back emf is generated as the magnetic flux collapses in the coil. This reverse voltage forward biases the diode which conducts and dissipates the stored energy preventing any

71

Chapter.... 3 Hardware & Software details of FPGA Based Design damage to the semiconductor device. When used in this type of application the diode is generally known as a power diode. Other types of inductive loads which require a power diode for protection are solenoids, motors and inductive coils.

3.2.S.3 Interfacing Electromechanical Relay with Spartan-3 FPGA

To change the positin of relay contact, a constant voltage should be applied across the relay coil. NPN transistor SL100 is used to control the relay with 12V coil, operating from +12V supply as shown in Fig.3.15. A Series base resistor R2 is used to set the base current for SL100, so that the transistor is driven into saturation when the relay is to be energised. That way, the transistor will have minimal voltage drop, and hence delivering most of the 12V to the relay coil. Initially when the coil is not energized, there will be a connection between the common terminal and normally closed (NC) pin. But when the coil is energized, this connection breaks and a new connection between the common terminal and normally open (NO) pin will be established. If signal from FPGA to the relay is HIGH, then the relay is switched to NO position. On the other hand signal from FPGA to the relay is LOW, then the relay is switched to

72

Chapter.... 3 Hardware & Software details of FPGA Based Design

A diode (IN4007) is connected across the relay coil, to protect the transistor from damage due to the back emf pulse generated in the relay coil’s inductance, when

SL100 turns off. That is, when the voltage is removed from the coil, it needs some path to discharge the stored energy in it. So the diode (IN4007) creates that path untill the coil discharges [8].

3.2.6 Spartan-3 FPGA Details

The key manufacturers of FPGAs are Xilinx, Altera, Lattice and Actel. Fig.3.16 shows the FPGA market share [9]. Xilinix was founded in 1984 and shipped its first commercial product in 1985. Xilinx offers its Vertex family at the high end and

Spartan family at the low end. The Spartan-3 family of FPGAs is specifically designed to meet the needs of high volume, cost-sensitive consumer electronic applications. The eight-member family offers densities ranging from 50,000 to five million system gates. Table 3.4 describes the summary of Spartan-3 FPGA Attributes.

Because of their exceptionally low cost, Spartan-3 FPGAs are ideally suited to a wide range of consumer electronics applications; including broadband access, home networking, display/projection and digital television equipment.

Xilinx

Actel

Altera

Fig.3.16 FPGA market share

Lattice

73

Chapter.... 3 Hardware & Software details of FPGA Based Design

Device

System

'Gates-.

Table 3.4 Summary of Spartan-3 FPGA attributes

Eqaivale

■1 Logic

Cells

(OeeCLG=Fo«rSbces)

Dfetribei erf RAM

Bits

<K=1024)

Block

SIAM

Bits

(K-I024)

Dedic ated

Malti pliers

DC

Ms'

Maxia

User

WO

Maxim*

DHknsik:

1 WO Pairs

XC3S50 50K 1,728

Rows eolmn n

Total

CLB s

16 12 192 12k

XC3S200 200K 4,320

XC3S400 400K 8,064

24

32

20

28

480

896

30K

56K

72k

216K

4

2 124 56 li 4 173 76

2S8K.

16 A 264

XC3SIOO0 1M 17,280 48

XC3S1500 1.5M

29,952 64 . 52 3^28 208K 576K 32 4 487

64 5,120 320K 720K 40 4 565 XC3S2000 2M 46,080 80

XC3S4000 4M 62,208 96 72 6^12 432K 1,728K 9*5 4 633

XC3S5000 5M 74,880 104

40 1,920 120K 432K 24 4 391

80 8320 520K 1,872K 104 4 633

175

221

270

300

300

The Spartan-3 family [10] is a superior alternative to mask programmed

ASICs. FPGAs avoid the high initial cost, the lengthy development cycles, and the inherent inflexibility of conventional ASICs. Also, FPGA programmability permits design upgrades in the field with no hardware replacement necessary, an impossibility with ASICs. Spartan-3 was first announced in April 2003. Spartan-3 family is based on a 90nm, eight layer metal process, with densities up to 74K logic cells (LCs) and up to 1,8 Mbits of embedded RAM, with dedicated 18x18 multipliers, up to 4 digital clock managers (DCMs), and high-speed, versatile external RAM interface. Spartan-3 devices support differential and single-ended VO standards. Spartan-3 family packaging information is shown in Fig.3.17.

74

Chapter,... 3 Hardware & Software details of FPGA Based Design

The Specifications of Spartan-3 FPGA are as follows

<=> Low-cost, high-performance logic solution for high-volume, consumer-oriented applications

• Densities up to 74,880 logic cells

O Select 10 interface signaling

• Up to 633 I/O pins

• 622+ Mb/s data transfer rate per I/O

•18 single-ended signal standards

• 8 differential I/O standards including LVDS, RSDS

• Termination by Digitally Controlled Impedance

• Signal swing ranging from 1.14V to 3.465V

• Double Data Rate (DDR) support

• DDR, DDR2 SDRAM support up to 333 Mbps

<4> Logic resources

• Abundant logic cells with shift register capability

• Wide, fast multiplexers

• Fast look-ahead carry logic

• Dedicated 18x18 multipliers

• JTAG logic compatible with IEEE 1149.1/1532

^ Select RAM hierarchical memory

• Up to 1,872 Kbits of total block RAM

• Up to 520 Kbits of total distributed RAM

"4> Digital Clock Manager (up to four DCMs)

• Clock skew elimination

• Frequency synthesis

75

Chapter..,. 3 Hardware & Software details of FPGA Based Design

• High resolution phase shifting

Eight global clock lines and abundant routing

■=> Fully supported by Xilinx ISE and WebPACK software development systems

MicroBlaze’and PicoBlaze processor, PCI, PCI Express PIPE Endpoint and other

IP cores

^ Pb-free packaging options

^ Automotive Spartan-3 XA Family variant.

MaskRevisionCode

FabricatianGode

Process Technology

Data Code

Lot Code

Fig.3.17 Spartan-3 family packing information

XC3S4O0 -4 PQ 208C

Device type

Speed Grade

L> Temperature Range

.£•= Commercial (T, =0oCto85oC) f = Industrial (Tj = -40oCto IGOoC)

Package Type NumberofPins

3.2,7 FPGA Base Board

The ADM Base Board is a powerful tool that allows user to understand the capabilities of FPGA. This board acts as a universal FPGA/CPLD/pP reconfigurable implementation platform to allow rapid and interactive prototype development [10],

76

Chapter.... 3 Hardware & Software details of FPGA Based Design

The board houses a plug-in daughter board containing a target FPGA/CPLD/pP device. Daughter boards can be easily swapped to provide support for multi-vendor devices available in DIL. PLCC, TQFP. PQFP packages up to 240 pins. Fig.3.18 shows the photograph of the FPGA base board used for the present work.

Fig.3.18 Photograph of the FPGA base board used for the present work

The Specifications of base board are as follows

* 16x2 Alpha-numeric LCD display with the backlight

* Four digit 7-segment display

4= Eight general purpose LEDs

77

Chapter,... 3 Hardware & Software details of FPGA Based Design

* Three LEDs to indicate the various power voltages

* 4x4 Matrix KeyPad

* 208 I/O pins

* All I/O with VCC/GND links.

* On board 10 MHz oscillator

* 10MHz clock and four different frequecny clocks (5MHz, 1MHz, 500 KHz, lOQKHz)

* Support’s 1.8V to 5V devices

* Vendor Specific Gate density

* JTAG Programming cable

* Paral 1 el/S eri al/US B/S PI/CAN

* PS2 Mouse & Keyboard I/F

* I2C EEPROM &.RTC

* Serial ADC/D AC with Pot

* Electromechanical Relay of DCS V

* RS232 serial interface through 9-PIN D type connector

^ Four sets of 30x2 male berg connectors to plug the Daughter board

3.2.8 Daughter Board

In the present application, daughter board contains Spartan-3 FPGA (XC3S400) from

Xilinx, which can be plugged on to the base board [11]. The Spartan-3 FPGA uses

SRAM technology. Spartan-3 devices support serial configurations, using the master/slave serial and JTAG modes, as well as byte-wide configuration employing the slave parallel mode. Fig.3.19 shows the photograph of Spartan-3 XC3S400

Daughter board used for the present work.

78

Chapter.... 3 Hardware & Software details of FPGA Based Design

Daughter board includes the following items

• Xilinx FPGA Spartan-3 (XC3S400)

• Platform Flash PROM (XCF02)

• Ten 10- pin Pleaders, intended for use as a GPIO

• Four sets of 20x2 female berg connector for plugging on to the base board

• Mode selection jumpers

• JTAG pins for in circuit programming

• Power supply 3.3V, 2.5V and 1,2V are provided from the base board

Fig.3.19 Photograph of Spartan-3 XC3S400 Daughter board

79

Chapter.... 3

Device System

Gates

Hardware & Software details of FPGA Based Design

XC3S400 Device Features

Equivalent

Logic Cells

CLB Array (One CLB= Four

Slices)

Rows Columns Total CLBs

XC3S400 400K 8,064 32 28 896

Distributed

RAM Bits

Block

RAM

Bits

Dedicated

Multipliers DCMs

Maximum

User I/O

Maximum

Differential

I/O Pairs

56K 288K 16 4 141 62

3.2.9 XCF02 (Platform Flash PROM)

Xilinx introduces the Platform Flash series of in-system programmable configuration

PROMs available in 1 to 32 Mb densities [12]. The XCFxxS version includes 4Mb,

2Mb and 1Mb PROMs that support Master Serial and Slave Serial FPGA configuration modes. The Platform Flash PROM family provides non-volatile storage, easy-to-use, cost-effective, as well as an integrated bitstream delivery mechanism for use with target FPGAs. For the present work, XCF02S is chosen since it possesses the following salient features

* The Platform Flash PROM XCF02S (2Mb) was developed using a low- power, advanced CMOS NOR FLASH process

* Operates over the full industrial temperature range (-40°C to +85°C).

* Endurance of 20,000 Program/Erase Cycles

* IEEE Standard 1149.1/1532 Boundary-Scan (JTAG) Support for

Programming, Prototyping and Testing

80

Chapter.... 3 Hardware & Software details of FPGA Based Design

* JTAG Command Initiation of Standard FPGA Configuration

* Cascadable for Storing Longer or Multiple Bitstreams

* Dedicated Boundary-Scan (JTAG) I/O Power Supply (VCCJ)

* I/O Pins Compatible with Voltage Levels Ranging From 1.5V to 3.3 V

* Design Support Using the Xilinx ISE Alliance and Foundation Software

Packages

* Serial FPGA configuration interface

* V020 package

* Convenient built-in power-up sequencing for FPGA data integrity

An overview of control, data output, clock, and JTAG signals for these PROMs are shown in Fig.3.20.

•CUE’ CE • j£.

TC&-

TDI

TOO'.

-9»

CeriScfand

4-^J.ijWr.

littedaw

"iJ'iti-

.«!------

Address

-S'

Msnerr au

X

* liaelfafe

3DATA(DO)

""serial Mode

■CE

Fig.3.20 Platform Flash PROMs Block diagram

81

Chapter,.., 3 Hardware & Software details of FPGA Based Design

3.2.10 Downloading Tool

Downloading tools are used to program the FPGA [12]. These tools connect to JTAG port or Serial port of the daughter board on one end and to PC parallel port on the other end. It drives power from the target-daughter board. Fig.3.21 shows the downloading tool connection diagram.

JTAG able PC Parallel Ca'de

Fig.3.21 Downloading tool connection diagram

3.2.11 Download Cables

There are three cables available for use with the JTAG Programmer. The first is an

RS232 serial cable known as the XChecker Cable. The second is the Parallel

Download Cable which can be connected to a PC’s parallel printer port [13]. The third is the Multilinx cable which can be connected to a USB port (Windows 98 only) or serial port. There are a few advantages to be considered in selecting a cable

• The XChecker Cable or Multilinx Cable connects to the serial port of both work stations and PCs.

• The parallel download cable has better drive capability. The parallel download cable can drive up to 10 devices in a boundary-scan chain, and the XChecker cable can drive up to 4 devices.

• The parallel download cable is at least 5 times faster. In the present work parallel download cable is used.

82

Chapter.... 3 Hardware & Software details of FPGA Based Design

Parallel Download Cable

The parallel download cable consists of a cable assembly containing logic to protect the PC‘s parallel port and a set of headers to connect to the target system. Using the parallel download cable [13] requires a PC equipped with an AT compatible parallel port interface with a DB25 standard printer connector. Fig.3.22 shows the parallel download cable and its accessories. The cable assembly contains logic designed to electrically isolate the target system from the parallel port of PC. The parallel download cable can be used with a single FPGA or several ICs connected in a boundary-scan chain to download and readback configuration and boundary-scan data. The transmission speed of the parallel download cable is determined solely by the speed at which the host PC can transmit data through its parallel port interface.

83

Chapter.... 3 Hardware & Software details of FPGA Based Design

3.2.12 Joint Test Action Group (JTAG)

The Boundary Scan Register and other test features of the device are accessed through a standard interface - the JTAG Test Access Port (TAP). Typical JTAG [14] device architecture is shown in Fig.3.23. According to the standard, the TAP must contain four signals, each available through a dedicated device pin and they may not be shared with any other function:

* Test Data Input (TDI): It is used to shift data and instruction tests into the

Boundary Scan register.

* Test Data Output (TDO): This pin provides data from the Boundary Scan register or other internal register.

* Test Clock (TCK): This input controls test-logic timing independent of clocks that normal system operations employ. The TDI shifts values into the appropriate register on the rising edge of TCK. Selected register contents shift out onto TDO during the TCK's falling edge.

* Test-Mode Select (TMS): This input, which also clocks through on the rising edge of TCK, determines the state of the TAP controller.

The JTAG port on the Daughter board is used to configure the FPGA and also to program the Platform Flash PROM. Parallel download cable is connected to the board through the JTAG port at one end and other end of the cable (i.e., DB25 Plug

Connector) is connected to PC Parallel port. To work in boundary scan mode, pinl and pin2 of mode selection jumper are shorted.

84

Chapter,... 3 Hardware & Software details of FPGA Based Design

3.23 Typical JTAG Device Architecture

3.3 Software Features

The following section describes the software development for FPGA based temperature measurement and control system using PtlOO in VHDL. The necessary functional modules and state flow diagrams are presented, and thoroughly discussed.

The software tools used for building and testing these modules in the present work is

Xilinx ISE 9.1i. Fig.3.24 shows the State flow diagram for temperature measurement and control system.

85

Chapter,,.. 3 Hardware & Software details of FPGA Based Design

Flow Chart

86

Chapter,.,. 3 Hardware & Software details of FPGA Based Design

Fig.3.24 Flow Chart for Temperature Measurement and Control System

VHDL code for temperature measurement and control System

LIBRARY IEEE;

USE IEEE.STD_LOGIC_ 1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL; entity ad574_relay_lcd is port (adc_data : clklOOk : inout std_logic_vector(l 1 downto 0);

-- 12-bit ADC data in std_logic;

— 100 KHz Clock to the module relay adc_RC :

: out stdjogic;

— Electromechanical relay to control the temperature inout stdjogic;

87

Chapter.... 3

LED lcd_control

Icd„data

:

Hardware & Software details of FPGA Based Design

— Read/ Convert pin of the ADC out std_Jogic_vector (11 downto 0);

— 12 LEDs to display the digital output

:

: out std_logic_vector (2 downto 0);

- control signals for LCD out std_logic_vector (7 downto 0));

- output data to the LCD end ad574_relay_lcd_Ptl00; architecture Behavioral of ad574_relay_led_PtlOO is

---------------------------------------Signal Declaration-----------------------------------

—The below statements are signal declaration for the design to assign the inputs

- and outputs of the modules--------------------------------------------------------------signal clkdiv signal clkstate signal clkkey signal clkrelaysignal clknew signal data signal lcdheader signal Temp

:

:

:

:

:

:

:

: std_logic_vector( 14 downto 0); std_logic_vector(7 downto 0); std_logic; stdjogic; stdjogic; std_logic_vector(7 downto 0); std_logic_vector( 10 downto 0); std_logic_vector(31 downto 0);

----- Beginning of the Architecture for the design-------------------begin

88

Chapter,... 3 Hardware & Software details of FPGA Based Design

--------------------------------------------- Signal assignment-------------------------------------

-The below statements are used for signal assignment of data read from AD574,-----

— Temperature display on LCD and control its value using Relay-------------------------

PI: process (clklGOk, clkdiv) begin if( rising_edge(clkl 00k)) then clkdiv <= clkdiv + 1; end if; clkkey <= clkdiv(13); clknew<= clkdiv(S); elkrelay <= clkdiv(14);

- -1 ‘ end process PI;

..................................................... Signal assignment------------ ------------------------------

—The below statements are used for signal assignment of 8-bit data increment---------

P2: process (clknew, clkstate) begin if( rising__edge(clknew)) then clkstate <= clkstate + 1; end if; data <= clkstate(7 downto 0); end process P2;

-----------------------------------Initialization of AD574 & LED display-------------------

-The below statements are used to send a signal for ADC from FPGA and to display the digital data on 12- LEDs ----------------------------------------------------------------------

89

Chapter.... 3

P3: process (clkkey, adc_RC)

Hardware & Software details of FPGA Based Design begin if rising_edge(clkkey) then adc_RC <= '1 if (adc_RC = T) then

LED <= adc_data; adc_RC <= 'O'; end if; end if; end process P3;

--------------------------------Initilization of LCD and display---------- ---------- ----------

—The below statements are used to initialise the LCD and display the temperature on it---------------- ---------------------- ,----------------------------------------------------------------

P4: process (data,Temp) begin case data is when "00000000" => ledheader <= "10000111000";-438 when "00000001" => ledheader <= "00000111000";-038 when "00000010" => ledheader <= "10000001110”;-40e when "00000011" => ledheader <= "00000001110";-00e when "00000100" => ledheader <= "10000000010";r-402 when "00000101" => ledheader <= "00000000010";-002 when "00000110" => ledheader <= "10000000001 ";-401 when "00000111" => ledheader «= "00000000001";-001

90

Chapter..,. 3 Hardware & Software details of FPGA Based Design when "00001000" => lcdheader <= "10101010100";-554 - T when "00001001" => lcdheader <= "00101010100";~154 when "00001010" => lcdheader <= "10101000101";~545 - E when "00001011" => lcdheader <= "00101000101";-145 when "00001100" => lcdheader <= "10101001101";-54d - M when "00001101" => lcdheader <= "00101001101";-14d when "00001110" => lcdheader <= "10101010000";-550 - P when "00001111" => lcdheader <= "00101010000";-150 when "00010000" => lcdheader <= "10101000101";-545 - E when "00010001" => lcdheader <= "00101000101 ";-145 when "00010010" => lcdheader <= "10101010010";-552 - R when "00010011" => lcdheader <= "00101010010";-152 when "00010100" => lcdheader <= "10101000001";-541 - A when "00010101” => lcdheader <= "00101000001";-141 when "00010110" => lcdheader <= "10101010100";-554 - T when "00010111" => lcdheader <= "00101010100";~154 when "00011000" => lcdheader <= ”10101010101";-555 - U when "00011001" => lcdheader <= "00101010101";~155 when "00011010" => lcdheader <= "10101010010";-552 - R when "00011011"=> lcdheader <= "00101010010";—152 when "00011100" => lcdheader <= "10101000101";-545 - E when "00011101" => lcdheader <= "00101000101";-145 when "00011110" =>.lcdheader <= "10100111010";-43A -: when "00011111" => lcdheader <= "00100111010";-03A when "00100000" => lcdheader "10011000000";~5CO - new line

Chapter.... 3 Hardware & Software details of FPGA Based Design when "00100001" => lcdheader <= "00011000000";~1C0 when "00100010" => lcdheader <= "101"& Temp(31 downto 24);

—100th position when "00100011" => lcdheader <= "001"& Temp(31 downto 24); when "00100100" => lcdheader <= "101 "& Temp(23 downto 16);

—10th position when "00100101" => lcdheader <= ”001 "& Temp(23 downto 16); when "00100110" => lcdheader <= "101 "& Temp(15 downto 8);

— Unit position when "00100111" => lcdheader <= ”001 ”& Temp(15 downto 8); when "00101000" => lcdheader <= "10100101110";— (.) dot display when "00101001" => lcdheader <= ”00100101110"; when "00101010"=>lcdheader <= "101 "& Terap(7 downto 0);

—first decimal position when "00101011" => lcdheader <= "001 "& Temp(7 downto 0); when "00101110" => lcdheader <= "10111011111";— degree when "00101111" => lcdheader <= "00111011111"; when "00110000" => lcdheader <= "10101000011"; - C(centigrade) when "00110001" => lcdheader <= "00101000011"; when others => lcdheader <="11111111111"; end case ; lcd_data <= lcdheader (7 downto 0); led_control <= lcdheader (10 downto 8); r' end process P4;

92

Chapter.... 3 Hardware & Software details of FPGA Based Design

---------------------------------------- Look up table —--------------------------------------

—The below statements compares the adc_data with Look up table and displays the —

----------- temperature value on LCD-------------------------------------------------------------

P5: process (adc_data) begin case adc_data is when "001001100110" => Temp <= X"30303030";--000.0°C when "001001100111 ” => Temp <= X"30303034";~ when "001001101000" => Temp <= X"30303038";~ when "001001101001" => Temp <= X"30303132";~ when "001001101010" => Temp <= X"30303136";~ when "001001101011" =>Temp<= X"30303230";-2.0°C when "001001101100" => Temp <= X"30303234";~ when "001001101101" => Temp <= X"30303238";~ when "001001101110" => Temp <= X"30303332";- when "001001101111" => Temp <= X"30303336";~ when "001001110000" => Temp <= X"30303430";-4.0°C when "001001110001" => Temp <= X"30303434";~ when "001001110010" => Temp <= X"30303438";~ when ”001001110011" => Temp <= X"30303532";~ when "001001110100" => Temp <= X"30303536";- when "001001110101" => Temp <= X"30303630";-6.0°C when "001001110110" => Temp <= X"30303634";- when "001001110111" => Temp <= X"30303638";-

93

Chapter..., 3 Hardware & Software details of FPGA Based Design when "001001111000" =s> Temp <= X"30303732";~ when "001001111001" => Temp <= X"30303736";- when "001001111010" => Temp <= X"30303830";-8.0°C when "001001111011" => Temp <= X"30303834";- when "001001111100" => Temp <= X"30303838";~ when "001001 111 101” =>Temp<= X"30303932";~ when "001001111110" => Temp <= X"30303936";~ when "001001111111" => Temp <= X"30313030";-10.0 °C when "001010000000" => Temp <= X"30313034";~ when ”001010000001" => Temp <= X"30313038";- when "001010000010" =>Temp <= X"30313132";- when "OOlpiOOOOOll" =>Temp <= X"30313136";~ when "001010000100" => Temp <= X”30313230";-12.0°C when "001010000101" => Temp <= X"30313234";- when "001010000110" => Temp <= X"30313238";~ when "001010000111" => Temp <= X"30313332";- when "001010001000" => Temp <= X"30313336”;- when ”001010001001" => Temp <= X"30313430" ;-l 4.0 °C when "001010001010" => Temp <= X"30313434" when "001010001011" => Temp <= X"30313438" when "001010001100" =>Temp<= X"30313532";- when "001010001101" => Temp <= X"30313536";~ when "001010001110” => Temp <= X"30313630”;-! 6.0 °C when "001010001111" => Temp <= X"30313634";- when "001010010000" => Temp <= X"30313638";-

94

Chapter,,.. 3 Hardware & Software details of FPGA Based Design when "001010010001" => Temp <= X"30313732";~ when "001010010010" =>Temp<= X"30313736";- when "001010010011" => Temp <= X"30313830";-18.0°C when "001010010100" => Temp <= X"30313834";-- when "001010010101" => Temp <= X"30313838";~ when "001010010110" => Temp <= X"30313932";~ when "001010010111" => Temp <= X"30313936";~ when "001010011000" => Temp <= X"30323030";-20.0°C when "001010011001" => Temp <= X”30323034";~ when "001010011010" => Temp <= X"30323038";~ when "001010011011" => Temp <= X"30323132";~ when "001010011100" => Temp <= X"30323136";- when "001010011101" => Temp <= X"30323230";-22.0 °C when "001010011110" => Temp <= X"30323234";~ when "001010011111" => Temp <= X"30323238";~ when "001010100000" => Temp <= X"30323332";- when "001010100001" => Temp <= X"30323336";- when "001010100010" => Temp <= X"30323430";-24.0 °C when "001010100011" => Temp <= X”30323434";~ when "001010100100" => Temp <= X"30323438";~ when "001010100101" => Temp <= X"30323532";- when "001010100110" => Temp <= X"30323536”;- when "001010100111" => Temp <= X"30323630";-26.0 °C when "001010101000" => Temp <= X"30323634";- when "001010101001" => Temp <= X"30323638";-

95

Chapter..., 3 Hardware & Software details of FPGA Based Design when "001010101010” => Temp <= X"30323732";~ when "001010101011" => Temp <= X"30323736";- when "001010101100" => Temp <= X"30323830";-28.0°C when "001010101101" => Temp <= X"30323834”;~ when "001010101110" => Temp <= X"30323838";~ when "001010101111" => Temp <= X"30323932";~ when "001010110000" => Temp <= X"30323936";~ when ”001010110001 ” => Temp <= X"30333030”;-30.0°C when "001010110010" => Temp <= X"30333034";~ when "001010110011" => Temp <= X"30333038";~ when "001010110100" =>Temp<= X"30333132";~ when "001010110101" => Temp <=X”30333136";- when "001010110110" => Temp <= X"30333230”;-32.0°C when "001010110111" =>Temp <= X"30333234";~

.when "001010111000" => Temp <= X"30333238";~ when "001010111001" => Temp <= X"30333332”;- when "001010111010" => Temp <= X"30333336";- when ”001010111011" =>Temp<= X"30333430";-34.0°C when "001010111100" => Temp <= X"30333434";~ when "001010111101" => Temp <= X"30333438";~ when "001010111110" => Temp <= X"30333532";~ when "001010111111" => Temp <= X"30333536”;- when "001011000000" => Temp <= X"30333630";-36.0°C when "001011000001" => Temp <= X"30333634";- when "001011000010" => Temp <= X"30333638";~

96

Chapter.... 3 Hardware & Software details of FPGA Based Design when "001011000011" => Temp <= X"30333732";~ when ”001011000100" => Temp <= X"30333736";- when "001011000101" => Temp <= X"30333830";-38.0°C when "001011000110" => Temp <= X"3G333834";~ when "001011000111" => Temp <= X"30333838";~ when "001011001000" => Temp <= X"30333932";~ when "001011001001" => Temp <= X"30333936";~ when "001011001010" => Temp <= X"30343030";-40.0°C when "001011001011" => Temp <= X"30343034";~ . when "001011001100" =>Temp <= X"30343038";~ when "001011001101" => Temp <= X"30343132";~ when "001011001110" => Temp <= X"30343136";~ when "001011001111" => Temp <= X"30343230";-42.0°C when "001011010000" => Temp <= X"30343234";~ when ”001011010001" => Temp <= X"30343238";- when "001011010010" => Temp <= X"30343332";- when "001011010011" => Temp <= X"30343336";- when "001011010100" => Temp <= X"30343430";-44.0°C when "001011010101" => Temp <= X"30343434,,;- when "001011010110" =>Temp <= X"30343438";- when "001011010111" => Temp <= X"30343532";- when "001011011000" => Temp <= X"30343536";- when "001011011001" => Temp <= X"30343630";-46.0°C when "001011011010" => Temp <= X"30343634";- when "001011011011" => Temp <= X"30343638";-

97

Chapter..,. 3 Hardware & Software details of FPGA Based Design when "001011011100" => Temp <= X"30343732";-- when "001011011101" => Temp <= X"30343736";~ when "001011011110" => Temp <= X"30343830";-48.0°C when "001011011111" => Temp <= X"30343834";~ when "001011100000" => Temp <= X"30343838";~ when "001011100001" => Temp <= X"30343932";~ when ”001011100010" => Temp <= X"30343936";™ when "001011100011" => Temp <= X"30353030";-50.0°C when "001011100100" => Temp <= X"30353034";~ when "001011100101" => Temp <= X"30353038";~ when "001011100110" => Temp <= X"30353132";~ when "001011100111" => Temp <= X"30353136";- when "001011101000" => Temp <= X"30353230";-52.0°C when "001011101001" => Temp <= X"30353234";~ when "001011101010" => Temp <= X"30353238";~ when "001011101011"=> Temp <=X"30353332";~ when "001011101100" => Temp <= X"30353336";~ when "001011101101 " => Temp <= X"30353430";-54.0°C when "001011101110" => Temp <= X"30353434";- when "00101 1101111” => Temp <= X”30353438";- when "001011110000" => Temp <= X"3Q353532";~ when "001011110001" => Temp <= X"30353536";- when "001011110010" => Temp <= X"30353630";-56.0°C when "001011110011" => Temp <= X"30353634";- when "001011110100" => Temp <= X"30353638";~

98

Chapter.... 3 Hardware & Software details of FPGA Based Design when "001011110101" => Temp <= X"30353732";~ when "001011110110” => Temp <= X"30353736";~ when ”00101 1110111" => Temp <= XH30353830";-58.0°C when "001011111000" => Temp <= X"30353834";~ when "001011111001 ” => Temp <= X"30353838";~ when "001011111010" => Temp <= X"30353932";~ when "001011111011" => Temp <= X"30353936";~ when "001011111100" => Temp <= X"30363030";-60.0 °C when "001011111101" => Temp <= X"30363034";~ when "001011111110” => Temp <= X”30363038";~ when "001011111111" => Temp <= X"30363132";~ when "001100000000" => Temp <= X"30363136";~ when "001100000001" => Temp <= X"30363230V62.0 °C when "001100000010" => Temp <= X"30363234";- when "001100000011" => Temp <= X"30363238";~ when "001100000100" => Temp <= X"30363332";~ when "001100000101" => Temp <= X"30363336";~ when "001100000110" => Temp <= X"30363430";-64.0°C when "001100000111 ” => Temp <= X"30363434";— when "001100001000" => Temp <= X"30363438";- when "001100001001" => Temp <= X"30363532";- when "001100001010" => Temp <= X"30363536";- when "001100001011" => Temp <= X"30363630";~66.0°C when "001100001100" => Temp <= X"30363634";- when "001100001101" => Temp <= X"30363638";-

99

Chapter.... 3 Hardware & Software details of FPGA Based Design when "001100001110" => Temp <= X"30363732";~ when "001100001111" => Temp <= X"30363736";- when "001100010000" => Temp <= X"30363830";-68.0°C when "001100010001" => Temp <= X"30363834";~ when'"001100010010" => Temp <= X"30363838";~ when "001100010011" => Temp <= X"30363932";~ when "001100010100" => Temp <= X"30363936";~ when "001100010101" => Temp <= X"30373030";-70.0°C when "001100010110" => Temp <= X"30373034";~ when "001100010111" => Temp <= X"30373038";~ when "001100011000".=> Temp <= X"30373132";~ when "001100011001" => Temp <= X"30373136";~ when "001100011010" => Temp <= X"30373230";-72.0 °C when ”001100011011 ” => Temp <= X"30373234";~ when "001100011100" => Temp <= X"30373238";~ when "001100011101" => Temp <= X"30373332";~ when "001100011110" => Temp <= X”30373336";- when "001100011111" => Temp <= X"30373430";-74.0 °C when "001100100000" => Temp <= X"30373434”;~ when "001100100001" => Temp <= X"30373438";- when "001100100010" => Temp <= X"30373532";- when "001100100011" => Temp <= X"30373536";~ when "001100100100" => Temp <= X"30373630";-76.0 °C when "001100100101" => Temp <= X"30373634”;~ when "001100100110" => Temp <= X"30373638";-

100

Chapter..,. 3 Hardware & Software details of FPGA Based Design, when "001100100111" => Temp <= X"30373732";~ when "001100101000" => Temp <= X"30373736";~ when "001100101001" => Temp <= X"30373830";-78.0°C when "001100101030" => Temp <= X"30373834";~ when "001100101011" => Temp <= X"30373838";~ when "001100101100" => Temp <= X"30373932”;- when "001100101101" => Temp <= X"30373936";~ when ”001100101110" => Temp <= X"30383030";-80.0 °C when "001100101111" => Temp <= X"30383034";~ when "001100110000" => Temp <= X"30383038";~ when "001100110001" =>Temp<= X"30383132";~ when "001100110010" => Temp <= X"30383136";~ when "001100110011" => Temp <= X"30383230";-82.0°C when "001100110100" => Temp <= X"30383234";~ when "001100110101" => Temp <= X"30383238";- when "001100110110" => Temp <= X"30383332";~ when "001100110111" => Temp <= X"30383336";~ when "001100111000" => Temp <= X"30383430";-84.0°C when "001100111001" => Temp <= X"30383434";- when "001100111010" =o Temp <= X"30383438";- when "001100111011" =>Temp <= X"30383532";- when "001100111100" => Temp <= X"30383536";- when "001100111101" => Temp <= X"30383630";-86.0°C when "001100111110" => Temp <= X"30383634";- when "001100111111" => Temp <= X”30383638";~

101

Chapter.... 3 Hardware & Software details of FPGA Based Design when "001101000000" => Temp <= X"30383732";~ when "001101000001" => Temp <= X"30383736";- when "001101000010" => Temp <= X"30383830";-88.0°C when "001101000011" => Temp <= X"30383834”;- when "001101000100" => Temp <= X"30383838";- when "001101000101" => Temp <= X"30383932";~ when "001101000110" => Temp <= X”30383936";~ when "001101000111" => Temp <= X"30393030";-90.0°C when "001101001000" => Temp <= X"30393034";- when "001101001001" => Temp <= X"30393038”;~ when "001101001010" => Temp <= X"30393132";~ when "001101001011" =>Temp<= X"30393136";~ when "001101001100" => Temp <= X"30393230";-92.0 °C when "001101001101" => Temp <= X"30393234";- when "001101001110" => Temp <= X"30393238";- when "001101001111" => Temp <= X"30393332";- when "001101010000" => Temp <= X"30393336";- when "001101010001" => Temp <= X"30393430";-94.0°C when "001101010010" => Temp <= X"30393434";- when "001101010011" => Temp <= X"30393438";- when "001101010100" => Temp <= X"30393532";- when ”001101010101" => Temp <= X”30393536";- when "001101010110" => Temp <= X"30393630";-96.0°C when "001101010111" => Temp <= X"30393634";~ when "001101011000" => Temp <= X"30393638";-

102

Chapter.... 3 Hardware & Software details of FPGA Based Design when "001101011001" => Temp <= X"30393732";~ when "001101011010" => Temp <= X"30393736";~ when "001101011011" => Temp <= X"30393830";-98.0°C when "001101011100" => Temp <= X"30393834";- when "001101011101" => Temp <= X"30393838";~ when "001101011110" => Temp <= X”30393932";~ when "001101011111" => Temp <= X"30393936";~ when "001101100000" => Temp <= X,,31303030";-100.0°C when "001101100001" => Temp <= X"31303034";~ when others => Temp <= X"3F3F3F3F"; - ??.? end ease; end process P5;

------------------------------------------- Controlling the temperature—----------------

-The below statements are sending a signal to relay from FPGA and controls the temperature at a desired value —------------------------------------------------------------

P6: process (elkrelay) begin if rising_edge(clkrelay) then if ( adc_data >= "011010110010”) then -90.0 °C relay <= 'O'; else relay <= '1 end if; end if;

103

Chapter..,. 3 end process P6; end behavioral;

Hardware & Software details of FPGA Based Design

•End of the complete design

3.4 Xilinx ISE9.1i (EDA Tool)

The Integrated Software Environment (ISE 9.1 i) [15] is the Xilinx design software suite that allows to take the design from design entry through Xilinx device programming. The ISE Project Navigator manages and processes the design through the following steps in the ISE design flow. The snapshot of the Xilinx ISE 9.1i environment opening window is shown in Fig 3.25.

3.4.1 Design Entry

Design entry is the first step in the ISE design flow [16], During design entry, source files can be designed based on the design objectives. Top-level design file can be created using a Hardware Description Language (HDL), such as VHDL, Verilog, or

ABEL, or using a schematic, In the present work VHDL is used as a programming language.

104

Chapter.... 3 Hardware & Software details of FPGA Based Design

P*» r« Pro*«f» w«* Pr«*w wunkn** w*r>

3 .* W (t , » ft c X -•> j //XXA8 /» *

<• ■>! o t ^:tft jo ■ «

(^^■■■■■■■■3

| 5owr»» Sc* j.ArrttrrTvrtMm

^ I *

- ♦ *

IIMNT tcrtt

TI r . '

'4

L»

- 'J to '•**>.k-<lP*1 ® mmmmtsmtmaasL i ^

«

I *2 'iMcn ^

,n..

»v " nisxpu

?;r.*.in v*ct*p • »»»*ti' -

■ Pwcrit«i« *ft74 lcd_P»1 (13 • Ck#**vBMi .

I Xi V«s»*C^*jn St trm&t

1 * > :<•■*•••*»»••

* *

*)0

Uw Cortt^ar#:

* • ^ST

| - f J f , '.Tctowr • l>»uy

* tiO Tiwidtfe

• (&»%.

- f FVTUYrroxi f Ip

:••

20

22

23

Por

•tfS'Jl i*! »y led P*

•ic_dati» : i DC''it el It 100 k relay

**de_PC

LEI ied_control lcd_d«t»

•ad •dS7d relay led PrlC ir» (letvavmra;

Y OfrmMwFKBm.AU

« 4TAG ‘A.

-* LorM m L)*> x « WFVdl TI

• fjnm.

clkdlv signal clRjtace clfckey

'£ ^ocews l r>»^ r>t*-rt«ry *•» *^>^4_*«*•»»_**«J oicytJir .7

vhd: r 11» •0:/r«)'«cl574 relay_lcd PeiOO/ad5?d relay

Architecture behavioral ot Entity «4S*M reiaylcd pt 100 i» vy rd Ct 3

0 date

Froceos "Check Syntax” roreplete-d »ucces>»ful ly y ., t*~» Qfr*, j Wmnp JldSW n'ndrtrdai

■

J «?•

M M *■*

Fig.3.25 Opening window of Xilinx ISE 9.1i Enviornment for FPGA

' Jdt3

.

* «

Ut 20Cd 1 ‘if* »K4

11 r>Pkt

3.4.2 Assigning Package Pins

Input and output signals to package pins in the design are assigned using the Assign

Package Pins process. This process launches the Floorplan Editor View within ISE and displays pin constraint information for the design. This process launches Pinout and Area Constraints Editor (PACE) for all other device-targeted designs. Using the editor, one can assign I/O locations, specify I/O banks, specify I/O standards, prohibit

I/O locations, and create legal pin assignments using the built-in design rule checks

(DRC). Package pin assignments are saved as a user constraints file (UCF). The snapshot of the package pins assignment window is shown in Fig.3.26.

105

Chapter.... 3 Hardware & Software details of FPGA Based Design a u„,r

-

-b: , ij mmx

File Ed* view 06s Areas Tools Window Help

□ aS H o

H X V?

H b ® 8 & .i

J .jfg

* _J

1 Global Logic

3

Logc nr , *

•

1

X 'A X 8U3

"i 3 SET UU ■” . »L

ZZ1

D

| I/O Name I/O D*ection| Loc adc data<0> InOut adc data<1> InOut adc data<2> InOut adc data<3> adc data<4>

InOut

InOut adc da»a<5> InOut adc oata<6> InOut adc dafa<?

InOut adc data<:8> adc da»a<9;

InOut

InOut adc da»a<10> InOut adc dala<11s InOut adc RC InOut elk 100k Input led controk0> Output led contiokD Output lcd_contiok2' Output led data<0> Output led data<D led data<2> led data<3>

Output

Output

Output

Output led dala<4> led data<5> Output led da»a<7> Output

P5

P4

P3

P2

P52

P77

P57

P56

P19

P18

P16

P15

P11

P10

P9

P7

P61

P71

P72

P74

P78

P85

P96

P87

P90

_______________

^/chapters

Rank|

BANK 7

BANK7

BANK 7

BANK?

BANK 7

BANK7

BANK?

BANK?

BANK7

BANK7

BANK7

BANK7

BANK6

BANK5

BANK5

BANK5

BANK5

BANK5

BANK5

BANK 5

BANK5

BANK 4

BANK4

BANK 4

BANK4

I/O

___

■

:

1 Hi •• ••

|\ Padugr Vl*w

/\ /fcNlertJre

View / jMyComputer fa]chapt«3 [Co. .

■

• | Xfcn- I5E ■ 0.. [TTS

T op View

• Q4MOO

1

■■ ty] Owpcerl [Co..

________ l-Ll

^5:3^ *Y t 25 PM

X41Y17

Fig.3.26 The package pins assignment window for FPGA (XC3S400)

3.4.3 Synthesis

After design entry and optional simulation, it needs to run synthesis. During this step,

VHDL, designs become netlist files that are accepted as input to the implementation step.

3.4.4 Implementation

Design implementation should be run after synthesis, which converts the logical design into a physical file format that can be downloaded to the selected target device.

From Project Navigator, the implementation process can be run in one step, or each of

106

Chapter,.,. 3 Hardware & Software details of FPGA Based Design the implementation processes can be run separately. Implementation processes vary depending on the target device like FPGA or CPLD.

3.4.5 Verification

The functionality of the design can be verified at several points in the design flow.

Simulator software can be used to verify the functionality and timing of the design or a portion of the design. The simulator interprets VHDL or Verilog code into circuit functionality and displays logical results of the described HDL to determine correct circuit operation. Simulation allows, to create and verify complex functions in a relatively small amount of time. In-circuit verification can also be run after programming the device.

3.4.6 Device Configuration

The device is configured after generating a programming file; during configuration, the generated configuration files and programming files are downloaded to Xilinx device from host computer.

3.4.7 Configuration Overview

Configuring a Device

FPGAs can be configured by using different modes like Boundary Scan, Slave Serial, or Select MAP. The most commonly used mode is Boundary Scan. When using this mode, the cable leads should be connect to the following pins: TDO, TDI, TCK,

TMS, VCC and GND. JTAG Programmer only accepts FPGA configuration files in the binary bitstream format (*.bit).

»

107

Chapter.... 3 Hardware & Software details of FPGA Based Design

PROM Files

Xilinx FPGAs are SRAM-based and must be programmed every time power is cycled. The most common method of programming Xilinx FPGAs is by using Xilinx

PROMs connected to a chain of FPGAs as shown Fig.3.27. These PROMs must be programmed using PROM files created from the FPGA chain bitstreams. PROM files include information on the FPGA chain length and contain bitstreams that are reformatted for use with PROM programmers. Several PROM file formats are available: MGS, EXO, TEK, HEX, UFP, BIN, and ISC. IMPACT can directly program Xilinx PROM devices using MCS, EXO, and ISC file formats. In the present work FPGA is programmed using *.bit file and PROM is programmed using *.mcs file.

Fig.3.27 JTAG Chain which shows the configured devices

108

Chapter.... 3 Hardware & Software details of FPGA Based Design

3.5 Temperature Measurement by interfacing PtlOO to FPGA using

AD574

Fig.3.28 shows the photograph of the complete FPGA based temperature measurement and control system. PtlOO is inserted in the water bath; when the temperature of the water bath changes, then the resistance of PtlOO is also changes.

The output produced by the PtlOO needs to be converted into quantized voltage levels.

This can be achieved through a process known as “signal conditioning”. The signal conditioning circuit gives the analog voltage, which is proportional to the temperature. The output of the signal conditioning circuit is fed to the ADC (AD574), since FPGA can process only digital data. AD574 converts the input analog voltage into 12-bit digital data.

Fig.3.28 Photograph of the FPGA based temperature measurement & Control System

109

Chapter.... 3 Hardware & Software details of FPGA Based Design

In order to initiate AD574, FPGA sends a high signal to R/C pin of AD574.

The conversion starts when signal to R/C goes low. When the end of conversion signal of the AD574 is found to be high, it is an indication to the FPGA that 12-bit data which represents the temperature can be read in. FPGA compares the corresponding temperature value from look up table and finally displays on LCD. The result is displayed in two lines as shown in Fig.3.29. The first line displays

TEMPERATURE: and the second line displays the measured temperature value with first decimal and units as °C.

Fig.3.29 Photograph showing the results on LCD

110

Chapter.... 3 Hardwares Software details of FPGA Based Design

REFERENCES

1. Dr. Matthew S. Goodman, Dr. Gerald M. Borsuk and Dr. Carter Armstrong,

Report of department of defense advisory group on electron devices special technology area review on FPGAs for military applications, 2005, 1-63.

2. http://www.electronics-tutorials.ws/io/io_3.html.

3 .

http://www.maxim-ic.com/app-notes/index.mvp/id/3450.

4 .

K. Sreelekha, Design and development of a microcontroller based measurement system for fluoride ion concentration using ion selective electrode, Ph.D. thesis, S.KLUniversity, Anantapur, India, 2010.

5. Muhammad Ali Mazidi, Janice Gillispie and Mazidi, The 8051

Microcontroller and Embedded Systems, Printice-Hall of India Private

Limited, New Delhi, 2005.

6. AD574 complete 12-bit A/D Converter Data sheet, Analog Devices.

7. http://www.electronics-tutorials.ws/io/io_5.html.

8. Relay Driving Basics, http://www.jaycar.com.au/images_upioaded/relaydrv.pdf.

9 .

Ognjen Scekic, prof, dr Veljko Milutinovic, FPGA Comparative Analysis,

University of Belgrade, Belgrade 2005,1-48.

10 .

Spartan-3 FPGA Family: .Complete Data Sheet DS099, 2009. http://www.xilinx.com/support/documentation/data_sheets/ds312.pdf.

11 .

ADM TKB208 User Manual-XC3Sxx D-Board, Applied Digital

Microsystems, Mumbai, http://www.admlindia.com.

Ill

Chapter.... 3 Hardware & Software details of FPGA Based Design

12. Xilinx XCF02S, JTAG PROMs for Data Storage Applications, XAPP544,

2008.

http://www.xilinx.com/support/documentation/application_notes/xapp544.pdf.

13. Savita Sonoli, Design and Implementation of FPGA based PID Controller for

DC Motor, Ph.D, thesis, S.K.University, Anantapur, India, 2009.

14. JTAG Programmer Guide, http://www.xilinx.com/itp/3_l i/pdf/docs/jtg/jtg.pdf.

15. JTAG Interface: Simple Introduction, www.amontec.com/pub/amt_ann004.pdf.

16. ISE9.1 i Quick Start Tutorial, http://www.xilinx.com/itp/xilinx9/books/docs/qst/qst.pdf.

17. ISE Help Xilinx ISE Overview,

Xilinx9.1 i/doc/usenglish/help/iseguide/whnjs.htm.

112