Application Note 9-17: GT3000 64L TQFP Recommended PCB

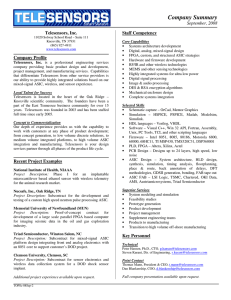

advertisement

Application Note 9.17 GT3200 64L TQFP Recommended PCB Layout Rev. 1.7 General Description The GT3200 is a stand-alone USB 2.0 Transceiver. It is also offered as a hard IP core (GT3100) on specific process nodes. This document illustrates a sample board schematic with detailed notes on specific component selection and placement as well as board layout. Notes labeled as ‘required’ indicate items that are critical to device performance and functionality. Those notes listed as ‘recommended’ will give optimum results and should therefore be adhered to whenever possible. Figure 1 illustrates the 64 lead TQFP pin-out while Figure 2 adds the external components to be used with the SMSC PHY. USB 2.0 Transceiver Macrocell Interface (UTMI) These pins are illustrated on Figure 2 as connecting to a generic UTMI interface and utilize 3.3V CMOS signaling levels. Analog Interface These pins are illustrated in Figure 2 and constitute pins 1 through 13. Note that aside from the typical supply bypass capacitors the only external components required for the PHY are those in the 12MHz crystal network and a 12kΩ external biasing resistor. Many interfaces available require an external 1.5kΩ in addition to two 45Ω resistors in series with the DP and DM data lines. These resistors have been integrated into the PHY IP core to save customers the added cost of having to place these components external to the IC. Most of the detailed notes in this application note are driven by the precision requirements of this analog interface. Careful attention should be paid to minimizing the introduction of noise to this interface. SMSC AN 9.17 1 APPLICATION NOTE Rev. 1.7 (05-12-03) © STANDARD MICROSYSTEMS CORPORATION (SMSC) 2003 80 Arkay Drive Hauppauge, NY 11788 (631) 435-6000 FAX (631) 273-3123 Standard Microsystems and SMSC are registered trademarks of Standard Microsystems Corporation. Product names and company names are the trademarks of their respective holders. Circuit diagrams utilizing SMSC products are included as a means of illustrating typical applications; consequently complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the semiconductor devices described any licenses under the patent rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC’s website at http://www.smsc.com. SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT, TORT, NEGLIGENCE OF SMSC OR OTHERS, STRICT LIABILITY, BREACH OF WARRANTY, OR OTHERWISE; WHETHER OR NOT ANY REMEDY IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE; AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. SMSC AN 9.17 2 APPLICATION NOTE Rev. 1.7 (05-12-03) Revision History REVISION LEVEL AND DATE Rev 1.7 05-12-03 Rev 1.7 05-12-03 Rev. 1.7 04-23-03 Rev. 1.7 04-23-03 Rev. 1.6 01-21-03 Rev. 1.6 01-21-03 Rev. 1.5 07-09-02 SECTION/FIGURE/ENTRY CORRECTION Power Supply Filtering – pg. 7 Figure 2 - 64L TQFP Board Schematic – pg. 5 Table 1 - 64L TQFP GT3200 PCB Connection Table – pg. 6 Modifications to numbers 1, 3, 14 Power Supply Filtering – pg. 7 Added this section. Analog Interface, RBIAS (R1) – pg. 1, 8 Updated Rbias to 12kΩ 1% Table 1- 64L TQFP GT3200 PCB Connection Table – pg. 6 Updated table, Pin 18 Added External Capacitance section. Updated “DP AND DM DATA LINES” section to reflect 90Ω differential trace impedance. Updated board schematic. Updated Crystal recommendation. Updated External Regulator recommendation. Removed “Test Pins” section. Removed “Package Outline” section. Added Figure 2 – Board schematic. Changed RBIAS (R1) to 12.1kΩ Rev. 1.4 03-12-02 Rev. 1.3 02-16-02 Rev. 1.2 12-11-01 SMSC AN 9.17 Added the following sentence: The analog power should be supplied to the pins of the GT3200 after it’s gone through the ferrite bead. Updated figure Initial release 3 APPLICATION NOTE Rev. 1.7 (05-12-03) CLKOUT VSS VALIDH RXVALID TXVALID DATA[0] VDD3.3 54 53 52 51 50 49 RXACTIVE 56 55 TXREADY RXERROR VDD1.8 58 57 59 VSS DATABUS16_8 62 61 TESTGND2 TESTGND3 63 60 VSS 64 N/C 1 48 VSS VSSA 2 47 DATA[1] N/C 46 DATA[2] DM 3 4 45 DATA[3] DP 5 VDDA3.3 6 VSSA 7 RBIAS 8 VDDA3.3 9 USB 2.0 GT3200 PHY IC 44 DATA[4] 43 VDD1.8 42 41 DATA[5] DATA[6] 40 DATA[7] VSSA 10 39 DATA[8] 27 28 29 30 31 32 RESET DATA[15] DATA[14] DATA[13] VDD3.3 OPMODE[0] XCVRSELECT VDD1.8 VSS 26 DATA[12] 33 25 34 16 LINESTATE[1] 15 TESTGND1 LINESTATE[0] SUSPENDN 23 24 DATA[11] 22 DATA[10] 35 OPMODE[1] 36 14 21 13 N/C VSS VDDA1.8 TERMSELECT DATA[9] 19 20 37 VDD1.8 12 18 VSS 17 38 VSS 11 VDD3.3 XI XO Figure 1 - PHY Pinout of 64L TQFP Package SMSC AN 9.17 Page 4 APPLICATION NOTE Rev. 1.7 (05-12-03) VDD3.3 regulator output C3 C4 VDDA3.3 FB1 C5 C11 C10 C9 VSS VSSA VDD1.8 C6 C7 VDDA1.8 FB2 regulator output C8 C14 C13 C12 VSS 8 9 10 VDD3.3 49 50 51 52 VSS 54 55 56 53 41 40 39 12 37 13 36 VSS 35 34 32 31 VSS VDD3.3 30 29 28 33 VDD1.8 19 20 VDD1.8 23 24 17 18 VSS VDD3.3 16 25 LINESTATE[1 ] LINESTATE[0 26 ] 27 38 14 VDD1.8 42 11 15 VSSA 43 USB 2.0 GT3200 PHY IC 22 XT1 VSS 46 VSS VDDA1.8 N/C R2 58 57 44 VSSA C2 59 5 7 C1 61 45 6 R1 60 47 3 4 VDDA3.3 VDDA3.3 VSSA 62 2 TERMSELEC T USB Connector 48 UTMI INTERFACE VSSA N/C 1 21 N/C 63 64 VSS VDD1.8 VSSA Figure 2 - 64L TQFP Board Schematic SMSC AN 9.17 5 APPLICATION NOTE Rev. 1.7 (05-12-03) Table 1 - 64L TQFP GT3200 PCB Connection Table NUMBER 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 SMSC AN 9.17 NAME N/C VSSA N/C DM DP VDDA3.3 VSSA RBIAS VDDA3.3 VSSA XI XO VDDA1.8 N/C SUSPENDN TESTGND1 VSS VDD3.3 VDD1.8 XCVRSELECT TERMSELECT VSS OPMODE[1] OPMODE[0] LINESTATE[1] LINESTATE[0] VDD1.8 RESET DATA[15] DATA[14] DATA[13] VDD3.3 VSS DATA[12] DATA[11] DATA[10] DATA[9] VSS DATA[8] DATA[7] DATA[6] DATA[5] VDD1.8 DATA[4] DATA[3] DIRECTION N/A N/A N/A I/O I/O N/A N/A I/O N/A N/A I/O I/O N/A N/A Input N/A N/A N/A N/A Input Input N/A Input Input Output Output N/A Input I/O I/O I/O N/A N/A I/O I/O I/O I/O N/A I/O I/O I/O I/O N/A I/O I/O TYPE N/A DC N/A 3.3V Analog 3.3V Analog DC DC 3.3V Analog DC DC 3.3V Analog 3.3V Analog DC N/A 3.3V CMOS DC DC DC DC 3.3V CMOS 3.3V CMOS DC 3.3V CMOS 3.3V CMOS 3.3V CMOS 3.3V CMOS DC 3.3V CMOS 3.3V CMOS 3.3V CMOS 3.3V CMOS DC DC 3.3V CMOS 3.3V CMOS 3.3V CMOS 3.3V CMOS DC 3.3V CMOS 3.3V CMOS 3.3V CMOS 3.3V CMOS DC 3.3V CMOS 3.3V CMOS CONNECTION POINT No Connect Analog GND Plane No Connect USB Connector USB Connector 3.3V Analog Supply Plane Analog GND Plane Resistor to Analog GND Plane 3.3V Analog Supply Plane Analog GND Plane XTAL Network XTAL Network 1.8V Analog Supply Plane No Connect ASIC / FPGA Analog GND Plane Digital GND Plane 3.3V Digital Supply Plane 1.8V Digital Supply Plane ASIC / FPGA ASIC / FPGA Digital GND Plane ASIC / FPGA ASIC / FPGA ASIC / FPGA ASIC / FPGA 1.8V Digital Supply Plane ASIC / FPGA ASIC / FPGA ASIC / FPGA ASIC / FPGA 3.3V Digital Supply Plane Digital GND Plane ASIC / FPGA ASIC / FPGA ASIC / FPGA ASIC / FPGA Digital GND Plane ASIC / FPGA ASIC / FPGA ASIC / FPGA ASIC / FPGA 1.8V Digital Supply Plane ASIC / FPGA ASIC / FPGA Page 6 APPLICATION NOTE Rev. 1.7 (05-12-03) NUMBER 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 NAME DATA[2] DATA[1] VSS VDD3.3 DATA[0] TXVALID RXVALID VALIDH VSS CLKOUT RXACTIVE TXREADY RXERROR VDD1.8 DATABUS16_8 VSS TESTGND3 TESTGND2 VSS DIRECTION I/O I/O N/A N/A I/O Input Output I/O N/A Output Output Output Output N/A Input N/A N/A N/A N/A TYPE 3.3V CMOS 3.3V CMOS DC DC 3.3V CMOS 3.3V CMOS 3.3V CMOS 3.3V CMOS DC 3.3V CMOS 3.3V CMOS 3.3V CMOS 3.3V CMOS DC 3.3V CMOS DC DC DC DC CONNECTION POINT ASIC / FPGA ASIC / FPGA Digital GND Plane 3.3V Digital Supply Plane ASIC / FPGA ASIC / FPGA ASIC / FPGA ASIC / FPGA Digital GND Plane ASIC / FPGA ASIC / FPGA ASIC / FPGA ASIC / FPGA 1.8V Digital Supply Plane ASIC / FPGA Digital GND Plane Digital GND Plane Digital GND Plane Digital GND Plane Board Layout Specifications Power Planes REQUIRED: A sufficient number of power and ground planes should be included to provide solid, low impedance connections to the power supply sources. Considerable care must be taken to provide quiet supplies to the analog section of the IC, consisting of supplies VDDA1.8 and VDD3.3, as well as the analog ground VSSA. If the 1.8V supply is not available on the test board, it must be derived from an external regulator. See the section on external regulator requirements for details. If the device is bus-powered from VBUS, then both supplies must be derived from an external regulator. RECOMMENDED: The methods of providing stable power and ground supply planes will vary among applications. The following 6-layer plane stack should provide adequate performance: 1. 2. 3. 4. 5. 6. SIGNAL LAYER 1 – Used for all primary signal routes VSS VDD3.3 PWR + VDDA3.3 PWR sub-planes (2 isolated planes on the same layer) VDD1.8 PWR + VDDA1.8 PWR sub-planes (2 isolated planes on the same layer) VSSA SIGNAL LAYER 2 – Used for signal routing and component placement directly under IC An alternate implementation would be to via planes 2 and 5 together, providing a shared, but lower impedance VSS plane. Power Supply Filtering REQUIRED: A ferrite bead is required on both the 3.3V and 1.8V supplies between the analog and digital supply pins (if using a single regulator for both analog and digital supply). The analog power should be supplied to the pins of the GT3200 after it’s gone through the ferrite bead. This is illustrated in Figure 2 as FB1 and FB2. The ferrite bead is used to isolate any noise on the digital power pins from getting coupled into the analog power pins. Not SMSC AN 9.17 7 APPLICATION NOTE Rev. 1.7 (05-12-03) following this requirement may cause instability in the PLL, and degrade the signal quality on the DP/DM lines. The ferrite beads should have a DC impedance of less than 0.5 Ohms. Bypass Capacitors REQUIRED: Some level of bypassing is needed for the PHY supply rails to bypass large current spikes that could generate significant voltage drops at the IC pins, thereby injecting noise. A minimum of 10uF should be used in close proximity to the power supply input to the board. Capacitors that are large in value tend to have a lower frequency roll-off due to their typically larger equivalent series resistance (ESR) than those of smaller capacitors. The required 0.1uF, low-ESR capacitors are used in parallel with the 10uF values for higher frequency bypassing. These lower valued bypass capacitors should be placed in close proximity to the IC supply pins (preferably directly under the IC). RECOMMENDED: To provide additional bypassing for high noise frequencies, 0.01uF capacitors may also be used. It is recommended that bypass capacitors be placed underneath the PHY in close proximity to the supply pins, utilizing the lowest layer of the board to access the bypass capacitors. Crystal Network REQUIRED: A 12MHz crystal with 50ppm (over temperature variation) worst-case jitter is required. Note that the 50ppm jitter is a direct contributor to the transmit and receive jitter budget as defined by the USB 2.0 specification. The crystal requires a resistor and capacitor network and is specified by the crystal manufacturer. The loading of pins 11 and 12 on the crystal can be estimated as 2pF. The components should be placed in close proximity to the IC and relative to each other. Care should be taken to keep any switching lines away from this crystal network and the associated routes to pins 11 and 12. RECOMMENDED: The Raltron 12MHz AS-SMD (designed to see 18pF Cload) crystal has been used during GT3200 evaluation with positive results. Use of the Raltron crystal requires a 1MΩ resistor for R2, and 34pF capacitors for C1 and C2. The recommended layout would include placement of the crystal network on the board directly underneath the GT3200, using the lowest plane to route from vias to the crystal network components. DP and DM Data Lines REQUIRED: Traces starting at pins 4 (DM) and 5 (DP) and ending at the USB connector must be routed differentially, be equal in length, and have a trace impedance of 45Ω each (90Ω differential trace impedance). The differential routes maintain the differential nature of these signals. The equal length and 90Ω differential trace impedance are required to match delays and minimize transmission line reflections, respectively. These lines must also be reasonably isolated from any other switching lines to minimize crosstalk. RECOMMENDED: Ground shields can be used to provide isolation of the DP/DM traces. Vias to the local GND plane placed along the outer edges of the DP and DM trace have been used to provide adequate shielding on evaluation hardware. RBIAS (R1) REQUIRED: A 12kΩ, +/- 1% resistor must be placed from pin 8 to VSSA. This resistor defines the master biasing for the GT3200, and care must be taken to minimize noise injection to this point. The resistor (R1) should be placed as close as possible to GT3200, with care taken to isolate the resistor and associated traces from switching noise. RECOMMENDED: It is recommended that R1 be placed directly underneath the GT3200, utilizing the lowest plane to access the resistor terminals. SMSC AN 9.17 Page 8 APPLICATION NOTE Rev. 1.7 (05-12-03) External Regulator RECOMMENDED: In order to derive VDD1.8 from the 3.3V supply, the following regulator is recommended: Texas Instruments TPS76318. External Capacitance The USB 2.0 specification states that in high-speed mode, there should be no more than 10pF (CLOAD) between the data lines (DP and DM) and ground. The GT3200 contributes approximately 4pF of the allotted 10pF CLOAD budget. Designers using the GT3200 will have a 6pF capacitance budget for PCB traces, the connector and cable. Also, according to the USB 2.0 specification, the DP and DM lines must match to within 1pF of each other. USB Connector A USB type B connector that has been High Speed Certified by the USB-IF should be used with the GT3200. Connectors that have been certified are listed at www.usb.org. Pin 1: VBUS. VBUS does not interface with the PHY. It may be interfaced with the device controller to monitor device connect and disconnect. Remember that this is a 5V signal and the device controller I/O must be 5V tolerant or a resistor network may be used to divide the voltage down to 3.3V. Pin 2: DM. See section DP and DM Data Lines for routing recommendations. Pin 3: DP. See section DP and DM Data Lines for routing recommendations. Pin 4: GROUND. On board designs that have the ground planes split into VSS and VSSA, it is recommended to connect Pin 4 of the USB connector to VSSA. If the ground planes are not split, just connect this pin to ground. SMSC AN 9.17 9 APPLICATION NOTE Rev. 1.7 (05-12-03)