Representations of bits AND and OR gates using switches

advertisement

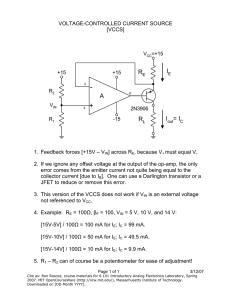

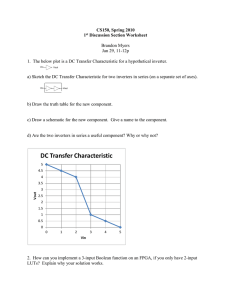

Representations of bits Ta bl e 3 - 1 Physical states representing bits in different computer logic and memory technologies. State Representing Bit Technology 0 1 Pneumatic logic Fluid at low pressure Fluid at high pressure Relay logic Circuit open Circuit closed Complementary metal-oxide semiconductor (CMOS) logic 0–1.5 V 3.5–5.0 V Transistor-transistor logic (TTL) 0–0.8 V 2.0–5.0 V Fiber optics Light off Light on Dynamic memory Capacitor discharged Capacitor charged Nonvolatile, erasable memory Electrons trapped Electrons released Bipolar read-only memory Fuse blown Fuse intact Bubble memory No magnetic bubble Bubble present Magnetic tape or disk Flux direction “north” Flux direction “south” Polymer memory Molecule in state A Molecule in state B Read-only compact disc No pit Pit Rewriteable compact disc Dye in crystalline state Dye in noncrystalline state Not all logic representations are suitable for logic gates. Logic device must outputs that are of the same type as its inputs. October 3, 2002 EE 121: Digital Design Laboratory Lecture 3 – 1 AND and OR gates using switches Single-pole single-throw (SPST) switches are either normally open (n.o.) or normally closed (n.c.). Normally-open switches can be used to build AND and OR gates. AND gate: serial connection: V + − LED A October 3, 2002 B OR gate: parallel connection: V + − LED A EE 121: Digital Design Laboratory B Lecture 3 – 2 MOS transistors Logic levels for CMOS circuits have wide range, from > 12 V down to ∼ 1 V. Often 5 V is used for compatibility with older logic families (TTL). 5.0 V Logic 1 (HIGH) 3.5 V undefined logic level 1.5 V Logic 0 (LOW) 0.0 V Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e MOS transistors are voltage-controlled resistances that we use as switches. VIN Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e n-type transistors are normally open; p-type transistors are normally closed. + source Vgs − Voltage-controlled resistance: increase Vgs ==> decrease Rds drain gate Vgs + source gate drain Note: normally, Vgs ≥0 − Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e October 3, 2002 Voltage-controlled resistance: decrease Vgs ==> decrease Rds Note: normally, Vgs ≤0 Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e EE 121: Digital Design Laboratory Lecture 3 – 3 CMOS inverter Schematic, function table, and logic symbol: VDD = +5.0 V (a) VDD = +5.0 V Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e (b) VIN Q1 Q2 VOUT 0.0 (L) 5.0 (H) off on on off 5.0 (H) 0.0 (L) Q2 on when VIN is low (p-channel) Q2 (p-channel) VOUT VIN Q1 VIN VOUT Q1 (n-channel) on when VIN is high (n-channel) (c) IN OUT Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e Switch view of CMOS inverter: (a) VIN = L VDD = +5.0 V (b) VOUT = H VDD = +5.0 V VIN = H VOUT = L Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e October 3, 2002 EE 121: Digital Design Laboratory Lecture 3 – 4 CMOS NAND Schematic, function table, and logic symbol: VDD (a) Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e (b) Q2 Q4 Z A Q1 B Q3 (c) A B Q1 Q2 Q3 Q4 Z L L H H off off on on on on off off off on off on on off on off H H H L L H L H A Z B Switch models for CMOS NAND gate: VDD (a) VDD (b) VDD (c) Z=H Z=H Z=L A=L A=H A=H B=L B=L B=H Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e October 3, 2002 EE 121: Digital Design Laboratory Lecture 3 – 5 CMOS NOR VDD (a) A B (b) Q2 Q4 A B Q1 Q2 Q3 Q4 Z L L H H off off on on on on off off off on off on on off on off H L L L L H L H Z Q1 Q3 (c) A B Z Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e NAND and NOR are dual Boolean functions (to be discussed later). Their logic circuits are dual circuits. Performance of NAND or NOR is not the same because pMOS and nMOS transistors have different characteristics. CMOS NAND gates are faster than NOR gates because of series connnection of n-channel transistors has higher conductance than series connection of p-channel transistors. October 3, 2002 EE 121: Digital Design Laboratory Lecture 3 – 6 n-input NAND and NOR VDD (a) Q2 (b) Q4 Z A Q1 B Q3 A B C Q1 Q2 Q3 Q4 Q5 Q6 Z L L H H L L H H off off off off on on on on on on on on off off off off off off on on off off on on on on off off on on off off off on off on off on off on on off on off on off on off H H H H H H H L L L L L H H H H Q6 A B C (c) C L H L H L H L H Q5 Z Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e This implementation of n-input NAND or NOR uses n pairs of transistors. Unfortunately, delay increases with the number of inputs: delay ≈ a + bn2 October 3, 2002 EE 121: Digital Design Laboratory Lecture 3 – 7 Large fan-in gates For a large number of inputs, it is faster to use multiple gates. Example: 8-input NAND might be faster using three small gate delays. I1 I2 I3 I4 OUT I5 I6 I7 I8 I1 I2 I3 I4 I5 OUT I6 I7 I8 Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e Note the tradeoff between speed and cost: 22 transistors vs. 16 transistors. Cost is proportional to the number of transistors or area in integrated circuit. October 3, 2002 EE 121: Digital Design Laboratory Lecture 3 – 8 CMOS AND-OR-INVERT The circuit below uses two AND gates (2 · 6 = 12T) and one NOR gate (4T). A B Z C D Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e This logic function can be implemented directly using 8 transistors. Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e VDD (a) (b) A Q2 Q4 Q6 Q8 B Z C Q5 Q3 D Q7 Q1 October 3, 2002 A B C D Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 Z L L L L L L L L H H H H H H H H off off off off off off off off on on on on on on on on on on on on on on on on off off off off off off off off off off off off on on on on off off off off on on on on on on on on off off off off on on on on off off off off off off on on off off on on off off on on off off on on on on off off on on off off on on off off on on off off off on off on off on off on off on off on off on off on on off on off on off on off on off on off on off on off H H H L H H H L H H H L L L L L L L L L H H H H L L L L H H H H L L H H L L H H L L H H L L H H L H L H L H L H L H L H L H L H EE 121: Digital Design Laboratory Lecture 3 – 9 CMOS steady-state electrical behavior VDD = +5.0 V (a) Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e (b) VIN Q1 Q2 VOUT 0.0 (L) 5.0 (H) off on on off 5.0 (H) 0.0 (L) Q2 (p-channel) VOUT Q1 VIN (n-channel) (c) IN OUT VOUT 5.0 HIGH VCC 3.5 VOHmin HIGH undefined VIHmin 0.7 VCC High-state DC noise margin ABNORMAL 1.5 VILmax 0.3 VCC LOW 0 LOW VIN 0 1.5 LOW 3.5 undefined 5.0 0 Low-state DC noise margin HIGH Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e October 3, 2002 VOLmax Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e EE 121: Digital Design Laboratory Lecture 3 – 10 Resistive loads, nonideal inputs (a) (b) VCC VCC "sourcing current" CMOS inverter CMOS inverter Rp > 1 MΩ Rp VOLmax VIN VIN IOLmax Rn resistive load VOHmin resistive load Rn > 1 MΩ IOHmax "sinking current" Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e Output voltage will differ from ideal high or low if too much output current. The voltage shift may not matter for analog applications (LEDs). But the output should not also be connected to inputs of CMOS gates. Intermediate input voltages (e.g., 2.5 V) cause both transistors to turn on partially and steady state current to flow. Unused inputs should be connected to some signal or voltage level. +5 V (a) (b) (c) X Z 1 kΩ X logic 1 Z logic 0 1k Ω Z X Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e October 3, 2002 EE 121: Digital Design Laboratory Lecture 3 – 11 Timing diagrams (a) (b) tr (c) tf VIHmin HIGH LOW VILmax tr tf Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e TEST CIRCUIT FOR ALL OUTPUTS LOADING VCC VCC Parameter t en Pulse Generator VIN VOUT Device Under Test RL t dis RL CL S1 S2 50 pF or 150 pF Open Closed 1 KΩ Closed Open tpZH tpZL S1 tpHZ 1 KΩ tpLZ S2 CL RT t pd tH VCC 50% 0.0 V Clock Input tREM Asynchronous Control Input (PR, CLR, etc.) VCC 50% 0.0 V Synchronous Control Input (CLKEN, etc.) VCC 50% 0.0 V tH PROPAGATION DELAY Open Open Open PULSE WIDTH LOW-HIGH-LOW Pulse tW HIGH-LOW-HIGH Pulse VOH 50% VOL VOH 50% VOL THREE-STATE ENABLE AND DISABLE TIMES Enable Same-Phase Input Transition tPLH tPHL tPLH tPHL Output Transition Opposite-Phase Input Transition Closed VCC 50% 0.0 V Data Input tSU — Open Closed DEFINITIONS: CL = Load capacitance, includes jig and probe capacitance. RT = Termination resistance, should equal ZOUT of the Pulse Generator. SETUP, HOLD, AND RELEASE TIMES tSU 50 pF or 150 pF VCC 50% 0.0 V Disable Control Input tPZL VOH 50% VOL Output Normally LOW VCC 50% 0.0 V Output Normally HIGH tPLZ 50% tPZH tPHZ 50% VCC 50% 0.0 V VCC 10% VOL VOH 90% 0.0 V Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e October 3, 2002 EE 121: Digital Design Laboratory Lecture 3 – 12 CMOS dynamic electrical behavior VDD = +5.0 V VCC = +5.0 V Equivalent load for transition-time analysis CMOS inverter Q2 Rp on when VIN is low (p-channel) VOUT Q1 VIN on when VIN is high (n-channel) RL VOUT VIN + Rn CL Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e VL − Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e VCC = +5.0 V VCC = +5.0 V (a) (b) 200 Ω Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e > 1 MΩ AC load AC load VOUT = 5.0 V VIN VOUT VIN IOUT = 0 100 Ω > 1 MΩ IOUT 100 pF 100 pF October 3, 2002 EE 121: Digital Design Laboratory Lecture 3 – 13 CMOS dynamic electrical behavior (2) VCC = +5.0 V VCC = +5.0 V (a) (b) 200 Ω Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e > 1 MΩ AC load AC load VOUT = 5.0 V VIN VOUT VIN IOUT = 0 100 Ω > 1 MΩ IOUT 100 pF 100 pF Fall time for high-to-low transition of CMOS output Rp Rn 200 Ω > 1 MΩ > 1 MΩ 100 Ω Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e 5V 3.5 V VOUT 1.5 V 0V time 0 tf October 3, 2002 EE 121: Digital Design Laboratory Lecture 3 – 14 CMOS dynamic electrical behavior (3) VCC = +5.0 V VCC = +5.0 V (a) Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e (b) 200 Ω > 1 MΩ AC load AC load VOUT = 0 V VIN VIN IOUT = 0 100 Ω VOUT IOUT > 1 MΩ 100 pF 100 pF Fall time for low-to-high transition of CMOS output Rp Rn 200 Ω > 1 MΩ > 1 MΩ 100 Ω 5V 3.5 V VOUT 1.5 V 0V time 0 tr October 3, 2002 Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e EE 121: Digital Design Laboratory Lecture 3 – 15 Propagation delays Rp Rn 200 Ω > 1 MΩ > 1 MΩ 100 Ω Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e Rp Rn 200 Ω > 1 MΩ > 1 MΩ 100 Ω 5V 5V 3.5 V VOUT 3.5 V VOUT 1.5 V 1.5 V 0V time 0 0V time 0 tr tf (a) Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e VIN VOUT tpHL (b) tpLH VIN VOUT tpHL tpLH Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e October 3, 2002 EE 121: Digital Design Laboratory Lecture 3 – 16 Power consumption Current flows from power to ground through transistors, but may pause on capacitors (input gates of other CMOS devices). VCC = +5.0 V VCC = +5.0 V (a) Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e (b) 200 Ω > 1 MΩ AC load VOUT = 0 V VIN 100 Ω AC load VOUT VIN IOUT = 0 IOUT > 1 MΩ 100 pF October 3, 2002 100 pF EE 121: Digital Design Laboratory Lecture 3 – 17 Power consumption (2) VCC = +5.0 V VCC = +5.0 V (a) (b) 200 Ω Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e > 1 MΩ AC load VOUT = 5.0 V VIN AC load VOUT VIN IOUT = 0 100 Ω > 1 MΩ 100 pF IOUT 100 pF 2 Power consumption formula: P = CPD · VDD ·f CPD effective capacitance VDD power-supply voltage f number of output transitions per second October 3, 2002 EE 121: Digital Design Laboratory Lecture 3 – 18 Transmission gates EN_L normally complementary A B EN Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e Multiplexers can be built using T-gates: VCC X Z Y S Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e October 3, 2002 EE 121: Digital Design Laboratory Lecture 3 – 19 Transmission gates (2) This circuit uses only 6T compared to 14T for the NAND-NAND circuit: (a) Z (b) X ZP ZP XZP Z F YZ YZ Y XZP Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e F 1 0 1 0 1 0 1 0 1 0 Warning: delays through transmission gates can add up. October 3, 2002 EE 121: Digital Design Laboratory Lecture 3 – 20