SLG59M1721V Layout Guide

advertisement

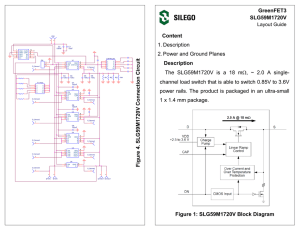

GreenFET3 SLG59M1721V Layout Guide Content 1 1 VDD C2 100nF ON U1 1 2 3 D_Sense1 1 2 3 4 1 C3 100u C4 100u R_Array 1 3 5 7 9 8 7 6 5 VDD GND ON CAP/ILIM D S D S 1 3 5 7 9 S_Sense1 1 C5 100u C6 100u R1 2 4 6 8 10 R2 C7 100nF 2 4 6 8 10 U2 9 1 2 3 4 D_Sense2 ON VDD D D D 8 7 6 5 GND CAP S S S_Sense2 1 1 C8 100nF U3 1 2 3 4 D_Sense3 ON VDD D D 8 7 6 5 GND CAP S S S_Sense3 1 1 C9 100nF U4 9 1 2 3 4 D_Sense4 1 ON VDD D D D 8 7 6 5 GND S S S S_Sense4 1 U5 1 2 3 4 D_Sense5 1 ON VIN VIN VIN 8 7 6 5 GND VOUT VOUT VOUT S_Sense5 1 U6 1 2 D_Sense6 ON D GND S 4 3 R3 R4 Figure 4. SLG59M1721V Connection Circuit 2. Power and Ground Planes CAP/RILIM Description The SLG59M1721V is a 18 m, ~ 2.0 A singlechannel load switch that is able to switch 0.85V to 3.6V power rails. The product is packaged in an ultra-small 1 x 1.4 mm package. D/VIN D/VIN 1 1 S_Sense6 1 1 1 VDD CAP2 GND CAP1 ON1 S2 ON2 S1 D1 D2 1. Description C1 10uF 10 9 8 7 6 1 1 2 3 4 5 S/VOUT S/VOUT Figure 1: SLG59M1721V Block Diagram 2. Power and Ground Planes This layout guide provides some important information about the PCB layout of SLG59M1721V applications. SILEGO FC-TDFN 1x1.4-6L PKG Unit: um 2.1. The VDD pin needs are 0.1uF and 10uF external capacitors to smooth pulses from the power supply. Locate these capacitors close to PIN1. 2.2. The trace length from the control IC to the ON pin should be as short as possible and must avoid crossing this trace with power rails. 2.3. The D/VIN and S/VOUT pins carry significant current. Please note how the D/VIN and S/VOUT pads are placed directly on the power planes in Figure 2. SLG59M1721V Package Dimensions and Recommended Land Pattern Please solder your SLG59M1721V here Figure 3, which minimizes the RDS (ON) associated with long, narrow traces. The D/VIN, S/VOUT and GND pins dissipate most of the heat generated during high-load current condition. The layout shown in Figure 3 is illustrating a proper solution for heat to transfer as efficiently as possible out of the device. 46mm 2.4. Place the power rail ramp capacitor as close as possible to the CAP pin to avoid/reduce the effect of parasitic mount capacitance. 2.5. The GND pin (PIN6) should be connected to GND. 2.6. 2 oz. copper is recommended for higher currents. 28mm Figure 3. SLG59M1721V Evaluation Test Board Note: Evaluation board has D_Sense and S_Sense pads. Please use them only for RDS(ON) evaluation.