A Quantization Noise Suppression Technique for 16Fractional

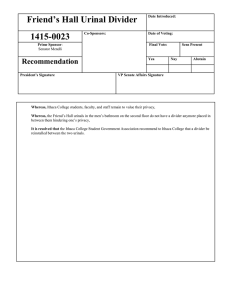

advertisement

2500 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 41, NO. 11, NOVEMBER 2006 A Quantization Noise Suppression Technique for Fractional-N Frequency Synthesizers 16 Yu-Che Yang, Shih-An Yu, Yu-Hsuan Liu, Tao Wang, and Shey-Shi Lu, Senior Member, IEEE 16 Abstract—The first circuit implementation of quantization noise frequency synthefractionalsuppression technique for sizers using reduced step size of frequency dividers is presented in this paper. This technique is based on a 1/1.5 divider cell which can reduce the step size of the frequency divider to 0.5 and thus the reduced step size suppresses the quantization noise by 6 dB. This frequency synthesizer is intended for a WLAN 802.11a/WiMAX 802.16e transceiver. This chip is implemented in a 0.18- m CMOS process and the die size is 1.23 mm 0.83 mm. The power consumption is 47.8 mW. The in-band phase noise of 100 dBc/Hz at 10 kHz offset and out-of-band phase noise of 124 dBc/Hz at 1 MHz offset are measured with a loop bandwidth of 200 kHz. The frequency resolution is less than 1 Hz and the lock time is smaller than 10 s. (16) Index Terms—CMOS RF, delta-sigma , fractional-N frequency synthesizers, frequency dividers, phase-locked loop (PLL), phase noise, quantization noise suppression, WLAN, WiMAX. I. INTRODUCTION P HASE-LOCKED LOOP (PLL)-based frequency synthesizers are used in wireless communication systems. Conventional integer-N frequency synthesizers suffer the fundamental tradeoffs between loop bandwidth and channel spacing. To resolve this problem, fractional- frequency synthesizers are adopted as frequency generators because they offer wide bandwidth with narrow channel spacing, and allow an alternative tradeoff among PLL design constraints for phase noise, lock time, and reference spur [1]–[5]. Since the fractionalfrequency synthesizer is able to generate a fractional division ratio, the output frequency needs not to be an integer multiple of the reference frequency. Therefore, a smaller division ratio can be chosen and results in lower in-band phase noise. A fractional- frequency synthesizer is usually based on a fractional divider composed of a modulator and a frequency divider with integer division ratio. The modulator generates a pseudo-random bit sequence to switch the frequency divider’s division ratio so that the desired fractional division ratio is obtained. However, since the intrinsic moduli of the divider remain Manuscript received January 11, 2006; revised July 12, 2006. This work was supported by the National Science Council under Grant NSC95-2220-E-002015. Y.-C. Yang and S.-S. Lu are with the Department of Electrical Engineering, National Taiwan University, Taipei, Taiwan, 10617, R.O.C. (e-mail: sslu@ntu. edu.tw). S.-A. Yu is with Columbia University, New York, NY 10027 USA. Y.-H. Liu is with Realtek Semiconductor Corporation, Hsinchu 300, Taiwan, R.O.C. T. Wang is with the Department of Electrical Engineering, National Taiwan University, Taipei, Taiwan, 10617, R.O.C. Digital Object Identifier 10.1109/JSSC.2006.883325 integers, they have constant deviations from the desired fractional number, which is so-called quantization error. The quantization error introduces the high-pass quantization noise and degrades the phase noise of the frequency synthesizer [1], [6]. In order to suppress the quantization noise, one can either increase the order of the loop filter, or decrease the loop bandwidth. The former method reduces the phase margin and hence endangers the stability [7], while the latter one obviously conflicts to the original goal of increasing bandwidth by fractional- synthesis. In this paper, we present a fractional- frequency synthesizer with a quantization noise suppression technique. The main idea is to reduce the step size of the frequency divider in the PLL to mod0.5, so that the quantization noise contributed by the ulator can be lowered and consequently the out-of-band phase noise can be reduced. This general idea was originally proposed by Sumi in [8] and [9] and then others [10]–[12], which differ among themselves in the realization of dividers. Based on this concept and our previous work [13], we present the first circuit implementation of this general idea with experimental results and its application to a PLL in this paper. The experimental results agree well with the theoretical prediction which will be detailed in Section II: the out-of-band phase noise contributed modulator is reduced by 6 dB. Moreover, this techby the nique can also co-exist with other quantization noise suppression methods using charge pump current compensation, such as those proposed in [14] and [15] and hence the phase noise can be further suppressed by 6 dB. Note that other researchers have already demonstrated different techniques [16] for the reduction of the quantization noise below that of voltage-controlled oscillator (VCO) noise. In such case, our approach will not help quantization noise performance further. That is, we propose an alternative method for the suppression of phase noise in case that the out-of-band phase noise is still dominated by the quantization noise. modulator adopted in common practice of A reduced commercial frequency synthesizer is used. The hardware of the modulator is reduced by truncating the second and the third stages so that 1/3 die area and 1/3 power consumption of the modulator can be saved. The frequency synthesizer is intended to be applied in the 802.11a WLAN/802.16e WiMAX direct-conversion transceiver using sub-harmonic mixers to avoid the problem of local oscillator (LO) self-mixing in receive as well as LO pulling in transmit [17]. Therefore, the required LO frequency is half of the RF frequency, i.e. 2575 2910 MHz and consequently the tuning range of the synthesizer is designed from 2500 MHz to 3200 MHz to cover this band. 0018-9200/$20.00 © 2006 IEEE YANG et al.: A QUANTIZATION NOISE SUPPRESSION TECHNIQUE FOR FRACTIONAL- FREQUENCY SYNTHESIZERS 2501 Fig. 1. Function block diagram of the implemented frequency synthesizer. This paper is organized as follows. Section II discusses the relationship between quantization level and quantization noise. The circuit blocks of the frequency synthesizer are described in Section III. The experimental results are given in Section IV, and in Section V, we conclude the work. II. QUANTIZATION LEVEL AND QUANTIZATION NOISE A MASH3 fractional- frequency synthesizer utilizes modulator to produce a fractional division ratio of by changing the divider’s modulus among , , , , , , , and , where is the integer modulus of the frequency divider and is the average fractional number generated by the modulator [3]. However, the quantization noise occurs and degrades the total phase noise of the frequency synthesizer since the intrinsic modulus of the frequency divider is still an integer. The power contributed by the spectral density of the phase noise modulator can be derived as [1] a (1) where is the desired division ratio and denotes the average divider output frequency. is the rms spectral density which is the difference between of the quantization noise generated by the the fractional part of and the bit stream modulator. is proportional to the square From the above equation, , which in turn is determined by the step size of value of . Therefore, it is predicted that a divider with a step size of 0.5 will generate 6 dB lower quantization noise than a divider with a step size of 1. For contrast, consider the following situation where a prescaler with constant modulus is put between the VCO and the programmable divider to relax the design of the programmable divider [18], [19]. According to (1), this constant modulus prescaler in conjuction with the programmable divider with step size larger than 1 and cause a raise will lead to in the out-of-band phase noise. To verify this point, we design with different a modulus combiner so that the effects of step sizes can be tested in the same frequency synthesizer (see Section III-D). III. CIRCUIT IMPLEMENTATION A. Architecture The block diagram of the proposed frequency synthesizer is shown in Fig. 1. The loop filter is off-chip so that we can adjust the loop bandwidth to examine the functions of the 1/1.5 divider cell. The whole chip consists of a VCO, a programmable frequency divider with a step size of 0.5, a phase/frequency detector (PFD), a charge pump (CP), a reference input buffer modulator (DSM), a three-wire interface (I/B), a MASH3 control circuit (TWIF), and inter-stage buffers. MUX1, MUX2, and MUX3 are used to change the polarity of the divided VCO 2502 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 41, NO. 11, NOVEMBER 2006 Fig. 2. Schematic of the 1/1.5 divider cell. signal, and then the PFD and the modulator can be triggered at different clock edges to reduce the substrate noise coupling [4]. The frequency range of the frequency synthesizer is 2500–3200 MHz. Because the frequency divider has a wide modulus range of 32–511.5, reference frequencies from 7 to 78 MHz can be used. B. 1/1.5 Divider Cell There are several ways to implement the frequency dividers with moduli having a step size smaller than one, such as the divide-by-2/2.5/3/3.5 circuits described in [2] and [20] or the divide-by-1/1.25/1.5/1.75 circuit in [21]. Dividers with static fractional moduli can also be found in [22] and [23]. Both the divide-by-2/2.5/3/3.5 and the divide-by-1/1.25/1.5/1.75 circuit utilize a 4-phase divide-by-2 circuit to generate quadrature outputs and a phase selector to switch among different phases, but the only difference is that the divide-by-1/1.25/1.5/1.75 circuit requires quadrature input signals. By selecting the outputs with phase differences of 90 /45 , the step size of 0.5/0.25 can be realized. Different from these dividers, we propose a 1/1.5 divider cell. The schematic of the 1/1.5 divider cell is depicted in Fig. 2. The key operating principle of the 1/1.5 divider cell is to trigger the divider on the rising and falling edges of the input signal in turn. For this purpose, two latches (latch1 and latch2 or latch3 and latch4), one (latch2 or latch4) enabled by the positive level and the other (latch1 or latch3) enabled by the negative level of the input signal, are parallel-connected and followed by a multiplexer (MUX1 or MUX2). These three functional blocks form a double-edge-triggered flip-flop (DTFF) [24]. By using the input signal to control latches as well as multiplexers, this architecture may have a potential timing race problem. However, since the multiplexers select the latches that are holding data, the glitches will not occur unless the input-to-multiplexer delay is much larger than the input-to-latch delay. Because both delays are small compared to the time constant of the output load of the latches, the multiplexers can always switch before the latches change their states and hence the timing race problem does not happen under all PVT conditions. Modified from the conventional 2/3 divider cell, the 1/1.5 divider cell also consists of two main parts: the prescaler logic and end-of-cycle logic [25]. The prescaler logic divides the frequency of the input signal by 1 or 1.5 depending on the delay period of the end-of-cycle logic, while the delay time of end-of-cycle logic is based on the state of the two control signals MOD and FB_CTRL. When MOD and FB_CTRL are both high, the 1/1.5 divider cell is in the divde-by-1.5 mode and the prescaler logic swallows half extra period of the input signal due to the delay of the end-of-cycle logic. The timing chart of the 1/1.5 divider cell in the divide-by-1.5 mode is illustrated in Fig. 3(a), and the state diagram is shown in Fig. 3(b). According to Fig. 3(b), no hidden state exists in this architecture. When either MOD or FB_CTRL is low, the output signal of latch1 stays high (low) and the output signal of latch2 stays low (high) and thus the 1/1.5 divider cell simply tracks the input signal, that is, the divider is in the divide-by-1 mode. Although dividing by 1 means that this 1/1.5 divider cell just passes the VCO signal to the following divider chain, which may raise a concern about wasting power and area, this cell has an advantage that quadrature signal generation and phase selector are not required. Accurate quadrature outputs and symmetrical signal paths need careful layout as well as small device mismatches, which is especially difficult for the first divider cell. Because the first divider cell operates at the highest , small mismatches lead to significant phase frequency errors. Phase errors in phase switching dividers will induce undesired fractional spurs and degrade the performance of the frequency synthesizer. The detailed discussion of this phenomenon can be found in [26]. YANG et al.: A QUANTIZATION NOISE SUPPRESSION TECHNIQUE FOR FRACTIONAL- Fig. 3. (a) Timing chart of 1/1.5 divider cell in the divide-by-1.5 mode. (b) States diagram of the 1/1.5 divider cell in the divide-by-1.5 mode. Another important issue of the 1/1.5 divider cell is the duty cycle of the input signal. According to [9] and [11], the fractional spurs appear at twice the fractional frequency in a fractional frequency synthesizer whose frequency divider has moduli with a step size of 0.5, assuming that the duty cycle of the input signal is 50%. To illustrate this point, please refer to Fig. 4(a) and (b). In Fig. 4(a), a frequency divider with step size of 1 generating a fractional modulus of 2.25 by switching between 2 and 3 is shown. Since the modulus repeats every . four reference period, the fractional spurs locate at As for the frequency divider with step size of 0.5 [Fig. 4(b)], when a fractional modulus of 2.25 is generated, the modulus is switched between 2 and 2.5, and the modulus repeats every two reference period. Therefore, the fractional spurs locate at , i.e. twice the fractional frequency of . However, if the input signal is not exactly 50% in duty cycle, then the fractional spurs will be shifted back to the fractional frequency. The reason is illustrated in Fig. 4(c). Because the frequency divider with a step size of 0.5 is double-edge triggered, the non-50% duty cycle causes period mismatch in the two divide-by-2.5 period, and thus makes the total period extend to four reference cycle. Consequently, the fractional spurs move . Nevertheless, the problem of to a frequency offset of fractional spurs caused by this technique is not worse than that by the conventional frequency divider with step size of 1 theoretically and experimentally (see Fig. 19). The logic functions in the 1/1.5 divider cell are all implemented with the source-coupled-logic (SCL) configuration. FREQUENCY SYNTHESIZERS 2503 Fig. 4. Illustration of fractional spurs. (a) Frequency divider with step size = 1. (b) Frequency divider with step size = 0:5 and input duty cycle is 50%. (c) Frequency divider with step size = 0:5 and input duty cycle is not 50%. Fig. 5. Schematic of the combined SCL AND-latch. Since SCL has the properties of keeping FETs biased in saturation region, it is more suitable for high frequency operation. In order to further reduce the propagation delay, the AND gates in the 1/1.5 divider cell are merged into the latches. The schematic of the combined AND-latch is shown in Fig. 5 [25], where the 2504 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 41, NO. 11, NOVEMBER 2006 Fig. 6. Schematic of the programmable frequency divider. transistors’ widths are labeled and the transistors’ lengths are all 0.18 m. The post-layout simulations show the 1/1.5 divider cell using the combined AND-latch can work over 4.6 GHz, whereas with AND gates and latches separated, the 1/1.5 divider cell can only operate under 3.5 GHz. However, the output DC level of the SCL AND-latch in cascode configuration will be higher than that of a single SCL latch and thus it is a common practice to use a level shifter. In our work, no level shifter is added here in order to save power consumption. Instead, the DC input level of the multiplexer is designed intentionally to be high enough so that the multiplexer can operate properly with the SCL AND-latch. It is found experimentally (see Fig. 18) that this divider cell can function well over all process/temperature corners, albeit modifications of biasing conditions are is increased. (The bias voltage can be necessary when changed by varying the off-chip biasing resistor.) C. Programmable Frequency Divider The programmable divider is shown in Fig. 6 and is similar to the divider proposed in [25]. It consists of a 1/1.5 divider cell followed by eight divide-by-2/3 stages and a control circuit (including a MUX, a decoder, and three OR gates) that can effectively shorten the length of the divider thereby extending the range of the divider. In this work, with a 2-bit modulus extension signal, the modulus range can be extended to 32 511.5 with a step size of 0.5. Fig. 7 shows the output waveforms of the 1/1.5 divider cell comparing to a typical 2/3 divider cell when they are connected to a chain of 2/3 divider cells in a programmable frequency divider. Note that all the voltage signals shown in Fig. 7 are in the differential mode. Shown in Fig. 7(a), when the feedback control signal FB_CTRL is high, the output signal Fout1 of the 1/1.5 divider cell is delayed by half period of the input signal Fin, while in Fig. 7(b), Fout1 of the 2/3 divider cell is delayed by one period of the input signal. To lower the power dissipation, only the first three bits (one 1/1.5 divider cell and two 2/3 divider cells) of the programmable frequency divider are realized with SCL configuration, whereas the remaining six bits are implemented in CMOS logic and synthesized by digital building blocks. D. Reduced Modulator With a Modulus Combiner A 24-bit digital third-order modulator is adopted to generate the pseudo-random number bit stream. Cooperating with modulator can produce the proposed 1/1.5 divider cell, the the output bit stream with an average between 0 and 0.5 so that . With a refthe step size of the frequency divider is erence frequency of 33 MHz, the resulting frequency resolution MHz Hz. of the frequency synthesizer is modulator adopted in common In this work, a reduced practice of commercial frequency synthesizer is used and its block diagram is shown in Fig. 8. A conventional digital modulator is a cascade of three accumulators of MASH3 the same bit size. However, in practice, the second and third stages need not to have so many bits as the first stage does to deal with the quantization noise. Therefore, we can truncate the second and third stages to 16 bits and 8 bits, respectively. The comparison of the reduced (the first accumulator is 24 bits while the second and third accumulators are 16 bits and 8 bits, respectively) and conventional (the second and third accumulators are not truncated, i.e. all the three accumulators modulators using the simulation results is are 24 bits) shown in Fig. 9, which indicates that the performance of the modulator is not degraded, yet 1/3 chip area and reduced modulator can be saved. 1/3 power consumption of the Note that the 1/3 hardware is not redundant. Deliberate removal of it will add error. However, experimentally we found that the error is so small that it does not degrade the quantization noise. To verify that the reduction of the quantization level can indeed suppress the quantization noise, a modulus combiner that can change the quantization level of the frequency divider is fractional- frequency synthesizer, designed. In a typical modulator are simply the modulation bits generated by the summed up with the integer modulus to control the division ratio of the frequency divider. However, in our system, if the YANG et al.: A QUANTIZATION NOISE SUPPRESSION TECHNIQUE FOR FRACTIONAL- FREQUENCY SYNTHESIZERS 2505 Fig. 7. Simulation results of the programmable frequency divider. (a) Output waveforms of the 1/1.5 divider cell. (b) Output waveforms of the 2/3 divider cell. modulation bits are added with the integer modulus, the quantization level will be 0.5, which implies that we still need a function block that can multiply the quantization level by 2, or equivalently, shift the modulation bits by 1 divider cell, to exon phase noise. For this amine the effect of the step size of purpose, a modulus combiner that can shift the modulated bits of the frequency divider is designed. The modulated bits can be , chosen to be divider cell 1, 2, and 3 quantization level , divider cell 3, divider cell 2, 3, and 4 quantization level , or divider cell 4, 5, and 4, and 5 quantization level 2506 Fig. 8. Block diagram of the reduced IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 41, NO. 11, NOVEMBER 2006 16 modulator. Fig. 10. Schematic of the VCO. Fig. 9. Simulated phase noise of the reduced and conventional modulator. 16 6 quantization level . Accordingly, we can compare the phase noises with different quantization levels in the same chip. E. VCO Fig. 10 depicts the schematic of the LC-VCO. The core of the differential oscillator is formed by two complementary nMOS and pMOS devices for generating the negative transconductance of the VCO. The and attached to the LC tank tank consists of a differential high- (18 at 3 GHz) inductor, which is a fully symmetric spiral inductor designed for differential excitation [27], and two pMOS varactors. To have a wide tuning range and a small VCO gain [28], a 3-bit binary weighted capacitors array is connected to the LC tank for coarse tuning. Fig. 11. Transfer curves of the VCO. YANG et al.: A QUANTIZATION NOISE SUPPRESSION TECHNIQUE FOR FRACTIONAL- FREQUENCY SYNTHESIZERS 2507 Fig. 12. Schematic of the charge pump. Because of their high quality factors, metal–insulator–metal (MIM) capacitors are chosen to form the capacitors array, fF, fF, and and the capacitances are fF, respectively. To have the same quality factor for each branch in the array, the sizes of the nMOS switches are also : : 1:2:4. Fig. 11 shows the VCO tuning scaled as curves, where the VCO gain is approximately 100 MHz/V. F. PFD, Charge Pump, and Loop Filter (LPF) The PFD adopted in this frequency synthesizer is a traditional tri-state PFD [29]. The schematic of the charge pump is – are put at the sources illustrated in Fig. 12. Switches of current mirrors to improve the switching speed and keep the switching noise low [4]. The output current sources are ) to increase output formed by cascaded transistors ( – and can be programmed impedance and the control bit to have three different output currents. The transistor size ratio of these three branches is 1:3:4 and the corresponding output currents can be 100 A, 400 A, and 800 A, respectively. The variable charge-pump current provides an alternative way to change the loop bandwidth of the PLL. A third-order off-chip passive loop filter is used as shown in pF, Fig. 13. The design parameters are as follows: pF, pF, k , and k . Given that the VCO gain is 100 MHz/V, the divider modulus is around 85, and the charge pump current is 400 A, the resulting PLL bandwidth is approximately 200 kHz. IV. EXPERIMENTAL RESULTS The proposed frequency synthesizer was implemented in a 0.18- m CMOS process. The microphotograph of the chip is Fig. 13. Schematic of the loop filter and the design parameters. shown in Fig. 14. The die area is 1.23 mm 0.83 mm (1 mm ) excluding the measurement pads. The supply voltage is 2.3 V for VCO (The VCO does not oscillate below 2.3 V) and 2 V for the other circuits and the total power consumption is 47.8 mW. All control signals are supplied through the three-wire serial interface, and the reference frequency used is 33 MHz. The measured phase noises at the same carrier freand quency of 2813 MHz with quantization level are shown in Fig. 15. For a fracquantization level tional- frequency synthesizer, the out-of-band phase noise 2508 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 41, NO. 11, NOVEMBER 2006 Fig. 14. Microphotograph of the frequency synthesizer. Fig. 16. Measured phase noise profiles with the same out-of-band phase noise. Fig. 15. Measured phase noise profiles with the same loop bandwidth. Fig. 17. Measurement results of phase noises with different quantization levels. is dominated either by the VCO or by the modulator [6]. According to our measurement results, the phase noises of the free-running VCO are 129 dBc/Hz at 1 MHz offset and 142 dBc/Hz at 4 MHz offset, whereas in Fig. 15 the phase noises are 124 dBc/Hz and 135 dBc/Hz at 1 MHz ). Thus, the and 4 MHz offset (with quantization level modout-of-band phase noise is now dominated by the ulator. Clearly from Fig. 15, with the help of the proposed 1/1.5 divider cell, the out-of-band phase noise contributed by modulator is indeed reduced by 6 dB (from 129 to the 135 dBc/Hz at 4 MHz offset), consistent with the theoretical prediction. The 6 dB phase noise reduction effectively allows us to design this synthesizer with a wider loop bandwidth. To verify this, we adjust the loop bandwidth so that the out-of-band is the same as that with phase noise with quantization level quantization level . Fig. 16 shows the experimental result. When the out-of-band phase noises are the same in both quantization levels, the 1/1.5 divider widens the loop bandwidth. As we mentioned in Section III, the modulus combiner can change the quantization level among 0.5, 1, 2, and 4. The mea- surement results of phase noises with these four quantization levels are shown in Fig. 17. It can be observed that the four curves have the same in-band phase noise (except for the one , whose quantization noise is too with quantization level high to be suppressed below the in-band phase noise floor.), whereas the out-of-band phase noise is 6 dB higher as the quantization level is doubled. From these experimental results, we know that when a fixed modulus prescaler is used in front of the programmable divider, the quantization level is increased and hence the quantization noise grows in proportion to the constant modulus. The performances over different temperature/chips/supply voltages are also tested. The chip was measured from 0 C to 100 C and the measurement results are shown in Fig. 18(a). It can be observed that the in-band phase noise grows as temperature increases, but the out-of-band phase noise can still have a 6 dB improvement after the quantization level is halved. Notice that when the temperature is higher than 75 C, the out-of-band phase noise is dominated by the VCO, as a result, the improve- YANG et al.: A QUANTIZATION NOISE SUPPRESSION TECHNIQUE FOR FRACTIONAL- FREQUENCY SYNTHESIZERS 2509 Fig. 19. Measurement results of fractional spurs. TABLE I PERFORMANCE SUMMARY Fig. 18. (a) Measured phase noises at different temperatures. (b) Measured phase noises for 10 chips. ment is smaller than 6 dB. Fig. 18(b) shows the performance of . The ten different chips measured with quantization level in-band phase noise varies from 105 dBc/Hz to 93 dBc/Hz at 10 kHz offset and the out-of-band phase noise has a variation of 5 dB, while the reduction of the quantization level can still have a 6 dB improvement. (The curves with quantization level are not shown for clarity.) The frequency synthesizer was also evaluated at different power supply voltages ranging from 2 V to 3 V (2.3 V to 3 V for VCO). The increment in supply voltage does not change the improved amount of the phase noise out of the loop bandwidth, but increases the power consumption from 47.8 mW to 112 mW. Fig. 19 shows the measured fractional spurs of the frequency synthesizer. (Since the duty cycle of the VCO output is not perfectly 50%, the fractional spurs still locate at the fractional frequency as has been explained in Section III-B and Fig. 4.) In Fig. 19, the x-axis represents the fractional part setting. For example, 16 means the fractional part is 16/128, and thus from Fig. 19, the fractional spurs locates at 4.125 MHz 33 MHz offset from the carrier frequency are 74 dBc. When the fractional frequency is larger than 6.18 MHz, the fractional spurs are smaller than the noise floor and cannot be measured. That is why the data are only collected to 24/128. The experimental results are summarized in Table I. V. CONCLUSION In this paper, a quantization noise suppression technique for fractional- frequency synthesizers is presented and verified in 0.18- m CMOS technology. The experimental results 2510 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 41, NO. 11, NOVEMBER 2006 show the out-of-band phase noise contributed by the modulator is reduced by 6 dB in the situation where the out-of-band phase is dominated by the quantization noise. As out-of-band phase noise reduced, a higher loop bandwidth can be used. The measurement results show 100 dBc/Hz in-band phase noise within the loop bandwidth of 200 kHz, and 124 dBc/Hz and 144 dBc/Hz out-of-band phase noise at 1 MHz and 10 MHz offset frequency. The lock time is less than 10 s. ACKNOWLEDGMENT The authors would like to thank the National Chip Implementation Center for IC fabrication, and the National Nano-Device Laboratory (NDL) for measurement support. Helpful discussions from Dr. Guo-Wei Huang at NDL and Prof. Hung-Wei Chiu at National Taipei University of Technology are also greatly appreciated. REFERENCES [1] T. A. Riley, M. Copeland, and T. Kwasniewski, “Delta-sigma modulation in fractional-N frequency synthesis,” IEEE J. Solid-State Circuits, vol. 28, no. 5, pp. 553–559, May 1993. [2] M. Perrot, T. Tewksbury, and C. Sodini, “A 27-mW CMOS fractional-N frequency synthesizer using digital compensation for 2.5-Mb/s GFSK modulation,” IEEE J. Solid-State Circuits, vol. 32, no. 12, pp. 2048–2060, Dec. 1997. [3] T. P. Kenny, T. A. D. Riley, N. M. Filiol, and M. A. Copeland, “Design and realization of a digital modulator for fractional-N frequency synthesis,” IEEE Trans. Veh. Technol., vol. 48, no. 2, pp. 510–521, Mar. 1999. [4] W. Rhee, B. Song, and A. Ali, “A 1.1-GHz CMOS fractional-N frequency synthesizer with a 3-b third-order modulator,” IEEE J. Solid-State Circuits, vol. 35, no. 10, pp. 1453–1460, Oct. 2000. [5] H. Lee, J. Cho, K. Lee, I. Hwang, T. Ahn, K. Nah, and B. Park, “A fractional-N frequency synthesizer using a wide-band integrated VCO and a fast AFC technique for GSM/GPRS/WCDMA applications,” IEEE J. Solid-State Circuits, vol. 39, no. 7, pp. 1164–1169, Jul. 2004. [6] M. H. Perrot, M. D. Trott, and C. G. Sodini, “A modeling approach for fractional-N frequency synthesizer allowing straightforward noise analysis,” IEEE J. Solid-State Circuits, vol. 37, no. 8, pp. 835–844, Aug. 2002. [7] H. Huh, Y. Koo, K. Lee, Y. Ok, S. Lee, D. Kwon, J. Lee, J. Park, K. Lee, D. Jeong, and W. Kim, “A CMOS dual-band fractional-n synthesizer with reference doubler and compensated charge pump,” in IEEE ISSCC Dig. Tech. Papers, Feb. 2004, pp. 100, 516. [8] Y. Sumi, S. Obote, K. Tsuda, K. Syoubu, and Y. Fuki, “Novel fractional-N PLL frequency synthesizer with reduced phase error,” Proc. IEEE Asia Pacific Conf. Circuits and Systems, pp. 45–48, Nov. 1996. [9] Y. Sumi, “PLL with variable (N+1/2) frequency dividing ratio,” European Patent EP1020994, Jul. 2000. [10] K. Pierce V, “Frequency synthesizer using double resolution fractional frequency division,” W. O. patent WO9922449, May 1999. [11] H. Morihito, “Fractionally-divided PLL frequency synthesizer,” Japan patent JP2002198812, Jul. 2002. [12] D. N. Behli and T. Robert, “Fractional-r frequency synthesizer,” W.O. patent WO03039002, May 2003. [13] Y.-C. Yang, S.-A. Yu, T. Wang, and S.-S. Lu, “A dual-mode truly modular programmable fractional divider based on a 1/1.5 divider cell,” IEEE Microw. Wireless Compon. Lett., vol. 15, no. 11, pp. 754–756, Nov. 2005. [14] E. Temporiti, G. Albasini, I. Bietti, R. Castello, and M. Colombo, “A 700 kHz bandwidth sigma-delta fractional synthesizer with spurs compensation and linearization technique for WCDMA applications,” IEEE J. Solid-State Circuits, vol. 39, no. 9, pp. 1446–1454, Sep. 2004. [15] S. Pamarti, L. Jansson, and I. Galton, “A wideband 2.4-GHz delta-sigma fractional-N PLL with 1-Mb/s in-loop modulation,” IEEE J. Solid-State Circuits, vol. 39, no. 1, pp. 49–62, Jan. 2004. 16 16 61 [16] S. Meninger and M. Perrot, “Bandwidth extension of low noise fractional-N synthesizers,” in IEEE RFIC Symp. Dig. Papers, 2005, pp. 211–214. [17] R. Magoon et al., “A single-chip quad-band (850/900/1800/1900 MHz) direct conversion GSM/GPRS RF transceiver with integrated VCOs and fractional-N synthesizer,” IEEE J. Solid-State Circuits, vol. 37, no. 12, pp. 1710–1720, Dec. 2002. [18] W.-Z. Chen and J.-T. Wu, “A 2-V, 1.8-GHz BJT phase-locked loop,” IEEE, J. Solid-State Circuits, vol. 34, no. 6, pp. 784–789, Jun. 1999. [19] S. T. Lee, S. J. Fang, D. J. Allstot, A. Bellaouar, A. Fridi, and P. Fontaine, “ A 1.5V 28mA fully-integrated fast-locking quad-band GSM-GPRS transmitter with digital auto-calibration in 130nm CMOS,” in IEEE ISSCC Dig. Tech. Papers, Feb. 2004, pp. 188, 521. [20] C.-W. Lo and H. C. Luong, “A 1.5-V 900-MHz monolithic CMOS fast-switching frequency synthesizer for wireless applications,” IEEE J. Solid-State Circuits, vol. 37, no. 4, pp. 459–470, Apr. 2002. [21] A. M. Fahim and M. I. Elmasry, “A wideband sigma-delta phase-locked loop modulator for wireless applications,” IEEE Trans. Circuits Syst. II: Analog Digit. Signal Process., vol. 50, no. 2, pp. 53–62, Feb. 2003. [22] R. van de Beek, R. Leenaerts, and G. van der Weide, “A fast-hopping single-PLL 3-band UWB synthesizer in 0.25 m SiGe BiCMOS,” in Proc. ESSCIRC, Sep. 2005, pp. 173–176. [23] Y. Moon, S.-H. Lee, and D. Shim, “A divide-by-16.5 circuit for 10-Gb Ethernet transceiver in 0.13-m CMOS,” IEEE J. Solid-State Circuits, vol. 40, no. 5, pp. 1175–1179, May 2005. [24] R. Hossain, L. D. Wronski, and A. Albicki, “Low power design using double edge triggered flip-flops,” IEEE Trans. Very Large Scale Integrat. (VLSI) Syst., vol. 2, no. 6, pp. 261–265, Jun. 1994. [25] S. Vaucher, I. Ferencic, M. Locher, S. Sedvallson, U. Voegeli, and Z. Wang, “A family of low-power truly modular programmable dividers in standard 0.35-m CMOS technology,” IEEE J. Solid-State Circuits, vol. 35, no. 7, pp. 1039–1045, Jul. 2000. [26] M. A. El Sheikh and A. Hafez, “Phase mismatch in phase switching frequency dividers,” in IEEE Int. Conf. Microelectronics, Dec. 2003, pp. 106–109. [27] M. Danesh and J. R. Long, “Differentially driven symmetric microstrip inductors,” IEEE Trans. Microw. Theory Tech., vol. 50, no. 1, pp. 332–341, Jan. 2002. [28] A. D. Berny, A. M. Niknejad, and R. G. Meyer, “A 1.8-GHz LC VCO with 1.3-GHz tuning range and digital amplitude calibration,” IEEE, J. Solid-State Circuits, vol. 40, no. 4, pp. 909–917, Apr. 2005. [29] B. Razavi, Design of Analog CMOS Integrated Circuits. New York: McGraw-Hill, 2001. 61 Yu-Che Yang was born in Taipei, Taiwan, R.O.C, in 1980. He received the B.S. degree in electrical engineering from National Taiwan University, Taipei, Taiwan, in 2002, where he is currently working toward the Ph.D. degree in electronic engineering. His research interests include frequency synthesizers, mixed-signal integrated circuits, and radio-frequency integrated circuits for wireless communications. Shih-An Yu was born in Taipei, Taiwan, R.O.C., in 1976. He received the B.S. and M.S. degrees in electrical engineering from National Taiwan University, Taipei, Taiwan, in 1999 and 2001, respectively. During 2001 to 2003, he worked on frequency synthesizers and other mixed-mode/RF systems for mobile phone and WLAN applications in VIA technology. During 2003 to 2005, he worked on biosensor networks in several research projects held by National Taiwan University and the government. He is currently pursuing the Ph.D. degree at Columbia University, New York, and collaborating with Bell Labs. His current research interests are low-voltage, low-power, and high-speed systems. YANG et al.: A QUANTIZATION NOISE SUPPRESSION TECHNIQUE FOR FRACTIONAL- Yu-Hsuan Liu was born in Kaohsiung, Taiwan, R.O.C., in 1981. She received the B.S. and M.S. degrees in electrical engineering from National Taiwan University, Taipei, Taiwan, in 2003 and 2005, respectively. She currently works at Realtek Semiconductor Corporation as an R&D Engineer. Her research interests include RF systems and RFIC design for wireless communication systems. Tao Wang was born in Taipei, Taiwan, R.O.C., in 1980. He received the B.S. degree from Chang Gung University, Taoyuan, Taiwan, in 2002, and the M.S. degree from National Taiwan University, Taipei, Taiwan, in 2004, both in electronics engineering, and is currently working toward the Ph.D. degree in electronics engineering at National Taiwan University. His research interests are in the areas of radio-frequency integrated circuits and monolithic microwave integrated circuits. FREQUENCY SYNTHESIZERS 2511 Shey-Shi Lu (S’89–M’91–SM’99) received the B.S. degree from National Taiwan University, Taiwan, R.O.C., in 1985, the M.S. degree from Cornell University, Ithaca, NY, in 1988, and the Ph.D. degree from the University of Minnesota at Minneapolis-St. Paul in 1991, all in electrical engineering. He joined the Department of Electrical Engineering, National Taiwan University, in August 1991 as an Associate Professor and was promoted to full Professor in 1995. His current research interests are in the areas of radio-frequency integrated circuits (RFIC)/monolithic microwave integrated circuits (MMIC) and MEMS-RF electronics.