mukherjee_tonmoy_s_201005_phd

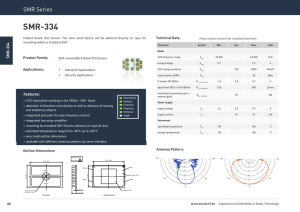

advertisement