IJDI-ERET

INTERNATIONAL JOURNAL OF DARSHAN INSTITUTE ON

ENGINEERING RESEARCH & EMERGING TECHNOLOGIES

Vol. 4, No. 1, 2015

www.ijdieret.in

(Research Article)

Design, Implementation and Comparison of 6-Bit 300MSPS

Current Steering Digital-to-Analog Converters

Khushali A. Shah1*, Mihir V. Shah2, Naresh P. Patel3

1

P G Scholar, Department of Electronics and Communication Engineering, Vishwakarma Government Engineering College, Chandkheda, Ahmedabad.

Associate Professor, Department of Electronics and Communication Engineering, Vishwakarma Government Engineering College, Chandkheda, Ahmedabad.

3

Assistant Professor, Department of Electronics and Communication Engineering, Vishwakarma Government Engineering College, Chandkheda, Ahmedabad.

2

Abstract

Scaling in CMOS technology becomes a great challenge to the analog designer, as design complexity increases with increase

in shrinking. Digital-to-Analog Converters are one of the crucial modules of analog blocks facing high performance demand. In

this paper, Digital-to-Analog Converter is designed with different current steering architectures like, binary weighted,

thermometer-coded (unary), segmented. Also, these architectures are implemented and compared with different parameters. The

speed of these 6-bit DACs was 300MSPS. The maximum current was set 0.3mA and maximum voltage was set 15mV. So, for

6-bit, LSB current was set as 4.88uA and LSB voltage was set as 0.244mV by connecting 3.3V supply voltage. The load was

connected as 50 ohm. Ngspice26 simulations with the 0.18-μm complementary metal-oxide semiconductor technology were

used.

Keywords: Binary weighted; current steering; Segmented; Thermometer DAC.

1.

Introduction

The data available in the real world are in analog form, but

this analog data storage procedure is more complex compared

to the digital data storage procedure. Following are the

benefits of digital data storage: 1) digital data storage requires

less memory compared to analog data 2) digital data are less

noisy and 3) they provides excellent encryption and safety

features. Thus, from a communication point of view, we use

analog to digital converter at transmitter side and Digital to

Analog Converter at the receiver side. DAC is a useful

building block in many-application because it represents the

interface between the real world analog signal and the Digital

Signal Processors.

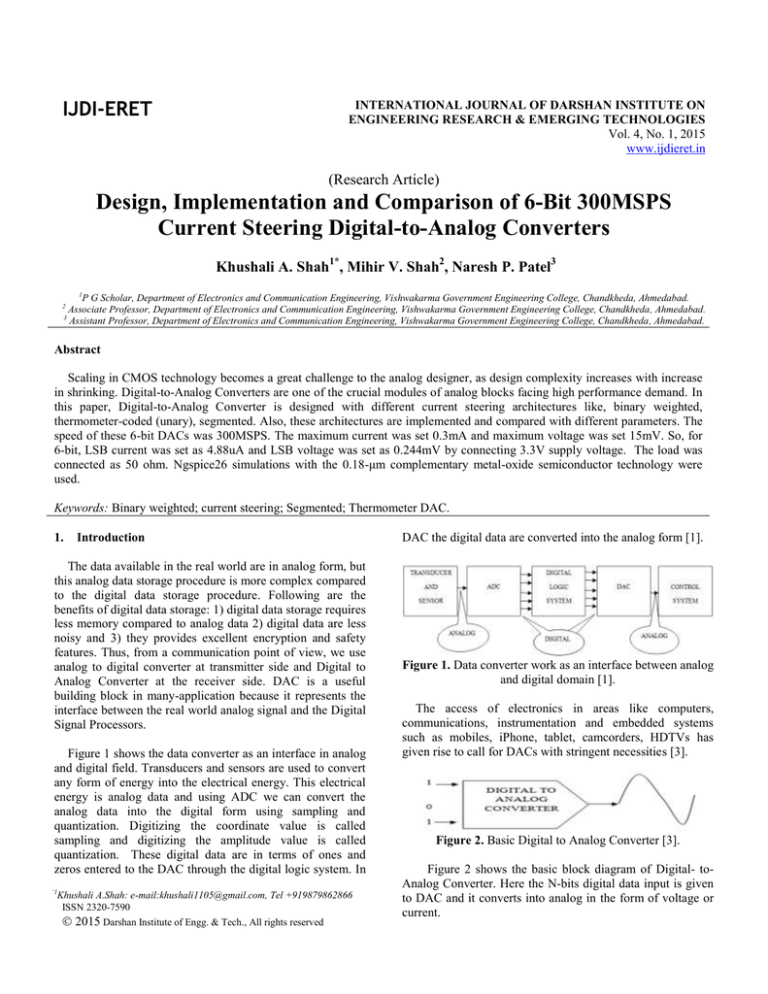

Figure 1 shows the data converter as an interface in analog

and digital field. Transducers and sensors are used to convert

any form of energy into the electrical energy. This electrical

energy is analog data and using ADC we can convert the

analog data into the digital form using sampling and

quantization. Digitizing the coordinate value is called

sampling and digitizing the amplitude value is called

quantization. These digital data are in terms of ones and

zeros entered to the DAC through the digital logic system. In

11

Khushali A.Shah: e-mail:khushali1105@gmail.com, Tel +919879862866

ISSN 2320-7590

2015 Darshan Institute of Engg. & Tech., All rights reserved

DAC the digital data are converted into the analog form [1].

Figure 1. Data converter work as an interface between analog

and digital domain [1].

The access of electronics in areas like computers,

communications, instrumentation and embedded systems

such as mobiles, iPhone, tablet, camcorders, HDTVs has

given rise to call for DACs with stringent necessities [3].

Figure 2. Basic Digital to Analog Converter [3].

Figure 2 shows the basic block diagram of Digital- toAnalog Converter. Here the N-bits digital data input is given

to DAC and it converts into analog in the form of voltage or

current.

International Journal of Darshan Institute on Engineering Research and Emerging Technology

Vol. 4, No. 1, 2015, pp. 16-20

Here, an input N-bit digital word (b1, b2... BN) has a

value Bin has given by

3. Current steering DAC

The current steering has become more popular nowadays

due to its property to provide relatively huge currents (10 to

20mA) to 50Ω load without buffering. Moreover, the speed

of a current-steering converter is determined by the capability

to drive the gates of the switches. Also, sample rates of

several hundreds of millions of samples per second can be

achieved using current steering. [2], [12].

There are three types of current steering:

1) Binary weighted

2) Unary

3) Segmented

Where, bi is a binary digit, like 0 or 1. The bit b 1 is the

most significant bit (MSB) and bN is the least significant bit

(LSB) [3], [9], [14].

2. Literature Review

Hongming Chenl , Xiaoyuan Chen and Yuhua Chengl

designed ,12-bit 80MSPS 3.3V dual channel DAC using a

voltage driver with large output swing range, lead to a

smaller output glitch and operated at higher output

voltage. Segmented architecture is used to combine high

conversion rate and high resolution. As segmented design has

capability of driving resistive loads without any buffers

like operational

amplifiers, suitability

for

CMOS

implementation and consumes low power in comparison

with others. Dummy decoder was used to equalize the delay

in binary weighted. To minimize the timing error, a latch was

used just before the switch transistor of each current source

[4]. Elnaz Ansari and David D. Wentzloff presented a lowpower 12-bit, 250MS/s DAC implemented with standard

digital design flows and automatic place and route (APR). In

order to increase the operating speed of the DAC, multiple

pipeline stages were placed along the signal path. A digital

controller manages the tasks like reading/writing, into/from

on-chip look-up-tables (LUT), defining the required number

of pipeline stages, and setting the control bits that select

different paths for the input signals and the clock. Current

steering cells divided into three banks. Tri-state spare DAC

cells are used for calibration purposes. The DSP measures the

output voltages of the DAC, compared with the target values,

and adjusted the LUTs accordingly to improve its

performance [5]. Lei Jianming, Gui Hanshu, and Hu Beiwen

introduced a design with low cross point switch driver and a

special dummy switch, to decrease glitch and increase the

. The current cells were designed with PMOS because PMOS

made in the N-well can avoid the 1/f (flicker) noise

interference. A dummy switch was used to reduce charge

injection and the clock feed-through effect [6]. As clock

varies from low to high at that time, the dummy switch

absorbs the charges, and as a result reduces the output glitch

[13]. Seyed Javad Azhari, Khalil Monfaredi and Salar Amiri

used ascade design in the current cell to increase the output

impedance and reduce the sensitivity of DAC to output load

variations. One significant weakness which appeared for nano

currents was the glitch problem caused by clock feed through,

introduced by switching clock pulse and digital inputs.

Complementary transmission gate switches and a deglitch

circuit were used to reduce the glitch and feed through errors

[7].

3.1 Binary weighted DAC: Figure 3 shows Binary-weighted

style uses current source in each branch to produce the analog

signal. The value of the current source in nth branch is 2nI

where I is the value of unit current source. The main benefit

of binary-weighted DAC is its least area because it does not

require any extra decoding circuitry.

Figure 3. Binary weighted Digital to Analog Converter [9].

But, this arrangement does not guarantee monotonicity

because sometimes by changing 1 LSB in the input code (for

example from 011 to 100) the output can change more than 1

LSB (and for a short time it could be 111) results in a large

glitch energy. The glitch in binary-weighted is relative to the

number of switches [8], [9], [12].

3.1 Thermometer-coded DAC(unary)

Figure 4. Thermometer coded DAC [9].

Figure 4 shows, equal amount of current in every branch,

which is called “Unit-Element Array”. In this structure, with

1 LSB change in the input binary code just one additional

17

International Journal of Darshan Institute on Engineering Research and Emerging Technology

Vol. 4, No. 1, 2015, pp. 16-20

current source is switched on or off depending on code

change. Thus, it promises monotonicity. Another benefit of

thermometer-coded DAC over binary-weighted DAC is

improved matching property of transistors. In binaryweighted the matching ratio is suitable to binary weights, and

it must be an almost exact value as several errors in matching

is multiplied using binary weights. One more advantage is

that the glitch is approximately zero, like in the binaryweighted; it is always relative to 1 LSB. The main weakness

of thermometer-coded DAC is that binary-to-thermometer

decoder is needed; thus its area is larger than binary-weighted

DAC and is not used for resolutions higher than 8 bits [8],

[9].

repelled channel charge instead of being transported to the

output [11]. VB1 and VB2 (biased voltages) are applied to

keep current source transistors in the saturation region.

4.2 6-bit Thermometer-coded DAC(unary): Figure 6 shows 6bit thermometer-coded DAC. In this design, row decoder and

column decoder are used to convert binary code to

thermometer code. Here, 3-bit binary code to 7-bit

thermometer decoder is used. The outputs of this decoder are

connected to the latch and outputs of latch are connected to

the switching transistors of unit current source. In unary

design, 2n -1 unit current sources are used, where; n is the

number of bits [10], [11]. There are 63 cells are used in the

current source matrix as shown in figure. 63 current sources

had the same value as it was for 1LSB. Thus, for 2LSB

connect two 1LSB sources, for 3LSB connect four 1LSB

sources... and so on. In figure, x indicated don’t care, 1

indicated current source for B0 bit, 2 indicated current

sources for B1 bit..., and so on. Also AND and OR logic

gates are used to switch on current sources such that when

next column was ON then previous column was also staying

ON condition.

3.2: Segmented DAC: Segmented DAC combines the rewards

of both binary-weighted and thermometer-decoded structures

jointly. In this technique, the input binary code is separated

into 2 segments. In MSB segment, where accuracy is

significant, thermometer-coding is used. Binary-weighted

structure is used in LSB segment to shrink the area of the

chip. Occasionally, even these segments are separated into

subsections and different strategies are used in each segment.

This is called a “Multi-segmented” DAC [8], [9].

4. Current steering DAC design

4.1 6-bit Binary weighted DAC:

Figure 5. 6-bit Binary weighted DAC

Figure 6. 6-bit Thermometer-decoded DAC

Figure 5 shows 6-bit binary weighted DAC. B0-B5 input

binary bits are applied to the switches. Depend on the

position of switches (ON/OFF) current flow from current

source to the load resistor. Here PMOS is used for designing

a current source, because using PMOS will give a lower 1/f –

noise due to lower mobility of holes but a higher thermal

noise level. Also,(1/f) flicker noise is inversely proportional

to the WL. PMOS has high WL compare to NMOS. An ideal

current source should have infinite output impedance. For

that reason, ascade transistors are used to increase the

output resistance; hence the effects of the nonzero channel

length modulation are reduced. To reduce the effect of the

channel charge dummy transistors are used. Actually the

dummy transistor operates as a capacitor which absorbs the

4.3 6-bit Segmented DAC: In segmented architecture, both

binary weighted DAC and thermometer coded DAC are

combined. 2-bit LSB use binary weighted structure and 4-bit

MSB use thermometer-coded structure. In thermometercoded, 2-bit are connected to row decoder and another 2-bit

connected to the column decoder with 2-bit binary to 3-bit

thermometer decoder. The latch is used for synchronization

purpose. The current flowing from binary

thermometer decoded combined in load.

18

weighted and

International Journal of Darshan Institute on Engineering Research and Emerging Technology

Vol. 4, No. 1, 2015, pp. 16-20

5. Simulation of Results and Analysis

Ngspice 26 with 0.18um technology used to design Digitalto-Analog Converter. Origin 8 is used for plotting graphs.

INL states the variation from the ideal line to actual line and

DNL express how much variation in output level between

two adjacent code deviates from the ideal LSB step.

Monotonicity means with increases in input, an output should

increase. Figure 7 present 6- bit binary weighted outputs, INL

and DNL, which shows more glitches in analog output and

maximum voltage 15mV.Figure 8 present thermometer-coded

DAC output, INL and DNL parameter, which shows that

there is good monotonicity, good DNL and less glitches

occurs compare to binary weighted DAC. But these two

structures are not able to design more than 8-bit. So, for more

resolution we use segmented structure which combine the

feature of both structures as shown in Figure 9. In segmented

DAC INL≤1LSB and DNL≤0.5LSB, this is in the range. As

well as, its design complexity and glitch are in between the

range of binary weighted and unary DAC. Table 1 indicates a

comparison of parameter of different Structure.

(a)

(b)

Figure 9. (a) 6-bit Segmented DAC (b) INL and DNL

TABLE 1: Comparison of parameter of different Structure

Parameter

Resolution

Rload

Imax

INL(LSB)

DNL(LSB)

Speed

(Sampling

rate)

Number of

transistors

Power

dissipation

(a)

(b)

Figure 7. (a) 6-bit Binary weighted DAC (b) INL and DNL

Binary

weighted

DAC

6-Bit

50 ohm

0.307mA

+0.15,-0.2

+0.1,-0.1

300MSPS

Unary

DAC

Segmented

DAC

6-Bit

50 ohm

0.307mA

0.16

+0.06,-0.1

300MSPS

6-Bit

50 ohm

0.307mA

0.6,-0.5

+0.4,-0.4

300MSPS

144

2262

586

51nW

60nW

33nW

6. Conclusion and Future work

The simulation results indicate that unary output has good

monotonicity and less glitch, but it requires more number of

transistors and extra decoder circuit. The thermometer code

will control the switches of the current source according to

the input code. This architecture uses a number of equal-size

elements which reduces glitches to a greater extent, therefore

improving the performance of the DAC. Binary weighted

DAC is easy to design, less complex and efficient but non

monotonous. Glitches in the output affect the performance of

the DAC. Due to the large ratio between the LSB and the

MSB, it is tough to synchronize the switching. The output can

change by substantially more than 1LSB, which gives rise to

a glitch. Thus, for high resolution, segmented architecture is

a good option as it has features of both architectures. By

connecting calibration circuit to reduce matching error in

segmented DAC; we can achieve more precise output.

(a)

(b)

Figure 8. (a) 6-bit unary DAC (b) INL and DNL

19

International Journal of Darshan Institute on Engineering Research and Emerging Technology

Vol. 4, No. 1, 2015, pp. 16-20

Nomenclature

DAC- Digital to Analog Converter

DSP-Digital Signal Processing

DNL-Differentiated Nonlinearity

INL-Integrated Nonlinearity

LSB-Least Significant Bit

MSPS-Million Samples per Second

SFDR-Spurious-Free Dynamic Range

7.

8.

References

1.

2.

3.

4.

5.

6.

Sabyasachi Chakraborty,“A critical Study on Digital to

Analog Conversion and vice versa and introduction to

Fuzzy circuit interface”, International Journal of

Scientific & Engineering Research, Volume 3, Issue 8,

August-2012 ISSN 2229-5518.

Rudy van de Plassche, “CMOS Integrated Analog-toDigital and Digital to Analog Converters”, 2nd edition,

Springer.

Anshul Agarwal, “Design of Low Power 8-Bit Digitalto-Analog Converter with Good Voltage-Stability”,

INTERNATIONAL

INSTITUTE

OF

INFORMATION TECHNOLOGY, Hyderabad, India,

May 2013.

Hongming Chenl , Xiaoyuan Chen, Yuhua Chengl, “A

Dual 12bit 80MSPS 3.3V Current-Steering DAC for

HINOC”, IEEE, 978-1-61284-193-9,2011.

Elnaz Ansari and David D. Wentzloff, “A 5mW

250MS/s 12-bit Synthesized Digital to Analog

Converter”, IEEE, 978-1-4799-3286-3, 2014.

Lei Jianming, Gui Hanshu, and Hu Beiwen, “A low

glitch 12-bit current-steering CMOS DAC for CNC

9.

10.

11.

12.

13.

14.

systems”, Journal of Semiconductors, Vol. 34, No. 2,

pp. 025007-1 to 025007-5, February 2013.

Seyed Javad Azhari, Khalil Monfaredi and Salar

Amiri, “A 12-bit, low-voltage, nanoampere-based,

ultralow-power, ultralow-glitch current-steering DAC

for HDTV”, International Nano letters,springer open

journal, 2228-5326-2-35, 2012.

Pankhaniya Shyamkumar Amrutlal, “study and

implementation of high speed current steering Digital

to Analog Converter”, Vishwakarma Government

Engineering College, Chandkheda, Ahmedabad, India,

MAY-2012.

J Jacob Wikner,“STUDIES ON CMOS DIGITAL TOANALOG CONVERTERS”, Linköpings universitet,

Sweden , ISBN91-7219-910-5 ISSN 0345-7524 ,

2001.

Soheil Radiom, Behzad Sheikholeslami, Hamed

Aminzadeh, and Reza Lotfi, “Folded Current Steering

DAC: An Approach to Low-Voltage High-Speed

High-solution D/A Converters”, IEEE, 0-7803-93902/06, 2006.

Guoyuan Fu, H. Alan Mantooth, and Jia Di, “A 12-Bit

CMOS Current Steering D/A Converter with a Fully

Differential Voltage Output”, IEEE, 978-1-612849140/11, pp.398, 2011.

Allen and holberg, “CMOS analog circuit design”,

Oxford

University

Press,ISBN

0195116445,

9780195116441, 2002.

Behzad razavi, “Design of analog CMOS Integrated

circuits”McGraw Hill, ISBN 0-07-118839-8, 2001.

R. Jacob Baker, Harry W. Li and David E. Boyce,

“CMOS Circuit Design, Layout, and Simulation”,

IEEE press, pp.755-837, ISBN 0·7803·3416·7, 1998.

Biographical notes

Khushali A.Shah is a P G Student of Department of Electronics & Communication Engineering, Vishwakarma Government Engineering

College, Chandkheda, Ahmedabad. She is doing Master Engineering in signal processing and VLSI Technology.

Mihir Shah is an Associate professor of Department of Electronics & Communication Engineering, Vishwakarma Government Engineering

College, Chandkheda, Ahmedabad. His research interest is VLSI System Design and Embedded Systems.

Naresh P Patel is an Assistant professor of Department of Electronics & Communication Engineering, Vishwakarma Government

Engineering College, Chandkheda, Ahmedabad. His research interest is VLSI System Design.

20