AN-646

APPLICATION NOTE

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106 • Tel: 781/329-4700 • Fax: 781/326-8703 • www.analog.com

Universal Evaluation Board for High Speed Op Amps

By John Ardizzoni

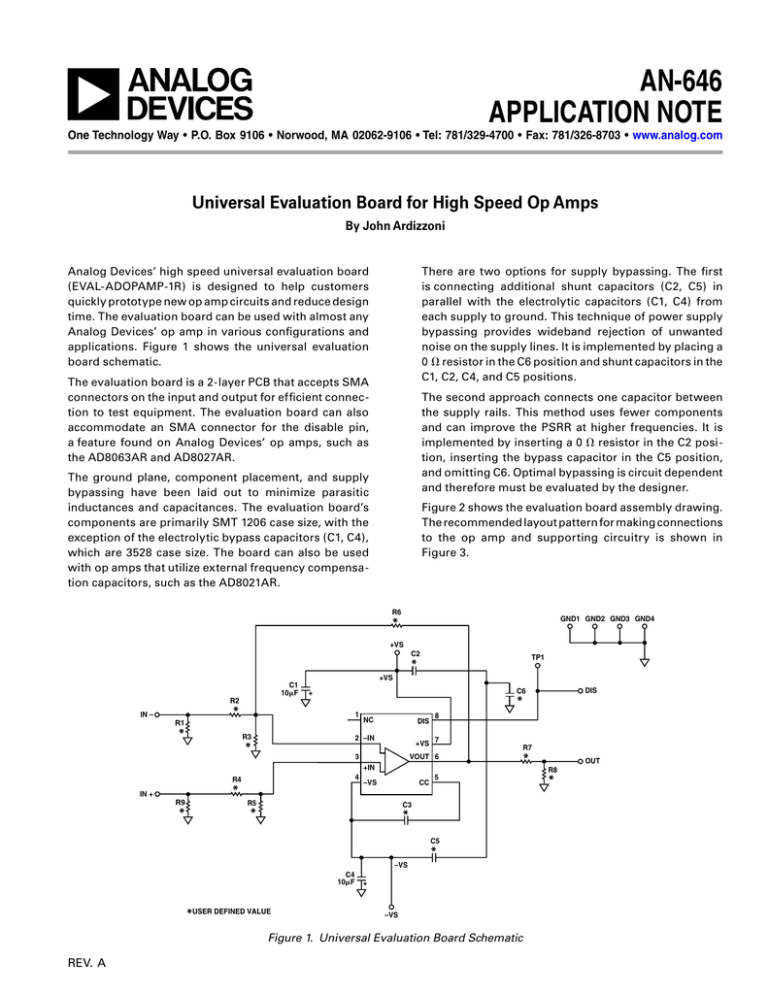

Analog Devices’ high speed universal evaluation board

(EVAL-ADOPAMP-1R) is designed to help customers

quickly prototype new op amp circuits and reduce design

time. The evaluation board can be used with almost any

Analog Devices’ op amp in various configurations and

applications. Figure 1 shows the universal evaluation

board schematic.

There are two options for supply bypassing. The first

is connecting additional shunt capacitors (C2, C5) in

parallel with the electrolytic capacitors (C1, C4) from

each supply to ground. This technique of power supply

bypassing provides wideband rejection of unwanted

noise on the supply lines. It is implemented by placing a

0 resistor in the C6 position and shunt capacitors in the

C1, C2, C4, and C5 positions.

The evaluation board is a 2-layer PCB that accepts SMA

connectors on the input and output for efficient connection to test equipment. The evaluation board can also

accommodate an SMA connector for the disable pin,

a feature found on Analog Devices’ op amps, such as

the AD8063AR and AD8027AR.

The second approach connects one capacitor between

the supply rails. This method uses fewer components

and can improve the PSRR at higher frequencies. It is

implemented by inserting a 0 resistor in the C2 position, inserting the bypass capacitor in the C5 position,

and omitting C6. Optimal bypassing is circuit dependent

and therefore must be evaluated by the designer.

The ground plane, component placement, and supply

bypassing have been laid out to minimize parasitic

inductances and capacitances. The evaluation board’s

components are primarily SMT 1206 case size, with the

exception of the electrolytic bypass capacitors (C1, C4),

which are 3528 case size. The board can also be used

with op amps that utilize external frequency compensation capacitors, such as the AD8021AR.

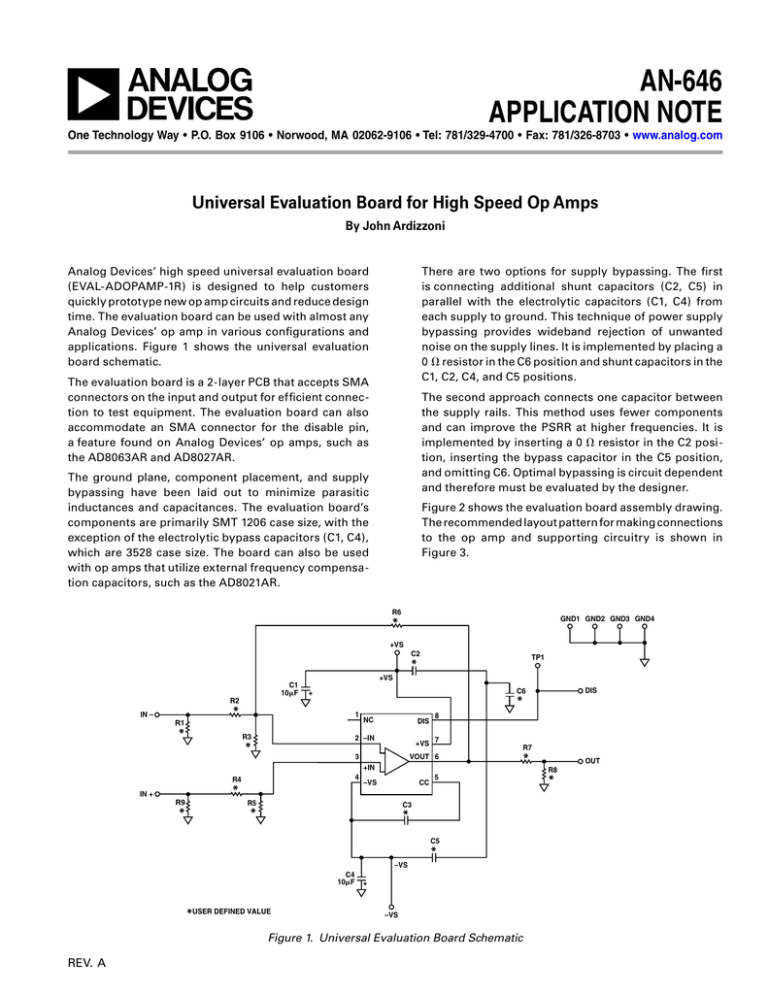

Figure 2 shows the evaluation board assembly drawing.

The recommended layout pattern for making connections

to the op amp and supporting circuitry is shown in

Figure 3.

R6

GND1 GND2 GND3 GND4

*

+VS

C2

TP1

*

C1

10F

R2

IN –

+VS

*

*

1

R1

*

R3

NC

DIS

2 –IN

*

8

+VS 7

3

VOUT 6

+IN

4

R4

IN +

*

R9

*

–VS

CC

R5

5

C3

*

*

C5

*

–VS

C4

10F

*USER DEFINED VALUE

+

–VS

Figure 1. Universal Evaluation Board Schematic

REV. A

DIS

C6

+

R7

*

R8

*

OUT

AN-646

UNIVERSAL HIGH SPEED

OP AMP EVALUATION BOARD

GND4

+VS

IN–

TP1

GND3

IN–

R6

DUT

R8

C3

IN+

C2

R7

OUT

*

R4

A00336C

R5

–VS

R9

C6

C4

GND2

R1

R2

OUT

*

R3

DIS

C5

*

C1

E03686–0–6/03(A)

ANALOG

DEVICES

IN+

GND1

EVAL-ADOPAMP-1R

SO SINGLE

COMPONENT SIDE

CIRCUIT SIDE

* SMA EDGE CONNECTOR JOHNSON COMPONENTS, INC. P/N 142-0701-831

Figure 2. Board Assembly Drawings

Figure 3. Board Layout Patterns

© 2003 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective companies.

–2–

REV. A