An Efficient and Accurate DC Analysis Technique for

advertisement

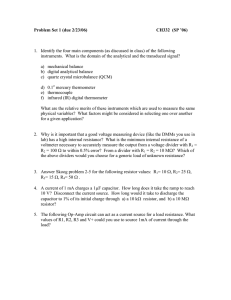

Analog Integrated Circuits and Signal Processing, 30, 239–241, 2002 C 2002 Kluwer Academic Publishers. Manufactured in The Netherlands. An Efficient and Accurate DC Analysis Technique for Switched-Capacitor Circuits MUSTAFA KESKIN,1 NURCAN KESKIN2 AND GABOR C. TEMES2 2 1 Qualcomm Inc., 5795 Morehouse Dr., San Diego, CA 92121 Department of Electrical and Computer Engineering, Oregon State University, Corvallis, OR 97331-3211 E-mail: mkeskin@qualcomm.com Abstract. A simple but highly accurate method is proposed to find the dc parameters of active or passive switchedcapacitor (SC) circuits. It is based on the dc model of a general SC branch. Key Words: switched-capacitor circuits, dc modeling, transient analysis, voltage multiplier, and power consumption Introduction Often, the steady-state dc average values of the voltages, currents, charges, and power or energy of an SC circuit need to be found. An example is the estimation of the output voltage, the input and output power and the efficiency of charge pumps used for dc voltage multiplication. These dc parameters can be found by transient analysis carried out over a long time using a simulation program such as SPICE; however, for good accuracy, the simulation must be performed with a very small integration time period to include fast switching transients, and the resulting data must be averaged over a long time. This makes the accurate prediction of the dc parameters a lengthy and expensive process. In this letter, a fast and accurate algorithm is described. It reduces the time required in computer analysis, and enhances its accuracy. Often, it enables the hand calculation of the dc parameters even for fairly complex circuits. into C when 1 = 1 is (C/T )(V1 − V2 ). The energy drawn from the circuit providing V1 in a clock period is (C · V1 )(V1 − V2 ); the energy delivered to C is (C/2)(V12 − V22 ), and the energy lost in the switches at port 1 is (C/2)(V1 − V2 )2 . Similar relations hold during the time period when 2 = 1. The average power flows can be obtained by dividing the energies delivered or lost in each clock period by T . It is easy to see that the equivalent circuit of Fig. 1(b) correctly predicts all dc currents, voltages, energies and power flows in the branch. As Fig. 2 illustrates, often the general circuit can be simplified, and then the equivalent circuit also becomes simpler. The proposed dc analysis method is based on replacing all switched-capacitor branches in the SC circuit by their resistive equivalents using Figs. 1 and 2, omitting (open-circuiting) all fixed capacitors, and carrying out the dc analysis of the resulting resistive circuit using SPICE or other computer program.1 As the examples shown below illustrate, the equivalent circuit often may even be analyzed by hand. A DC Model for an SC Branch Application Examples Figure 1(a) illustrates a typical SC branch containing a capacitor C and four periodically operated switches. The clock phases 1 and 2 are nonoverlapping signals. Assuming that the port voltages V1 and V2 change negligibly during any clock period T , simple analysis [1] shows that the average current flowing The effectiveness of the use of the equivalent circuits of Figs. 1 and 2 will next be demonstrated through two representative circuit analysis examples. The first circuit is an SC voltage doubler shown in Fig. 3(a). During the 1 = 1 time period, C is charged to E, while 240 M. Keskin, N. Keskin and Temes Φ1 Φ2 V1 V2 C V1 V1 V1 and the average current supplied by the battery is 2 · Il . The power efficiency is hence (Vout · Il )/(E · 2Il ) = 1 − (Il · T )/(2 · C · E). For E = 5 V, T = 0.5 µs, C = 10 pF and Il = 10 µA, the dc parameters Vout = 9.5 V, I1 = I2 = 10 µA, Pin = 100 µW and Pout = 95 µW result. The efficiency is high: η = Pout /Pin = 95%. The above analysis ignored the parasitic capacitances loading nodes A and B. This may be justified if C is an off-chip capacitor. However, for on-chip capacitors, the stray capacitances associated with the plates are typically 10–20% of the main capacitance, and their effects on the power efficiency can be devastating. Hence, next the effect of these parasitic capacitances will analyzed. Including Ctop = 0.05C and Cbot = 0.2C in the circuit, the equivalent circuit shown in Fig. 3(c) results. Even this expanded circuit can easily be analyzed by hand, using node analysis. It can also be analyzed as a dc circuit using SPICE without any of the numerical problems occuring in the time-domain analysis process. Table 1 compares the accurate results obtained using the proposed technique with those obtained by time-domain analysis and averaging using SPICE. Even after a lengthy computation, the latter still yields somewhat inaccurate data. It is also interesting to note that the output voltage dropped by 0.215 V, and the power efficiency η is reduced to 42%, due to the losses in the switched parasitic capacitances. As another simple example, the low-frequency output voltage and input current of the SC-active filter stage shown in Fig. 4(a) will be found in response to a slowly varying input voltage Vin and the inputreferred offset Vos of the opamp. The equivalent circuit, obtained using the model of Fig. 1(b), is shown in Fig. 4(b). By inspection, Vout = Vos + Vin and Iin = 0 A. T/C T/C V2 Φ2 Φ1 (b) (a) Fig. 1. (a) A typical SC branch (b) DC model. Φ1 Φ2 + V1 - T/C + V2 - C Φ1 Φ2 + V1 - C + V2 - + V1 - T/C + V1 - Fig. 2. Special cases. the load (represented by the 10 µA current sink Il ) discharges the 10 pF output buffer capacitor Cb with a voltage slope Il /Cb . When 2 goes high, C is connected in series with the battery, and it shares charges with Cb . At this time, the output voltage jumps, and then declines with a slope Il /(C + Cb ). An analytical calculation of the average output voltage, output power and efficiency based on the time-domain response is possible but lengthy, and so is the accurate computer simulation of the dc average values. By contrast, the model of Fig. 1 can be used to replace the circuit with the simple dc equivalent shown in Fig. 3(b). By inspection, the average output voltage is Vout = 2E − Il · (T /C) Φ1 T/C Ctop C Φ2 E Φ2 A B Il 10 µA Cbot Φ1 Cb =10 pF E I1 Il T/C I2 E (a) T/Ctop Vout -E (b) T/C E Vout Il T/C T/Cbot E Vout -E (c) Fig. 3. (a) The switched-capacitor voltage-doubler (b) DC model without parasitics (c) DC model with parasitics. Vout An Efficient and Accurate DC Analysis Technique 241 Table 1. Parameters with stray capacitances. DC Model HSPICE Vout Iout Pout Iin Pin η 9.285 V 9.2226 V 10 µA 10.15 µA 92.86 µW 93.64 µW 44.29 µA 45.53 µA 221.4 µW 227.6 µW 42% 41% Φ2 T/C 1 C2 Vin Φ1 C1 Φ1 Vin Φ2 - Vin - Vout Vout -V os + Vos T/C 1 (a) Vou t + Vos (b) Fig. 4. The active filter stage. The calculation of these values using node analysis, SPICE or SWITCAP [2] would have been considerably more difficult and less accurate. Note Conclusions References A straightforward and highly accurate technique was proposed for obtaining the dc performance parameters of switched-capacitor circuits. Two circuits, a voltagedoubler charge pump and a direct-charge-transfer active stage, were analysed to illustrate the functionality and efficiency of the proposed method. 1. Temes, G. C., “On-chip supply and clock voltage multipliers for low-voltage CMOS ICs,” Lecture Notes, Short Course on Low-Voltage, Low-Power Analog CMOS IC Design. Ecole Polytechnique Federal de Lausanne, Switzerland, June 1999. 2. SWITCAP, http://www.elab.columbia.edu/projects/switcap/. 3. Maxwell, J. C., “A treatise on electricity and magnetism,” pp. 420– 421, 1873. 1. Note that replacing SC branches by equivalent resistors is an idea which dates back all the way to Maxwell [3]. However, our model is somewhat more elaborate than his.