Datasheet

Universal DDR IO Pad

(DDR4, DDR3, DDR3L, LPDDR3, LPDDR2, HSTL class-I, RLDRAM-3 IO)

Overview

The KRIVI Universal DDR IO pad is suitable for memory controller applications within a DDR4, DDR3, DDR3L, LPDDR3,

LPDDR2, HSTL-class I, RLDRAM-3 and other similar standards. The Universal DDR IO pad provides JEDEC compliance,

robust ESD performance, comprehensive feature set and well-defined architecture that allow designers extensive flexibility for

various applications, and a roadmap to future products. The benefits of Krivi IO pad comes from differentiated performance

through PVT compensated slew rates, low area, power and noise. KRIVI minimizes risk with extensive pre-silicon verification,

resulting in highly reliable products, which are manufacturable in leading CMOS processes. Universal DDR IO pad is a member

of the Krivi’s Memory Interface solutions family.

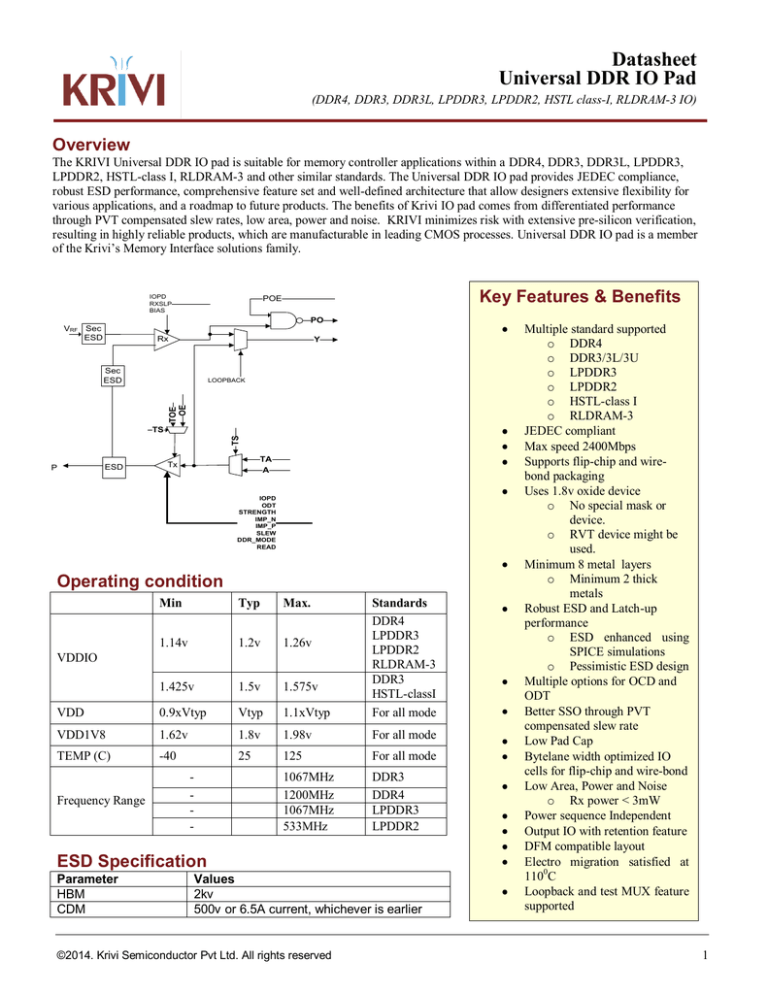

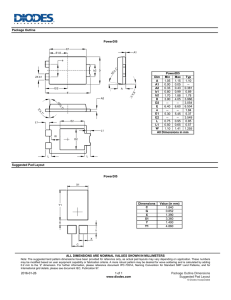

IOPD

RXSLP

BIAS

Key Features & Benefits

POE

PO

VRF

Sec

ESD

Rx

Y

Sec

ESD

TOE

OE

LOOPBACK

TS

TS

P

ESD

TA

A

Tx

IOPD

ODT

STRENGTH

IMP_N

IMP_P

SLEW

DDR_MODE

READ

Operating condition

Min

Typ

Max.

1.14v

1.2v

1.26v

1.425v

1.5v

1.575v

VDD

0.9xVtyp

Vtyp

1.1xVtyp

Standards

DDR4

LPDDR3

LPDDR2

RLDRAM-3

DDR3

HSTL-classI

For all mode

VDD1V8

1.62v

1.8v

1.98v

For all mode

TEMP (C)

-40

25

125

For all mode

1067MHz

1200MHz

1067MHz

533MHz

DDR3

DDR4

LPDDR3

LPDDR2

VDDIO

Frequency Range

-

ESD Specification

Parameter

HBM

CDM

Values

2kv

500v or 6.5A current, whichever is earlier

©2014. Krivi Semiconductor Pvt Ltd. All rights reserved

Multiple standard supported

o DDR4

o DDR3/3L/3U

o LPDDR3

o LPDDR2

o HSTL-class I

o RLDRAM-3

JEDEC compliant

Max speed 2400Mbps

Supports flip-chip and wirebond packaging

Uses 1.8v oxide device

o No special mask or

device.

o RVT device might be

used.

Minimum 8 metal layers

o Minimum 2 thick

metals

Robust ESD and Latch-up

performance

o ESD enhanced using

SPICE simulations

o Pessimistic ESD design

Multiple options for OCD and

ODT

Better SSO through PVT

compensated slew rate

Low Pad Cap

Bytelane width optimized IO

cells for flip-chip and wire-bond

Low Area, Power and Noise

o Rx power < 3mW

Power sequence Independent

Output IO with retention feature

DFM compatible layout

Electro migration satisfied at

1100C

Loopback and test MUX feature

supported

1

Universal DDR IO pad Datasheet

Specifications

Cell List

VIL and VIH specification

Parameter

DDR4

Cell Name

DDR3

LPDDR3

LPDDR2

VIH (DC)

TBD

VREF+0.1

VREF+0.1

VREF+0.13

VIL (DC)

TBD

VREF-0.1

VREF-0.1

VREF-0.13

VIH (AC)

N/A

VREF+0.135

VREF+0.135

VREF+0.22

VIL (AC)

N/A

VREF-0.135

VREF-0.135

VREF-0.22

VIHL_AC

186mv(min)

N/A

N/A

N/A

Notes :

1.

VREF =0.5*DVDD for DDR3 and center tap termination.

2.

VREF for DDR4 and LPDDR3 depends upon OCD and ODT values.

HSTLclass I

VREF+0.1

VREF-0.1

VREF+0.2

VREF-0.2

N/A

Description

RLDRAM-3

IODDR_DQ

VREF+0.1

VREF-0.1

VREF+0.135

VREF-0.135

N/A

IODDR_DQS

DQ bidirectional

data cell

DQS bidirectional

data cell

IODDR_CLK

CLK output pad

IODDR_CMD

ADD/CMD output

pad with retention

IODDR_VREF

VREF data cell

IODDR_CAL

IO Impedance

Calibrator cell

DC specification

Parameter

IODDR_BIAS

IO BIAS cell

Values

Unit

IODDR_PWRSNSE

OCD

34 , 40, 48, 60

Ω

IO Power sense

cell

IODDR_VDDIO

VDDIO cell

ODT

30,40,48,60, 80,120, 240

Ω

IODDR_VSSIO

DVSSIO cell

IODDR_VDD

VDD cell

IODDR_VSS

VSS cell

IODDR_VDD1v8

1.8v supply cell

IODDR_VSS1v8

1.8v ground cell

IODDR_ESD1

IOESD cell

IODDR_ESD2

IOESD cell

IODDR_LVSFT

Level shifer cell

IODDR_BLBRK

Byte Lane Breaker

cell

IODDR_BRK

Breaker cell

IODDR_CORNER

Corner cell

IODDR_FILLEROV

FILLER cell 1u

without contacts

IODDR_FILLER5

FILLER cell 5u

IODDR_FILLER10

FILLER cell 10u

IODDR_DECAP10

Decap cell 15u

IODDR_DECAP5

Decap cell 5u

IODDR_ANALOG

Analog cell

IODDR_BP

Bond pad cell

OCD Specification For DDR4

RONNOM

Resistor

Vout

34Ω

RON34PD

0.5*VDDQ

0.8*VDDQ

1.1*VDDQ

RON34PU

0.5*VDDQ

0.8*VDDQ

1.1*VDDQ

Min

0.8

0.9

0.9

0.9

0.9

0.8

Typ

1

1

1

1

1

1

Max

1.1

1.1

1.25

1.25

1.1

1.1

Unit

34Ω

34Ω

34Ω

34Ω

34Ω

34Ω

Notes:

RONPU = VDDQ-Vout/|Iout| ; when RONPD is disabled.

RONPD= Vout/|Iout| ; when RONPU is disabled

AC Parameter

Parameter

Frequency

Min

-

DDR3/LPDDRn

Slew

Rate

DDR4

Duty cycle

Notes:

1.

2.5

4

48

Max.

1200Mhz : DDR4

1067MHz : (LP)DDR3

867MHz : DDR3L

5

9

52

Duty cycle in monte carlo simulation might degrade by +/- 1%

Unit

MHz

V/ns

V/ns

%

Deliverables

GDSII, CDL, Verilog, LEF, .lib, IBIS, User-guide

Krivi reserves the right to make changes to any products and services described herein, at any time without notice in order to make improvements

in design, performance, or presentation and to provide the best possible products and services. Customers should obtain the l atest specifications

before referencing any information, product, or service described herein, except as expressly agreed in writing by an officer of Krivi.

Krivi does not assume any responsibility or liability arising out of the application or use of any products or services described herein, except as

expressly agreed to in writing by an officer of Krivi; nor does the purchase, lease, or use of a product or service from KRIVI convey a license under

any patent rights, copy rights, trademark rights, or any other intellectual property rights of Krivi or of third parties.

Website: http://krivisemi.com

©2014. Krivi Semiconductor Pvt Ltd. All rights reserved

V1.0

2