SIS8300 MTCA.4 Digitizer 4/8-channel 250 MSPS 14-bit

advertisement

SIS Documentation

SIS8300 Digitizer

250 MSPS 14-bit

SIS8300

MTCA.4 Digitizer

4/8-channel 250 MSPS 14-bit

Addendum

SIS GmbH

Harksheider Str. 102A

22399 Hamburg

Germany

Phone: ++49 (0) 40 60 87 305 0

Fax:

++49 (0) 40 60 87 305 20

email: info@struck.de

http://www.struck.de

Version: SIS8300-M-2403-1-V101-250MSPS_attendum.doc as of

08.08.2013

Page 1 of 10

SIS Documentation

SIS8300 Digitizer

250 MSPS 14-bit

Revision Table:

Revision

0.001

1.00

1.01

Page 2 of 10

Date

18.02.2013

19.02.2013

08.08.2013

Modification

Generation

First official release.

Add Tap delay table

Add ADC data format mode (related to Firmware V_2403)

SIS Documentation

SIS8300 Digitizer

250 MSPS 14-bit

- Table of contents

1

2

3

4

5

6

Table of contents....................................................................................................................................... 3

Introduction .............................................................................................................................................. 4

1.1

Related documents............................................................................................................................. 4

Design ...................................................................................................................................................... 5

250 MSPS Setup ....................................................................................................................................... 5

3.1

Disable ADC channels 9 and 10......................................................................................................... 5

3.2

Tap delay........................................................................................................................................... 5

3.3

AD9510 clock distributor................................................................................................................... 6

3.4

ADC data format ............................................................................................................................... 7

3.4.1

User Control/Status register....................................................................................................... 8

Firmware .................................................................................................................................................. 9

Memory Read Speed ................................................................................................................................. 9

Index....................................................................................................................................................... 10

Page 3 of 10

SIS Documentation

1

SIS8300 Digitizer

250 MSPS 14-bit

Introduction

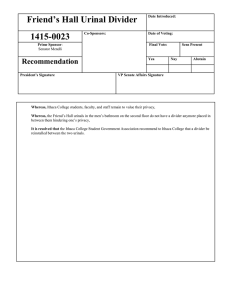

The original SIS8300 design is a 10 channel 125 MS/s digitizer with 16-bit resolution

according to the MTCA.4 standard. This addendum describes the 4/8 channel 250 MS/s 14-bit

stuffing option on the base of four Analog Devices AD9643BCPZ-250 dual digitizer chips.

Please refer to the manual of the 125 MS/s unit for a full hardware and register description.

10 channel 125 MSPS 16-bit SIS8300 with SFPs installed

As we are aware, that no manual is perfect, we appreciate your feedback and will incorporate proposed

changes and corrections as quickly as possible. The most recent version of this manual can be obtained

by email from info@struck.de, the revision dates are online under http://www.struck.de/manuals.html .

Note: The SIS8300 was developed in co-operation with DESY under ZIM grant 2460101MS9

(ZIM: Zentrales Innovationsprogramm Mittelstand)

1.1 Related documents

A list of available firmware designs can be retrieved from http://www.struck.de/sis8300firm.html

Page 4 of 10

Struck Documentation

2

SIS8300 Digitizer

250 MSPS 14-bit

Design

Four Analog Devices AD9643BCPZ-250 dual digitizer chips covering SIS8300 channels 1-8

are installed. Simultaneous sampling of all 8 channels is possible up to 4 KSample event size.

There are no event size limitations for simultaneous acquisition with four active channels

(channels 1, 3, 5 and 7 e.g.).

Note 1: ADC channels are disabled in the Sample Control register

3 250 MSPS Setup

3.1

Disable ADC channels 9 and 10

ADC channels 9 and 10 have to be disabled always, four more channels for event sizes above

4 KSamples.

data = 0x300 ; // disable channel 9/10

SIS8300_Write_Register(sis8300_device, SIS8300_SAMPLE_CONTROL_REG, data);

3.2

Tap delay

The Tap Delay has to be set to 11 !

gl_class_adc_tap_delay = 11 ;

SIS8300_Write_Register(sis8300_device, SIS8300_ADC_INPUT_TAP_DELAY_REG,

0x1f00 + (gl_class_adc_tap_delay & 0x3f));//

Tap Delay / Sample frequency table:

Tap Delay

value

0

1

2

3

4

5

6

7

8

9

10

11

Min

Sample rate

(MHz)

40

40

40

40

40

40

40

40

40

40

40

40

Max

Sample rate

(MHz)

160

170

180

190

200

210

220

230

240

250

250

250

Page 5 of 10

Struck Documentation

SIS8300 Digitizer

250 MSPS 14-bit

3.3

AD9510 clock distributor

The clock divider has to be set to bypass

// AD9510 Clock Distributuon IC

//ch_divider_configuration_array[i] :

//

bits <3:0>: Divider High

//

bits <7:4>: Divider Low

//

bits <11:8>: Phase Offset

//

bit <12>: Select Start High

//

bit <13>: Force

//

bit <14>: Nosyn (individual)

//

bit <15>: Bypass Divider

//#define CLK_25MHZ //with Phase

clock_source_choice = fCombo_Clock_source->GetSelected();

ad9510_divider_data = 0x0 ;

switch (clock_source_choice) {

case 0: // 250 MHz

ad9510_divider_data = 0x8000 ;

double_fft_frequency = 250000000.0 ;

break;

case 1: // 125 MHz

ad9510_divider_data = 0x0 ;

double_fft_frequency = 125000000.0 ;

break;

case 2: // 62.5 MHz

ad9510_divider_data = 0x11 ;

double_fft_frequency = 62500000.0 ;

break;

case 3: // 41.66 MHz

ad9510_divider_data = 0x22 ;

double_fft_frequency = 41660000.0 ;

break;

case 4: // 31.25 MHz

ad9510_divider_data = 0x33 ;

double_fft_frequency = 31250000.0 ;

break;

case 5: // 25 MHz

ad9510_divider_data = 0x44 ;

double_fft_frequency = 25000000.0 ;

break;

case 6: // 83.33 MHz

ad9510_divider_data = 0x10 ; // internal Sample Clock 83.33 MHz ; test only

double_fft_frequency = 83330000.0 ;

break;

}

ad9510_divider_configuration_array[0] = 0x0000 + ad9510_divider_data ; // (ADC1-CLK, ch1/2)

//ad9510_divider_configuration_array[1] = 0x0200 + ad9510_divider_data ; // (ADC2-CLK, ch3/4) phase:

2 clks

ad9510_divider_configuration_array[1] = 0x0000 + ad9510_divider_data ;

ad9510_divider_configuration_array[2] = 0x0000 + ad9510_divider_data ;

ad9510_divider_configuration_array[3] = 0x0000 + ad9510_divider_data ;

ad9510_divider_configuration_array[4] = 0x0000 + ad9510_divider_data ;

ad9510_divider_configuration_array[5] = 0x0000 + ad9510_divider_data ;

ad9510_divider_configuration_array[6] = 0x0000 + ad9510_divider_data ;

synch. of external Triggers

// (ADC2-CLK, ch3/4)

// (ADC3-CLK, ch4/5)

// (ADC4-CLK, ch6/7)

// (ADC5-CLK, ch8/9)

// (Frontpanel Clk, Harlink)

// (FPGA DIV-CLK05) used for

ad9510_divider_configuration_array[7] = 0xC000 + 0x00 ; // (FPGA DIV-CLK69) used for sychn. of

AD910 ISc and Bypass

SIS8300_AD9510_SPI_Setup(sis8300_device, ad9510_divider_configuration_array, 1

/*ad9510_synch_cmd*/ );

Page 6 of 10

Struck Documentation

SIS8300 Digitizer

250 MSPS 14-bit

3.4

ADC data format

Two additional ADC data format modes are added:

Mode 1:

one bit to shift up the 14-bits bit by two bits and have 0's in bit 0 and 1

Mode 2:

one bit to copy bit 13 into bits 14 and 15

The ADC data format will be programmed with the User Control/Status register (0x4) bit 4

and bit 5.

ADC data format table:

mode

0

bit 1

0

bit 0 ADC data format

0 Memory Bits 15:14 = 00

Memory Bits 13:0 = ADC bits 13:0

1

(new)

0

1

Memory Bits 15:2 = ADC bits 13:0

Memory Bits 1:0 = 00

2

(new)

1

0

Memory Bits 15

= ADC bits 13 (sign)

Memory Bits 14

= ADC bits 13 (sign)

Memory Bits 13:0 = ADC bits 13:0

3

1

1

Reserved

Notes:

The internal FIR Trigger works with ADC data format mode 0 and 1 , only in

combination with the ADC chip “Offset Binary Output Mode”.

The ADC data format mode 2 is used in combination with the ADC chip “Twos

Complement Output Mode”.

Page 7 of 10

Struck Documentation

SIS8300 Digitizer

250 MSPS 14-bit

3.4.1 User Control/Status register

#define SIS8300_USER_CONTROL_STATUS_REG

0x04

The control register is implemented as a selective J/K register, a specific function is enabled

by writing a 1 into the set/enable bit, the function is disabled by writing a 1 into the

clear/disable bit (which location is 16-bit higher in the register). An undefined toggle status

will result from setting both the enable and disable bits for a specific function at the same

time. The only function at this point in time is user LED on/off.

On read access the same register represents the status register.

Bit

31

..

24

23

22

21

20

19

18

17

16

15

..

8

7

6

5

4

3

2

1

0

write Function

Clear reserved 15 (*)

..

Clear reserved 8 (*)

Clear reserved 7 (*)

Clear reserved 6 (*)

Clear ADC data format bit 1 (*)

Clear ADC data format bit 0 (*)

Clear reserved 3 (*)

Clear reserved 2 (*)

Switch off LED test

Switch off user LED (*)

Set reserved 15

..

Set reserved 8

Set reserved 7

Set reserved 6

Set ADC data format bit 1

Set ADC data format bit 0

Set reserved 3

Set reserved 2

Switch on LED test

Switch on user LED

(*) denotes power up default setting

Page 8 of 10

read Function

0

..

0

0

0

0

0

0

0

0

0

Status reserved 15

..

Status reserved 8

Status reserved 7

Status reserved 6

Status ADC data format bit 1

Status ADC data format bit 0

Status reserved 3

Status reserved 2

Status LED test

Status User LED (1=LED on, 0=LED off)

Struck Documentation

4

SIS8300 Digitizer

250 MSPS 14-bit

Firmware

The 8 channel 250 MSPS firmware 0x2402 is based on the 10 channel 125 MSPS 0x1402

firmware. A Xilinx ISE project framework to assist in the development of your own

customized firmware is furnished on the Struck product DVD.

5 Memory Read Speed

The DMA read speed is appr. 450 MByte/s.

Page 9 of 10

Struck Documentation

SIS8300 Digitizer

250 MSPS 14-bit

6 Index

250 MSPS setup 5

AD9510 6

AD9643BCPZ-250 4, 5

ADC data format 7

clock divider 6

design 5

DESY 4

Firmware 9

introduction 4

ISE 9

LED

test 8

Page 10 of 10

user 8

Memory Read Speed 9

MTCA.4 4

register

sample control 5

User Control/Status 8

SIS8300 4

tap delay 5

user

LED 8

Xilinx 9

ZIM 4