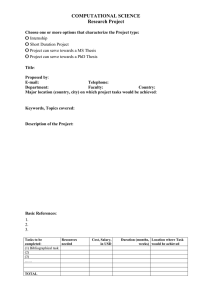

Master Thesis/Internship Topic Guide 2013-2014

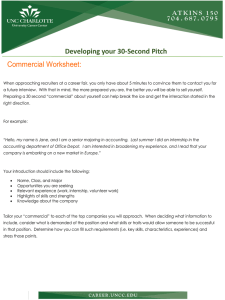

advertisement