A New ZVZCS Isolated Dual Series Resonant DC

advertisement

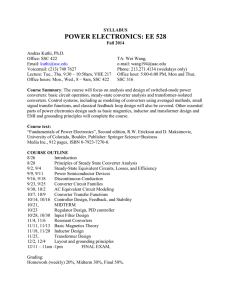

A New ZVZCS Isolated Dual Series Resonant DC-DC Converter with EMC Considerations A. Nemati* and M. Pakdel** Abstract: A novel ZVZCS isolated dual series-resonant active-clamp dc–dc converter is proposed to obtain high efficiency. The proposed converter employs an active-clamp technique, while a series-resonant scheme controls the output voltage with the complementary pulse width modulation controller. The active-clamp circuit serves to recycle the energy stored in the leakage inductance or the magnetizing inductance and provides zero-voltage and zero-current turn-on and turn off switching. The voltage stresses of the main switch are clamped. The voltage transient spikes across the dual series active clamp circuit and the current stress of the current-fed side switches are limited by auxiliary active clamping circuits on both sides, and ZVZCS is achieved. The operating principles and design considerations are discussed and verified by simulations using PSIM software. Also, the EMI reduction techniques from EMC point of view in the circuits related to converters has been pointed out. Keywords: Converter, EMC, Series-Resonant, Soft-Switching. 1 Introduction1 In switching mode power supplies, as the switching frequency increases for high power density and with small size, switching losses associated with the turn-on and turn-off of the devices in the power converter are increased. These losses are so significant that the operations of the power converters at high frequency are limited. To overcome these problems, a number of full, quasi-, and multi-resonant dc–dc converter topologies have been investigated in [1], [2]. However, although resonant mode power conversion achieves low switching loss at high frequency compared to the pulsewidth modulation (PWM) converter, these converters have some difficulties such as size reduction, EMI noise, and filter design because a wide variety of switching frequency is needed to control the output voltage. Also, the resonant converters typically have large component stresses due to high peak currents and voltages. Therefore, the trend in power processing technology has been toward combining the simplicity of PWM converters with the soft-switching characteristics of the resonant converters [3]–[10]. Iranian Journal of Electrical & Electronic Engineering, 2010. Paper first received 29 Aug. 2009 and in revised form 13 July 2010. * The Author is with Young Researchers Club, Islamic Azad University- Tehran South Branch, Tehran-Iran. E-mail: nemati_abbas@yahoo.com ** The Author is with Department of Electrical and Electronic Engineering, Islamic Azad University-Miyaneh Branch, MiyanehIran. E-mail: majidpakdel@yahoo.com 190 As discussed in [11], the phase-shifted zero-voltage switching full-bridge converter is one of the most attractive techniques, as it allows all switches to operate at zero-voltage turn-on switching (ZVS) by utilizing the leakage inductance of the power transformer without an auxiliary switch [12]-[14]. However, the complexity of the full-bridge is almost the highest due to its increased switches and complicated control. Therefore, the activeclamp circuit and the half-bridge circuit composed of two switches and operated by the asymmetrical PWM controller are other typical examples to successfully realize ZVS for the switches by utilizing leakage inductance, magnetizing inductance, and parasitic capacitance [15]–[21]. In particular, the forward converters and the flyback converters using these circuits provide the zero-current turn-off switching (ZCS) of the output diodes by the resonant-current formed by the leakage inductance of the transformer and the clamp capacitor (or blocking capacitor). However, since these converters transfer the input energy to the output stage, when the main switch is only in the onstate or off-state, the transformer utilization is reduced in comparison with the dc–dc converter such as the push–pull, full-bridge converters. In addition, dc–dc converters such as the conventional forward and flyback converters have a severe difficulty in surge occurrence due to leakage inductance of the transformer and the reverse-recovery problem of output diodes. To absorb the surge energy and achieve the ZVS operation, the active-clamp technique was proposed and its stability was analyzed Iranian Journal of Electrical & Electronic Engineering, Vol. 6, No. 3, Sep. 2010 [22]–[24]. Forward F conveerters and flyyback converrters using active--clamp circuits are the suitaable topologiees to achieve highh efficiency att higher frequeency for low and medium pow wer applicationns. Active-claamp circuits were w introduced as a a resetting technique forr the transform mer of the forwaard converterr and an active snubber in i a flyback convverter. Moreoover, these cirrcuits have been b used as a sofft-switching technique t in PWM P convertters. Thus, the acttive-clampingg technique haas been provenn to be an important componennt/factor for PWM converteers. In this paaper, a ZVZC CS isolated DC-DC D conveerter [25] and a dual d series ressonant active--clamp conveerter [11] are com mbined to form m a very effecctive zero-volttage and zero current c switching convertter with higgher efficiency. So, the prooposed topoology has both b advantages inn comparisonn with the connverters propoosed in [11], [25]. The switchees used in thee proposed dcc–dc converter arre operated by a compllementary PW WM controller att the constantt switching frequency. fr In the proposed coonverter, the active-clampp circuit of the primary sidee provides thee turn-on and turn-off ZVZ ZCS of the switchhes and clampps the voltagee spike across the switches. Moreover, M sincce the proposed dual serriesresonant circcuit providess two resonannt-current paaths, energy throuugh the powerr transformer, regardless off the switch statee, is delivereed.[26] The voltage stressses across the output o diodess are clampeed to the outtput voltage of thhe converter. Thus, T the propposed dual serriesresonant actiive-clamp connverter can reeduce the volttage stress, curreent stress, annd the switchhing loss of the switching deevices. Also, the voltage transient spiikes across the dual d series acctivate clampp circuit and the current stresss of the currennt-fed side switches are limited by auxiliary active clampiing circuits onn both sides, and ZVZCS is acchieved. The operrating principles and desiggn consideratiions are discussedd and verifiedd by simulatiions using PS SIM software. O 2 Principlees of Circuit Operation The ZVZ ZCS isolatedd dual seriess-resonant dcc–dc converter is proposed p as shhown in Fig. 1. This conveerter is composedd of a dual series-resonan s nt circuit andd an active-clampp circuit. In thhis section, a detailed analyysis and d design conccept for the tuurn-on and turn n-off ZVZCS S opeeration of swiitches and thee turn-off ZCS S operation off thee output diodees are presentted. To analyzze the steady-staate operation of o the proposeed converter shown s in Fig.. 1, several assum mptions are m made during one o switchingg perriod TS ( TS is selected 1000 kHz and is the switchingg freequency of sw witches S1 and S 2 and S5 ). 1) Main switch S1 and auxiliary switch S 2 are operatedd by an asymmettrical PWM m method with a short deadd me and the dutty ratio D is bbased on the switch s tim S1 . 2) All switchess, S1 and S2 , are ideal exccept for theirr outtput capacitannces CS 1 , CS 2 and their bod dy diodes. 3) The ripple coomponent of thhe clamp capaacitor voltagee VC is negligiblee because thee clamp capaccitor CC has a large value. Thhen, the averaage voltage across a CC is,, Vin)/(1−D). (DV The steady-sstate operatioon of the pro oposed dc–dcc con nverter includes eight m modes during a switchingg perriod Ts. The equivalent ccircuits in eaach mode aree desscribed in Fig. 2. Mo ode 1: At thiss mode, switchhes S1 , S 2 , S3 and S5 aree turrned on. Swittches S1 , S 2 , S3 and S5 reverse biass dio odes and the output o diodes D1 and D3 arre maintainedd to the off-statee. Also, the capacitor CC is chargedd thrrough resonannt circuit. Mo ode 2: At this mode, after 1μs , switch S 4 is turned onn and d switch S 2 is turned off affter 2μs . Swiitches S1 , S3 and d S 5 are mainttained to on-sttate also switcch S 2 reversee dio ode is turned on o and the ouutput diodes D1 and D3 aree maaintained to thhe off-state. A Also, the reson nant circuit iss forrmed by thhe capacitor CC and the primaryy maagnetizing indductance of traansformer and d the current iss osccillated amongg the resonantt circuit. Mo ode 3: At thhis mode, swiitch S3 is tu urned off (thee sw witching frequeency of switcches S3 and S 4 gate drivee sig gnal is selected 200 kHz). T The diode D1 is turned onn and d the transforrmer secondarry current is flowed f to thee loaad. Also, the oscillating cuurrent is floweed among thee ressonant circuit. Mo ode 4: At this mode, afteer 1μs , switcch S 4 is alsoo turrned off and the capacitorr CO1 is chaarged throughh sw witch S 4 reveerse bias dioode. Also, th he oscillatingg currrent is flowedd among the rresonant circuiit. Mo ode 5: At thiss mode, switcches S1 and S5 are turnedd Fig. 1 Proposeed ZVZCS isolaated dual seriess-resonant convverter. offf and switch S3 is turned oon and the cap pacitor CC iss disscharged throuugh the resonaant circuit and d in this modee thee second of transformer is short-circu uited throughh sw witch S3 and innductor L2 . Nemati & Paakdel: New ZV VZCS Isolatedd Dual Series Resonant DC C-DC Converteer 1911 Fig. 2 Equivalent Circuit of Operation Modes. 192 Iranian Journal of Electrical & Electronic Engineering, Vol. 6, No. 3, Sep. 2010 Mode 6: At this mode, switch S4 is turned on after 1μs , and the capacitor CO1 is also discharged through Lm ⟨ the resonant circuit. Mode 7: At this mode, switch S 2 is turned on and the capacitor CC is charged through the resonant circuit. where f S is the switching frequency? The critical angular resonant frequency ω rc for the turn-off ZCS Mode 8: At this mode, switch S3 is turned off and the current is flowed to the load. 3 Analysis of Circuit Parameters In this section, the design equations of the proposed ZVZCS isolated dual series-resonant dc–dc converter using the active-clamp mechanism operated by the complementary PWM controller are introduced. As in [11], the ripple component of the clamp capacitor CC voltage VC can be neglected by the large clamp capacitor value. Therefore, the average voltages across switches S1 and S 2 are the sum of the dc-input voltage Vin and the average clamp capacitor voltage VC is as follow [11]: V S 1 = V S 2 = V in + V C = 1 V in 1− D (1) Thus, if voltages VS 1 and VS 2 are determined by considering the voltage-rating, and the voltage-margin of the switches S1 , S 2 and the dc-input voltage V are selected, the duty ratio D can be calculated from (1). obtained as follows [11]: ω rc = π D (4) fS 4 EMC Consideration For EMI reduction from EMC point of view in converters and related circuits can be used from the following methods [28]: a. use of the common mode current, ferritebead and optocoupler on the transmission lines, b. use of the suitable input filtering; c. use of the trace termination to do impedance matching in transmission lines between source, transmission line and load Impedances; d. EMI reduction through reduction of clock signal edge rate or increase of its rise/fall time. With decreasing the clock signal edge rate can delete many of the clock signal undesirable harmonics in τ -20dB/dec However, The ZVS design of the main switch S1 is determined by the magnetizing inductance Lm and the output power PO . If the maximum output power PO max of the converter is selected, from the turn-on ZVS condition [27] to meet the soft switching of the main switch S1 , the magnetizing inductance value Lm can be determined as: tf tr (2) The soft switching of the auxiliary switch S 2 is naturally achieved by the stored energy in the leakage inductance Llk and the magnetizing inductance Lm . (3) V(dBv) Vo (1 − D) Vin 2 design of the output diodes D1 and D2 is determined according to the duty ratio D . If the duty ratio D is smaller than 0.5 at the selected constant input voltage Vin , the critical angular resonant frequency ω rc can be If the leakage inductance of the transformer is a very small value compared to the magnetizing inductance, the voltage transfer function of the proposed converter then becomes that of an isolated boost converter. Therefore, although this paper does not manage the step-up applications, the proposed converter can be considered as the isolated boost converter suitable for the step-up applications. Turns ratio n of the transformer is thus obtained as [11]: n= D (1 − D ) 2 V o 2 n 2 f S Po , max -40dB/dec 1 π t r (or 1 π t f ) 1 πτ F(Hz) Fig. 3 Clock signal with related Fourier transform. Nemati & Pakdel: New ZVZCS Isolated Dual Series Resonant DC-DC Converter 193 RF) Frequency Spectrum, speccially in radioo frequency (R according Figg 3. e. EM MI reduction through reduuction of the line length. 5 Simulatioon Results To verifyy the theoretiical analysis of the propoosed topology, the simulation results usingg PSIM softw ware are given. The proposed topology andd control strattegy in PSIM woorkspace is shhown in Fig. 4, the follow wing parameters have h been chosen c in sim mulation circcuit: Vin = 200V , L1 = 4μH , C O 1 = 560 μ F , C C = 2 .2 μ F L2 = 10 μH , C S 1 = C S 2 = C S 3 = 1nF , L m = 500 μ H Fig g. 5 ZVZCS waaveforms of I S 1 , VS 1 , and S1 drive signal. N P N S = 400 14 , C O 2 = 560 μ f , Ro = 1Ω . The curreent and voltagge across the switch and drrive signal ZVZC CS waveformss of switches S1 , S 2 , S3 , S 4 and S5 are shown in Figgs. 5-9 respecctively. Also, the waveform off output voltaage, Vout , is shhown in Fig. 10. The output power p of thee ZVZCS isolated dual series resonant dc-dc converter is about 650 W . As shownn in Figs. 4-9, thee proposed toppology for dc--dc converter has lower powerr losses and higher efficciency and softswitching zeero-voltage orr zero-currentt or both of the conditions taake place in turn t on and tuurn off of all the switches. Fig g. 6 ZVZCS waaveforms of I S 2 , VS 2 , and S2 drive signal. 6 Experimeental Results Fig. 11 illustrates thee experimentaal circuit of the study and fiigures 12-18 show the obtained resultss of experimentall circuit of thee present studdy. In this circuit as discussedd in part 4, thhe EMC Tecchniques suchh as input filterinng, clock siggnal edge ratte reduction and using comm mon mode choke, ferrrite bead and optocoupler have been used u for EMII reduction. The T clock signal frequency is 50 kHz and is shown in Fig. F 12. The volttage V DS for switches S1 , S 2 , S3 , S 4 and wn in Figs. 13-18. 1 Also, the DC outtput S5 are show voltage is shoown in Fig. 188. Fig. 4 The prooposed topologyy and control sttrategy using PS SIM software. 194 Fig g. 7 ZVZCS waaveforms of I S 3 , VS 3 , and S3 drive signal. Fig g. 8 ZVZCS waaveforms of I S 4 , VS 4 and S 4 drive signal. I Iranian Journnal of Electrica al & Electronnic Engineerinng, Vol. 6, No. 3, Sep. 2010 Fig. 9 ZVZCS S waveforms off I S 4 , VS 4 and S5 drive signal. Fig g. 13 VDS for sw witch S1 . Fig. 10 Wavveform of Vout . Fig g. 14 VDS for sw witch S 2 . Fig. 11 Experiimental Circuit.. Fig g. 15 VDS for sw witch S3 . Fig. 12 Clock Signal. Nemati & Paakdel: New ZV VZCS Isolatedd Dual Series Resonant DC C-DC Converteer 1955 presented. This proposed converter combines the activeclamp circuit and the dual series-resonant circuit across the power transformer proposed in [12] with the topology proposed for soft switching dc-dc converter in [25]. The dual series-resonant circuit provides two resonant-current paths formed by the leakage inductance of the power transformer and the resonant capacitors. In addition, the turn-on and turn-off ZVS and ZCS mechanism of the switches by the active-clamp and auxiliary input and output switches, they reduce the switching losses and the reverse-recovery losses. Therefore, the proposed converter provides high efficiency at the full load. EMC Important techniques used in the converter circuit reduce EMI and increase performance in the circuit. Fig. 16 VDS for switch S 4 . Acknowledgment I would like to extend our greatest gratitude to the Islamic Azad University-Tehran South Branch, Young Researchers Club that supported me to do the present research project. Fig. 17 VDS for switch S5 . Fig. 18 Waveform of DC output voltage ( Vout ). 7 Conclusion A ZVZCS isolated dual series resonant dc-dc converter with high efficiency has been proposed. Analysis, design, and simulation and experimental results for the proposed converter have also been 196 References [1] Panov Y. and Jovanovic M. M., “Adaptive offtime control for variable frequency, soft-switched flyback converter at light loads,” IEEE Trans. Power Electron., Vol. 17, No. 4, pp. 596–603, Jul. 2002. [2] Zhang Y. F., Yang L. and Lee C. Q., “Spectral analysis and EMI comparison of PWM, quasiresonant, and resonant converters,” in Proc. IEEE Circuits Syst. , Vol. 1, pp. 1285–1288, 1995. [3] Jain P. K., St-Martin A. and Edwards G., “Asymmetrical pulse-width modulated resonant dc/dc converter topologies,” IEEE Trans. Power Electron.,Vol. 11, No. 3, pp. 413–422, May 1996. [4] Mao H., Abu-Qahouq J., Luo S. and Batarseh I., “Zero-voltage-switching half-bridge dc–dc converter with modified PWM control method,” IEEE Trans. Power Electron., Vol. 19, No. 4, pp. 947–958, Jul. 2004. [5] Huber R. and Jovanovic M. M., “Forward-flyback converter with current doubler rectifier: Analysis, design, and evaluation results,” IEEE Trans. Power Electron., Vol. 14, No. 1, pp. 184–192, Jan. 1999. [6] Wang C.-M., “Novel zero-voltage-transition PWM DC-DC converters,”IEEE Trans. Ind. Electron., Vol. 53, No. 1, pp. 254–262, Feb. 2006. [7] Wai R.-J., Lin C.-Y., Duan R.-Y. and Chang Y.R., “High-efficiency DC-DC converter with high voltage gain and reduced switch stress,” IEEE Trans. Ind. Electron., Vol. 54, No. 1, pp. 354– 364, Feb. 2007. [8] Matysik J. T., “The current and voltage phase shift regulation in resonantconverters with Iranian Journal of Electrical & Electronic Engineering, Vol. 6, No. 3, Sep. 2010 integraation control,”” IEEE Transs. Ind. Electroon., Vol. 544, No. 2, pp. 1237–1239, 1 A 2007. Apr. [9] Choi B., B Lim W., Bang B S. and Choi S., “Sm mallsignal analysis and controldesignn of asymmetrrical half-brridge DC-DC converters,” IEEE I Trans. Ind. I Electroon., Vol. 53, No. 2, pp.. 511–520, Apr. A 2006. [10] Lin B.-R. and Tsengg C.-H., “Anaalysis of paralllelconneccted asym mmetrical soft-switchhing converrter,” IEEE Trans. T Ind. Ellectron., Vol. 54, No. 3, pp. 1642–16553, Jun. 2007. [11] Lee J.--J., Kwon J.-M M., Kim E.-H H. and Kwon B.H., “Dual Seriies-Resonant Active-Claamp Conveerter,” IEEE Trans. T Ind. Ellectron., Vol. 55, No. 2, pp. 699-710, Feb. 2008. [12] Koo G.-B., Moonn G.-W. annd Youn M.-J., “Analyysis and desiign of phase shift full briidge converrter with seriees-connected two t transformer,” IEEE Trans. T Powerr Electron., Vool. 19, No. 2, pp. 411–419, Mar. 20044. [13] Redl R., R Sokal N. O. and Balogh L., “A noovel soft-sw witching fulll-bridge dcc/dc converrter: Analyssis, design connsiderations, and a experimenntal resultss at 1.5 kW, 100 1 kHz,” IEE EE Trans. Pow wer Electroon., Vol. 6, No. 3, pp. 408––418, Jul. 1991. [14] Jamalii S. and Parhaam A., “One Terminal Diggital Algoriithm for Addaptive Singgle Pole AuutoReclossing Based on Zero Seequence Volttage (ZSV),” Iranian Journal of Electrical and a Electroonic Engineering (IJEEE), Vol. 4, No. 3, pp. 71––78 , 2008. [15] Watson R., Lee F. C. C and Hua G. G C., “Utilizattion of ann active-clam mp circuit to t achieve soft switchhing in flybacck converterss,” IEEE Traans. Powerr Electron., Vol. V 11, No. 1, pp. 162–1169, Jan. 19996. [16] Li Q., Lee F. C., Buso B S. and Joovanovic M. M., “Largee-signal trannsientanalysiss of forw ward converrter with activve-clamp reseet,” IEEE Traans. Powerr Electron., Vol. V 17, No. 1, pp. 15–24, Jan. J 2002. [17] Spiazzzi G., Buso S. and Mattaveelli P., “Analyysis of thhe active-claampedsoft-sw witched forw ward converrter without output o filter,”” in Proc. IE EEE Powerr Electron. Sppec. Conf., Vol. V 5, pp. 38229– 3835, 2004. 2 [18] Wai R.-J., R Liu L.--W. and Duaan R.-Y., “Hiighefficiency voltage--clamped DC C-DC conveerter with reeduced reversse-recovery cuurrent and switch voltagee stress,” IEE EE Trans. Indd. Electron., Vol. V 53, Noo. 1, pp. 272–2280, Feb. 20066. [19] Chen T. T M. and Cheen C. L., “Analysis and dessign of asyymmetrical haalf bridge flyyback convertter,” Proc. Inst. Electr. Eng.—Electtr. Power Apppl., Vol. 1449, No. 6, pp. 433–440, Noov. 2002. [20] Lee S.-S., Han S.-K K. and Moon G.-W., G “Analyysis and design d of asyymmetrical ZVS Z PWM half h bridge forward coonverter withh flyback type t transformeer,” in Procc. IEEE Pow wer Electron. Spec. Conf nf., Vol. 2, pp. 1525–1530, 2004. 2 [2 21] Shoyama M., Li G G., and Ninomiya N T.,, “Applicatiion of com mmon-source active-clampp circuit to various dc–dcc converter to opologies,” inn Proc. IEE EE Power Eleectron. Spec. Conf., C Vol. 3,, pp. 1321––1326, 2003. [2 22] Jain M., Daniele M M. and Jain P. K., “A A bidirectionnal dc–dc coonverter topollogy for low w power application,” a IEEE Tra ans. Powerr Electron., Vol. 15, No. 4, pp. 595–60 06, Jul. 2000. [2 23] Chen M. and Sun J.,, “A general approach too averaged modeling aand analysiss of active-clamped converters,” c inn Proc. IEEE E Appl. Powerr Electron. Conf., Vol. 2,, pp. 1359–1365, 2005. [2 24] Dixon L. H., “Magneetics design for f switchingg power suppplies,” Unitroode Seminar, 2001. [2 25] Rahimi Kh., K Pakdel M.., “A New ZV VZCS Isolatedd DC-DC Converter,” C iin Proc. IEE EE ICIT2009. Conf., Australia, Feb. 22009. [2 26] Mohammaadpour A. , M Mokhtari H. and a Zolghadrii M.R., “Coontrol of Seriees Resonant Converter C withh Robust Performance P A Against Load d and Powerr Circuit Components C Uncertaintiees,” Iraniann of Electrrical Journal and Electronicc Engineeriing(IJEEE), V Vol. 5, No. 4, pp. 244–252,, 2009. [2 27] Lee J.-J. and Kwon B B.-H., “DC-D DC converterr using a multiple-couple m ed inductor fo or low outputt voltages,”” IEEE Transs. Ind. Electrron., Vol. 54,, No. 1, pp. 467–478, Febb. 2007. [2 28] Nemati A., EMC in Electtronics andd Communiccative System ms (Digital Circuit C Designn of high Frequency), Amirkabir University U off Tehran Polytechnic Press, 20 008; ISBN:: 97896446633362. Abbas Nemati, He receiived the M.Sc.. degree in Electronic Eng gineering from m versity Tehran n the Islamic Azad Univ South Brranch in 20 005. He hass published the first bo ook in EMC C Engineerin ng that pu ublished by y Amirkabirr University of o Technology,, Tehran, Iraan. He is the faaculty memberr at the Deepartment of Electrical E and d Eleectronics Engin neering and thee head of Youn ng Researcherss Clu ub in Islamic Azad Univeersity Miyaneh h Branch; Hee teaaches the proffessional lesso ons of the B.Sc, degree in n Eleectronics and Communicatiion engineerin ng in Islamicc Azzad University Miyaneh Bran nch. He also is i the memberr of Shiny Talent Office and Y Young Researcchers Club in n n South Branch h. His research h Islaamic Azad Uniiversity Tehran inteerests include EMC, EMI R Reduction, high h-power PWM M con nverters, modeling and con ntrol of power converters,, miccrocontrollers and electronicc drives. He haas published 5 IEE EE technical paapers. Nemati & Paakdel: New ZV VZCS Isolatedd Dual Series Resonant DC C-DC Converteer 1977 Majid Pakdel He received the B.S. degree from the Amirkabir University of Technology, Iran, in 2005 and the M.S. degree from the Isfahan University of Technology, Iran, in 2007. He is an instructor at the Department of Electrical and Electronics Engineering, Islamic Azad University, Miyaneh Branch. His research interests include high-power PWM converters, modeling and control of power converters, applied digital control, finite element analysis, microcontrollers and electrical drives. He has published one journal and 12 IEEE technical papers. 198 Iranian Journal of Electrical & Electronic Engineering, Vol. 6, No. 3, Sep. 2010