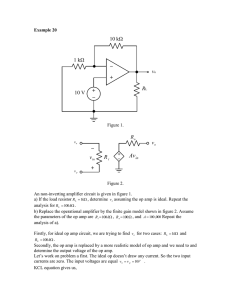

R Vi RC C Vo

advertisement

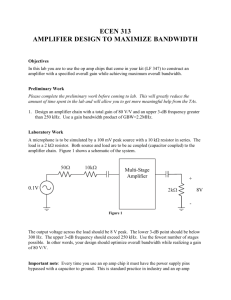

622(ESS) Fall’15 Due: September 29, 2015 HOMEWORK ASSIGNMENT # 2 Problem 1. a) Obtain the transfer function of the compensated integrator when As GB s p RC C R Vi A(s) Vo b) Determine the value of RcC to yield an optimal integrator response. c) Design A(s) with a two-stage amplifier with a GB=2x107Hz using 0.18m CMOS technology. Then simulate the integrator circuit for 1/RC=2106. Plot the resulting magnitude, group delay and phase frequency response. Also, include the plot of a step response. Problem 2. -1 Ideal Ro1 RQ C1 A1 A2 Vi i) C2 Ro2 Vo RBP Obtain the transfer function for A i s GBi , i=1,2. Determine the expression of s pi the actual Qa and oa as a function of the ideal Qo and ii) iii) Design a bandpass filter of Qo=5 and o 2 4 105 r s and Ho 1. Use the op amp designed in Prob. 1c). Using op amp macromodels verify the transistor level results. Obtain the minimum GB to yield a Q of 5%. Problem 3. You have designed and fabricated a highly linear ADC for audio and you need to test it. Unfortunately, once in the lab you realize that your frequency generator (for a 1KHz sinusoidal) has higher distortion than that of your ADC. To solve this problem you decide to build a low pass 2nd order filter to precondition the ADC input signal. However, you can only use either a TowThomas or Sallen-Key topologies for your low pass. Use VerilogA macromodels to decide which structure (Tow Thomas vs. Sallen-Key) can give you better linearity (and better chances to publish your ADC) assuming that you can model your amplifier (OPAMPs) using: v out a o a 1 v in a 2 v in2 a 3 v 3in Use a previous transistor-level two-stage Miller amplifier to extract the an coefficients following [1] and the dominant and non-dominant pole of your op amp (Hint: you can use the laplace_nd VerilogA function to model the op amp frequency response). Compare the two topologies assuming: 1) You can only use the SAME op amp in both cases. 2) For the worst topology in 1), use the models to find out what characteristics (GBW?) different op amp has to have to match the linearity of the best topology. Which solution do you think will consume the less power, the winner in 1) or the topology using the better op amp? Why? 3) Modify your VerilogA models to include noise (Hint: look into the white_noise function and remember that noise is additive). Find a commercial amplifier that meets the GBW requirements of 2) and use the noise density from its datasheet. Find out the THD+N of the filter, is this value acceptable? Consider the characteristics (THD+N) of the equipment you will be using for measurement (you have an AP System One audio analyzer). [1] “Distortion in elementary transistor circuits,” W. Sansen, IEEE Trans. Circuits Syst. II, vol. 46, no. 3, pp. 315-325, March 1999.