A 5.3μA Quiescent Current Fully-Integrated Low

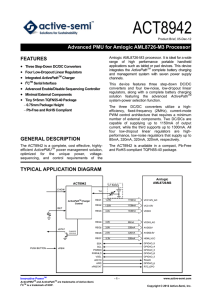

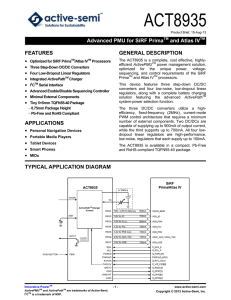

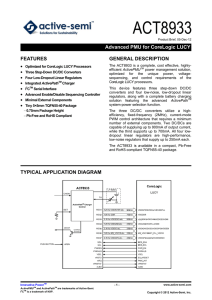

advertisement

A 5.3µA Quiescent Current Fully-Integrated Low-Dropout (LDO) Regulator with Transient Recovery Time Enhancement Paul M. Furth, Srikar Krishnapurapu, Sri Harsh Pakala and Mohammad A. Haque VLSI Laboratory, Klipsch School of Electrical and Computer Engineering, New Mexico State University, Las Cruces, NM 88003, USA Email: pfurth@nmsu.edu, srikar89@nmsu.edu, sriharsh@nmsu.edu and atiqul@nmsu.edu Abstract— A new technique to decrease the transient recovery time in a very low-quiescent current low-dropout (LDO) voltage regulator is introduced. The new Transient Recovery Time Enhancement (TRTE) block comprises a voltage-to-current converter, current comparator and an NMOS output transistor. The proposed LDO using the TRTE block was fabricated in a 0.5-µm 2P3M CMOS process. The circuit operates at a total quiescent current of 5.3 µA with a maximum load current of 50 mA while supplying a regulated output voltage of 1.5 V to a 100 pF load. Experimental results indicate a drop-out voltage of 123 mV with an average recovery time of 5.22 µs under maximum load current changes. Index Terms—low power, low-dropout (LDO) regulator, slewrate enhancement. I. I NTRODUCTION Modern portable electronic devices such as cell phones and tablets are complex systems which require multiple supply voltages for powering different sub-blocks. For the sake of higher levels of integration, achieving on-chip regulation to supply ripple-free voltages for sensitive analog blocks becomes a prime necessitiy. For such applications, low-dropout regulators (LDOs) can be ideal system-on-chip (SoC) solutions owing to their simple structure and lack of external components [1]–[11]. Low quiescent current and low dropout voltage are important design characteristics for an LDO, as most portable applications strive for prolonged battery life. The requirement of low-quiescent current inevitably reduces the slew rate capability of the LDO. Another constraint is the need for a low dropout voltage, forcing the use of a large power transistor, which tends to deteriorate the LDO’s transient behavior. In recent literature, several techniques exist which improve an LDO’s transient behavior with no change in quiescent current consumption at minimum load currents [6]– [11]. Adaptive biasing and capacitive coupling are notable among these reported techniques. This paper presents an ultra-low quiescent current LDO regulator using a recovery-time enhancement technique implemented in a 0.5-µm CMOS process. As shown in Fig. 1, the proposed enhancement block creates a push-pull output stage during transients in conjunction with the PMOS pass element. Section II discusses the operation of the LDO. Section III presents the simulation results of the proposed circuit. Hardware measurements of the system are given in Section IV. Finally, Section V draws conclusions based on performance comparisons with state-of-the-art work. VREF Buffer Pass Element Error Amplifier VA VFB VB A1 R F1 Sourcing VOUT R F2 V-to-I I TR Sinking VN I REF Transient Recovery Time Enhancement (TRTE) Circuit Fig. 1. Conceptual block diagram of proposed low-dropout (LDO) regulator with Transient Recovery Time Enhancement (TRTE) block. II. C IRCUIT D ESCRIPTION The conceptual block diagram of the proposed LDO is shown in Fig. 1. The system consists of a reference buffer, an error amplifier, a PMOS pass element and finally the Transient Recovery Time Enhancement (TRTE) block. The error amplifer is a CMOS source cros-coupled pair with a wide-swing current mirror. As the input impedance of the error amplifier is low, a reference buffer is needed to drive the error amplifier. The output stage is a PMOS pass element in order to achieve a very low dropout voltage. During the sourcing phase, there is therefore no slew-rate limitation. But in order to ensure that the LDO is not slew-rate limited during the sinking phase, we have introduced the TRTE block. This block consists of a voltage-to-current converter, a current comparator and an NMOS transistor at the output stage. The feedback achieved through the TRTE block is negative. A. Circuit Description and Operation The circuit implementation of the proposed LDO regulator is shown in Fig. 2. The three main stages - reference buffer, error amplifiier and pass element - are from the LDO proposed in [12], which is based on the high slew-rate error amplifier LDO from [1]. Transistors M1 -M12 form the source crosscoupled error amplifier with the wide-swing current mirror. Input terminals of the error amplifier are nodes VA and VF B ; the output terminal is node VB . The reference buffer contains transistors M15 -M22 with the positive input terminal connected to VREF . The resistive divider formed by resistors RF1 M 17 VIN M 19 M 18 M 10 M 11 VFB 3IB 3IB VA M 15 VREF M 16 M5 RF1 IB VBIAS M 22 IB IB RF2 M 21 M4 M3 IB M7 IB M2 M1 CC1 RC1 IB V BIAS CC2 VN M8 M9 0 V BIAS (x4) (x6) M 14 M 12 M 20 M 6 Reference Buffer VOUT IB VSS IREF MN Transient Recovery Time Enhancement (TRTE) Circuit Error Amplifier Schematic of proposed low-dropout (LDO) regulator with Transient Recovery Time Enhancement (TRTE) block. B. Transient Recovery Time Enhancement (TRTE) Circuit The proposed LDO regulator contains the Transient Recovery Time Enhancement (TRTE) block. This block is realized by transisors M13 , M14 and MN . It enables the LDO to sink large amounts of current during a transient overshoot event. A copy of the current through transistor M7 , on the right side of the source cross-coupled differential amplifier, is created through mirrors M8 /M9 and M10 /M13 . In steady-state conditions, the mirrorred current through transistor M13 is equal to IB . This current is compared to a reference current (Iref ) of 2IB created by transistor M14 . Since 2IB >> IB , node VN is pulled to VSS , placing transistor M14 in the triode region and the NMOS output transistor MN in cutoff. As such, the additional quiescent current of the TRTE circuit is only IB , such that the total quiescent current for the LDO is 13IB . During a transient overshoot event, that is, when VOU T = VF B exceeds VA , transistor M7 passes current greater than IB . As the source cross-coupled amplifier is not slew-rate limited, the current through transistor M7 can greatly exceed IB . This current is mirrored through M8 /M9 and again through M10 /M13 to the current comparator at node VN . As soon as the current through M13 exceeds Iref , node VN is pulled high, turning on output transistor MN , which pulls node VOU T back towards equilibrium. Transistor MN is not slew-rate limited, so its output current can be much higher than IB . Moreover, capacitors CC 2 and CC 3 help pull up node VN during a transient overshoot event. When VOU T increases, node VN is pulled up through CC 2 . Through feedback, node VB is driven high, which also pulls up node VN throughs CC 3 . During a transient undershoot event, through feedback, node VB is driven low, turning on pass transistor MP ASS with its inherent ability to pass large amounts of current. During this phase, the TRTE block is dormant, as the output NMOS transistor MN is in cut off as described earlier. III. S IMULATION R ESULTS The proposed LDO in Fig. 2 was simulated under nominal conditions of CL = 100 pF, VIN = 2 V, and VOU T = 1.5 V. Simulated open-loop gain and phase plots are given in Fig. 3 under the condition that ILOAD = 1 mA. The calculated phase and gain margins are 91.5o and 12.5 dB, respectively. Over the entire range of load current from 1 µA to 50 mA the minimum phase and gain margins are 50.3o and 9.8 dB, respectively. *+,-./012 and RF2 allows for dynamic voltage scaling [12]. Transistor MP ASS forms the pass element of the LDO. For the purpose of achieving a stable transient response, three compensation networks are utilized in this circuit. RC1 and CC1 form the dominant Miller compensation with nulling resistor. Capacitors CC2 and CC3 assist the transient recovery enhancement circuit through negative feedback. *C.A.!#B&.01 &" *+,-.A.()B##.01 " EF*9.A.D()B'.G?@ ï&" ï!"" " !" 34+56./7682 Fig. 2. IB CC3 VB IB IB M PASS M 13 (x6) ! !" # !" $ !" % !" & !" ' !" ( !" !" ) " ï!"" 3C.A.D!B%).068:665 ï#"" ï$"" " ! !" # !" $ % !" 9:6;<6-=>./?@2 !" & !" ' ( !" !" !" Fig. 3. Simulated AC plots at ILOAD = 1 mA and VIN = 2 V. !" ) The simulated dropout voltage (VDO ) is 125.1 mV, measured according to the definition from [13] VDO = (VIN − VOU T )|VOU T =VOU T ,max −100mV (1) Recovery time is defined as the time from the maximum (minimum) value of VOU T during an overshoot(H) (undershoot(L)) event to the time that VOU T settles within 1% of the final value [14]. Average recovery time TR is defined as TRH + TRL TR = (2) 2 Line transient simulations are performed with VIN varying from 2 to 2.8 V with rise and fall times of 100 ns at ILOAD = 1 mA. Fig. 4 shows the simulated line transient response, which indicates an average recovery time of 4.8 µs. Simulated values for line overshoot, undershoot and ∆VOU T are 298.9 mV, 280.6 mV and 579.5 mV, respectively. Load transient response simulations were performed with ILOAD varying from 1 µA to 50 mA with rise and fall times Input Pulse 55 Fig. 4. 1 mA. 20 1.8 Undershoot = 280.6 mV 1.6 1.4 VOUT (V) Overshoot = 298.9 mV 15 Time (!s) 70 TRL = 3.7 !s 1.2 55 6VOUT = 579.5 mV 60 65 Time (!s) 70 Simulated line transient with trise = tf all = 100 ns at ILOAD = of 100 ns at VIN = 2 V. Load undershoot, overshoot and ∆VOU T were found to be 336 mV, 277 mV and 613 mV, respectively. The simulated load transient response shows a fast average recovery time of 3.75 µs, as seen in Fig. 5. ILOAD (mA) Load Current 40 20 0 4 1.8 1.6 1.4 1.2 4 Undershoot = 336 mV T RL 6 8 = 3.3 !s 10 12 Time (!s) 14 16 20 0 55 60 65 70 75 80 85 90 Load Transient Response at Falling Edge 1.8 1.6 1.4 1.2 55 6VOUT = 613 mV T RH = 4.2 !s Fig. 7. Overshoot = 277 mV 60 65 70 75 Time (!s) 80 85 90 The proposed LDO was fabricated in a 0.5-µm 2P3M CMOS process with an active area of 0.175 mm2 . The chip micrograph is shown in Fig. 6. Chip micrograph of proposed LDO. The measured quiescent current of the LDO is 5.3 µA. The measured dropout voltage VDO is 123 mV. Fig. 7 shows the measured line transient response of the LDO. A small dip is seen after the rising edge of VIN . This dip is due to the 50 Ω source impedance of the instrument producing the pulse at VIN . In simulation, the effect of adding a 50 Ω resistor in series with VIN is to decrease overshoot from 590 mV to 572 mV and increase recovery time from 4.2 µs to 4.8 µs. The measured ∆VOU T,line and average recovery time (TR ) for line transients are 594 mV and 5.4 µs, respectively. The measured load transient response can be seen in Fig. 8. The measured ∆VOU T,load is 585 mV. The average recovery time (TR ) is 5.22 µs. V. D ISCUSSION AND C ONCLUSION In this section, the proposed LDO’s performance is compared with state-of-the-art LDO’s in the literature and summarized in in Table I. For the sake of quantifying the performance of an LDO, various figures of merit (F OM s) have been introduced. As there is no industry-standard F OM , the appropriate choice depends on the application of the LDO. 20 25 30 35 Line Transient Response TRH = 7.15 !s 1.5 40 45 TRL = 3.7 !s 6VOUT = 594 mV 10 15 20 25 30 Time (!s) 35 40 45 Measured line transient response of the proposed LDO regulator. Load Current 40 20 0 5 10 2 15 20 25 Load Transient Response 6VOUT = 585 mV 30 35 TRH = 6.8 !s 1.5 TRL = 3.65 !s 5 Fig. 5. Simulated load transient with trise = tf all = 100 ns at VIN = 2 V. IV. H ARDWARE M EASUREMENT R ESULTS Fig. 6. 15 40 6 8 10 12 14 16 Load Transient Response at Rising Edge VOUT (V) VOUT (V) ILOAD (mA) Load Current 10 2 5 VOUT (V) 1.4 10 65 ILOAD (mA) VOUT (V) VOUT (V) 1.6 5 60 Line Transient Response at Falling Edge TRH = 5.9 !s 1.2 2.8 2.6 2.4 2.2 2 5 VIN (V) VIN (V) VIN (V) 2.8 2.6 2.4 2.2 2 5 10 15 20 Line Transient Response at Rising Edge 1.8 Input Pulse Input Pulse 2.8 2.6 2.4 2.2 2 10 15 20 Time (!s) 25 30 35 Fig. 8. Measured load transient response of the proposed LDO depicting fast recovery times. For emphasizing the importance of load transient ∆VOU T , [6] introduces F OM 1 which attempts to normalize ∆VOU T by rise and fall times of �the load current, � ∆VOU T ∗ IQ F OM 1 = K (V ) (3) ∆ILOAD where K is defined as rise time ratio, trise /trise,min . Parameter trise is the average rise and fall time used when measuring load transient and trise,min is the minimum average rise and fall time among the compared LDOs. However, as evidenced from Figs. 10 and 11 from [6] and Figs. 6(c) and 6(g) from [4], measured ∆VOU T is not linear with respect to the rise time ratio, but rather sublinear. Indeed in [6] a ten-fold change in trise resulted in only 2.5x change in ∆VOU T . According to Table I, we see that the proposed LDO has a higher F OM 1 than most designs. This is because F OM1 does not take into account the fabrication process, thus, greatly skewing the advantage towards designs fabricated in faster technologies. Hence we propose F OM 2 , which incorporates a sublinear relationship between ∆VOU T and K, substitutes the total minimum ground current (IQ + IL,M IN ) for the quiescent current (IQ ) and is also process normalized by an estimated F O4 inverter delay [2]. F OM 2 is given by � � 1/3 ∆VOU T (IQ + IL,M IN ) (V /µs) (4) F OM 2 = K F O4Delay ∗ ∆ILOAD Based on F OM2 , the proposed LDO performs well, with only LDOs from [8] and [4] posting lower values. Whereas F OM1 and F OM2 emphasize an LDO’s load transient performance, there exists another figure of merit, which emphasizes recovery time [1], � � IQ F OM 3 = TR (ns) (5) IL,M AX TABLE I P ERFORMANCE C OMPARISON OF LDO S BASED ON F IGURES OF M ERIT (F OM s) [2] Year Technology (nm) Chip Area(mm2 ) IL,M AX (mA) IL,M IN (µA) VDO (mV) VOU T (V) CL (pF) IQ (µA) ∆VOU T (mV) ∆ILOAD (mA) TR (µs) Avg. trise (µs) Rise time Ratio (K) F O4Delay (ps) F OM1 (V) F OM2 (V/µs) F OM3 (ns) F OM4 (106 ) 2005 90 0.51 100 0 200 0.9 600 6000 90 100 0 0.0001 1 23 0.0054 234.78 0 0 [3] 2007 350 0.29 50 0 200 2.8 100 65 130 50 15 1 10000 90 1.6900 40.46 19.5 216.67 [1] 2007 180 0.09 50 50 100 0.9 100 1.2 700 49.95 2.8 0.35 3500 47 0.0589 231.79 0.067 61.07 [4] 2010 350 0.145 100 0 200 1.6 100 20 175 100 9 0.1 1000 90 0.0350 3.89 1.8 20.00 [5] 2010 350 0.155 66.7 670 200 1.2 1000 43 140 99 3 1 10000 90 0.9117 361.88 1.93 360 As seen in Table I, the proposed LDO again lags behind virtually every other LDO in F OM3 value, predominantly because of the lack of process normalization. Hence, we propose a new Figure of Merit (F OM 4 ), which is a process normalized version of F OM3 and which also incorporates the minimum ground current (IL,M IN +IQ ) a design needs to be stable. F OM 4 is given by F OM 4 = TR (IQ + IL,M IN ) (unitless) F O4Delay ∗ ∆ILOAD (6) With respect to F OM4 , the proposed LDO again performs well. Only LDOs in [2], [7] and [8] have lower values. Based on Table I, the proposed amplifier exhibits an F OM 2 (emphasizing ∆VOU T ) equal to 5.71 V/µs, third only to LDOs from [8] and [4], which have F OM 2 of 3.89 and 0.53 V/µs, respectively. Similarly, F OM 4 of the proposed amplifier (emphasizing TR ) is 5.1, lagging only LDOs from [2], [7] and [8], which have values of 0, 0.95 and 3.18, respectively. Thus, the only LDO with superior performance in terms of F OM 2 and F OM 4 is that reported in [2]. However, a direct comparison between the LDO in [2] and the proposed LDO is problematic. For example, the design in [8] is for VOU T of 1 V, which is very near the maximum supply voltage of a 65 nm process. Moreover the design in [8] has a VDO of 200 mV, which leads to a maximum efficiency of only 83.3%. By contrast the proposed LDO has VOU T equal to 1.5 V, 3x smaller than the maximum supply voltage and a VDO of 123 mV, leading to a maximum efficiency of 92.4%. In summary, a low-quiescent current fully-integrated LDO with transient recovery time enhancement (TRTE) has been presented. The proposed LDO with TRTE block is stable for current loads of 1 µA to 50 mA. The proposed TRTE block helps the LDO achieve a measured average load transient recovery time of 5.22 µs. Compared to designs from the literature, the proposed LDO achieves the best balance in terms of the proposed F OM2 , F OM4 and maximum efficiency. [6] 2010 90 0.019 100 3000 250 0.5 50 8 187 97 5 0.1 1000 23 0.0154 2521.27 0.4 6741.37 [10] 2011 130 0.03 50 0 100 0.8 5 1.33 850 50 18.5 0.2 2000 35 0.0452 8.14 0.492 14.06 [7] 2012 350 0.064 100 50 150 2.35 100 7 455 99.95 0.15 0.5 5000 90 0.1593 49.30 0.010 0.95 [8] 2013 65 0.017 100 0 200 1 100 0.9 68.8 100 6 0.3 3000 17 0.0019 0.53 0.054 3.18 [9] 2013 130 0.018 50 50 200 1 20 37.32 94 49.95 0.4 0.2 2000 35 0.1405 59.15 0.298 19.98 [11] 2013 350 0.04 100 100 200 1 100 1.2 475 99.9 2.7 1 10000 90 0.0571 115.19 0.032 30.39 This work 2013 500 0.175 50 1 123 1.5 100 5.34 585.2 49.99 5.225 0.1 1000 130 0.0625 5.71 0.558 5.1 R EFERENCES [1] T. Man, P. K. T. Mok, and M. Chan, “A high slew-rate pushpull output amplifier for low-quiescent current low-dropout regulators with transient-response improvement,” Circuits and Systems II: Express Briefs, IEEE Transactions on, vol. 54, no. 9, pp. 755–759, 2007. [2] P. Hazucha, T. Karnik, B. Bloechel, C. Parsons, D. Finan, and S. Borkar, “Area-efficient linear regulator with ultra-fast load regulation,” SolidState Circuits, IEEE Journal of, vol. 40, no. 4, pp. 933–940, 2005. [3] R. Milliken, J. Silva-Martinez, and E. Sanchez-Sinencio, “Full on-chip cmos low-dropout voltage regulator,” Circuits and Systems I: Regular Papers, IEEE Transactions on, vol. 54, no. 9, pp. 1879–1890, 2007. [4] E. Ho and P. K. T. Mok, “A capacitor-less cmos active feedback low-dropout regulator with slew-rate enhancement for portable on-chip application,” Circuits and Systems II: Express Briefs, IEEE Transactions on, vol. 57, no. 2, pp. 80–84, 2010. [5] P. Y. Or and K. N. Leung, “An output-capacitorless low-dropout regulator with direct voltage-spike detection,” Solid-State Circuits, IEEE Journal of, vol. 45, no. 2, pp. 458–466, 2010. [6] J. Guo and K. N. Leung, “A 6- µw chip-area-efficient outputcapacitorless ldo in 90-nm cmos technology,” Solid-State Circuits, IEEE Journal of, vol. 45, no. 9, pp. 1896–1905, 2010. [7] X. Ming, Q. Li, Z. kun Zhou, and B. Zhang, “An ultrafast adaptively biased capacitorless ldo with dynamic charging control,” Circuits and Systems II: Express Briefs, IEEE Transactions on, vol. 59, no. 1, pp. 40–44, 2012. [8] S. Chong and P. Chan, “A 0.9- µa quiescent current output-capacitorless ldo regulator with adaptive power transistors in 65-nm cmos,” Circuits and Systems I: Regular Papers, IEEE Transactions on, vol. 60, no. 4, pp. 1072–1081, 2013. [9] E. Ho and P. K. T. Mok, “Wide-loading-range fully integrated ldr with a power-supply ripple injection filter,” Circuits and Systems II: Express Briefs, IEEE Transactions on, vol. 59, no. 6, pp. 356–360, 2012. [10] M. Ho and K. N. Leung, “Dynamic bias-current boosting technique for ultralow-power low-dropout regulator in biomedical applications,” Circuits and Systems II: Express Briefs, IEEE Transactions on, vol. 58, no. 3, pp. 174–178, 2011. [11] X. Qu, Z.-K. Zhou, B. Zhang, and Z.-J. Li, “An ultralow-power fasttransient capacitor-free low-dropout regulator with assistant push-pull output stage,” Circuits and Systems II: Express Briefs, IEEE Transactions on, vol. 60, no. 2, pp. 96–100, 2013. [12] H. Valapala and P. Furth, “Analysis and design of fully integrated very low quiescent current ldos,” in Circuits and Systems (MWSCAS), 2012 IEEE 55th International Midwest Symposium on, 2012, pp. 230–233. [13] M. Day, “Understanding low drop-out ldo regulators,” in Texas Instruments, Dallas, 2002. [14] G. A. Rincon-Mora, “Current efficient, low voltage, low dropout regulators,” Ph.D. dissertation, Georgia Institute of Technology, November 1996.