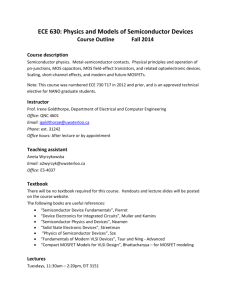

Report

advertisement