Analysis and Design of Inductive Coupling and Transceiver Circuit

advertisement

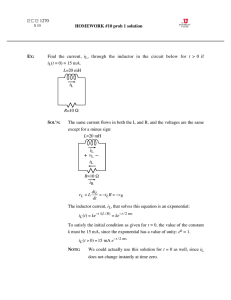

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 4, APRIL 2005 829 Analysis and Design of Inductive Coupling and Transceiver Circuit for Inductive Inter-Chip Wireless Superconnect Noriyuki Miura, Daisuke Mizoguchi, Takayasu Sakurai, Fellow, IEEE, and Tadahiro Kuroda, Senior Member, IEEE Abstract—A wireless bus for stacked chips was developed by utilizing inductive coupling among them. This paper discusses inductor layout optimization and transceiver circuit design. The inductive coupling is analyzed by a simple equivalent circuit model, parameters of which are extracted by a magnetic field model based on the Biot–Savart law. Given communication distance, transmit power, data rate, and SNR budget, inductor layout size is minimized. Two receiver circuits, signal sensitive and yet noise immune, are designed for inductive nonreturn-to-zero (NRZ) signaling where no signal is transmitted when data remains the same. A test chip was fabricated in 0.35- m CMOS technology. Accuracy of the models is verified. Bit-error rate is investigated for various inductor layouts and communication distance. The maximum data rate is 1.25 Gb/s/channel. Power dissipation is 43 mW in the transmitter and 2.6 mW in the receiver at 3.3 V. If chip thickness is reduced to 30 m in 90-nm device generation, power dissipation will be 1 mW/channel or bandwidth will be 1 Tb s mm2 . Index Terms—High bandwidth, inductor, low power, SiP, wireless bus. I. INTRODUCTION M ULTIFUNCTION and high-performance LSI systems are in increasingly strong demand in recent years. Typical applications are an application processor for three-dimensional (3-D) video games, an imaging processor for high-end digital cameras, a graphics card for personal computers, and so on. The important key to improve the performance of these LSI systems is high-bandwidth communication between functions, such as CPU and memory. Conventional system-on-a-board (SoB) implementation with a high-speed serial link techniques [1], [2] has difficulty to develop high-bandwidth interface due to its long inter-chip distance, which degrades data rate and channel density, or it requires higher power dissipation and area for circuits. On-chip network [3], [4] in system-on-a-chip (SoC) technology is one of the solutions to meet the demand. However, cost increase due to the complex embedded process is the problem of SoC. System in a package (SiP) can solve the problem and 3-D stacking structure reduces chip distance substantially ( 100 m), providing motivation to develop a low-cost low-power high-bandwidth interface. From this point of view, several interface technologies are reported [5]–[11]. Manuscript received August 30, 2004; revised January 24, 2005. N. Miura, D. Mizoguchi, and T. Kuroda are with the Department of Electronics and Electrical Engineering, Keio University, Yokohama 223-8522, Japan. T. Sakurai is with the Center for Collaborative Research, University of Tokyo, Tokyo 153-8505, Japan. Digital Object Identifier 10.1109/JSSC.2005.845560 In wired mechanical approaches, through-silicon via [5] or micro bump [6] technologies, issues are cost increase caused by additions in process complexity and yield degradation due to difficulty in screening a known good die (KGD). On the other hand, wireless approaches, wireless superconnect (WSC) by capacitive coupling (WSC-C) [8], [9] or inductive coupling (WSC-IIS) [10], [11] have many advantages over wired in terms of power, speed, and cost. The interface, a metal plate for capacitive coupling or a metal inductor for inductive coupling, can be implemented in a standard CMOS process without an additional mechanical process which allows significant cost reduction of fabrication and high-density channel arrangement by exploiting the process scaling. In addition, the noncontact interface removes a highly capacitive electrostatic discharge (ESD) protection device to reduce power, delay, and area. The absence of ESD protection and a high-pass filtering property of ac coupling solves the KGD problem [12], enabling test at the high operating frequency before assembly. However, capacitive coupling has a limitation. Since it is a voltage-driven scheme, it cannot provide large transmit power enough to communicate over long distance at low supply voltages in scaled devices. As a result, the capacitive coupled interface can be employed only in a case where two chips are stacked face-to-face in distance shorter than several microns. It cannot be used when a lower chip is mounted face down in an area bump package. Additionally, in an application where an upper chip has imaging sensors, the chip has to be stacked face-up, which also limits employing capacitive coupling. To overcome this limitation, WSC-IIS [10], [11] is developed for longer inter-chip communication. Fig. 1 illustrates the scheme. Chips are stacked face-up and inductively coupled by metal inductors to form a multidrop bus. Since power, ground, and clock can be provided by bonding wires in a face-up stacked structure, no complex mechanical process (through-silicon via or micro bump) is required, while it is required in a face-to-face structure. A transmitter and a receiver each have an inductor and the transmitter inductor is allocated in the receiver inductor for high layout density. Fig. 2 shows the metal inductor layout that reduces parasitic capacitance between metal layers [13]. Since inductive coupling is a current-driven scheme, transmit power can be increased for longer distance communication even at low supply voltages in scaled devices. In addition, transmission gain can be increased by increasing number of turns of the inductors by exploiting an increasing a level of the metal layers. Data rate of 1.2 Gb/s/pin in 300 m distance is reported in [10]. Power dissipation is 43 mW in a transmitter and 2.5 mW in a receiver. 0018-9200/$20.00 © 2005 IEEE 830 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 4, APRIL 2005 Fig. 3. Inductive nonreturn-to-zero (NRZ) signaling. Fig. 1. Wireless superconnect (WSC) with inductive inter-chip signaling (IIS). presented in Section VI. Finally, conclusions will be presented in Section VII. II. INDUCTIVE NRZ SIGNALING Fig. 2. Metal inductor layout. An ideal scaling scenario may be found if a chip thickness is scaled down. It is reported in [14] that substrate thickness is reduced 1.7 m without affecting transistor characteristics. Given communication distance, transmit power, data rate, and signal-to-noise ratio (SNR) budget, the metal inductor should be minimized for area reduction by optimizing layout parameters (diameter , width , space , and number of turns ). Smaller inductor layout yields higher bandwidth when the inductors are placed in an array. However, there is no theory for design optimization, since both electrical circuit and magnetic field are involved in designing the inductive coupling. In this paper, simple and yet accurate models for circuit and magnetic field design are discussed to derive a theory for optimizing inductor layout. Transceiver circuit design for the inductive nonreturn-to-zero (NRZ) signaling is described. The analysis and the design is verified and evaluated by measuring a test chip that was fabricated in 0.35- m CMOS technology. The rest of this paper is organized as follows. In Section II, the inductive NRZ signaling will be proposed. Section III will discuss an analysis of inductive coupling with an equivalent circuit and a magnetic field model, and these models will be verified. Section IV describes transceiver circuit design for the NRZ signaling. In Section V, the design and the analysis including the transceiver circuit are verified and evaluated by the measurement of inter-chip communications. The performance summary and scaling scenario of the proposed interface will be In a general wireless data communication, a carrier modulation technique is often utilized to improve SNR while it requires sophisticated RF/analog circuits (mixer, frequency synthesizer, passive filter, etc.) which increase power dissipation and area. On the other hand, since a transceiver of WSC-IIS communicates in close proximity, much higher SNR can be obtained without the carrier modulation. Therefore, we can utilize a kind of pulse modulation which eliminates circuit complexity significantly. Fig. 3 illustrates our proposed inductive NRZ signaling. A transmitter converts transition of baseband binary data Txdata to a bipolar pulse current . A receiver senses the pothrough inductive coupling with a sampling clock larity of Rxclk and recovers baseband data Rxdata. is not In the inductive NRZ signaling, a received signal generated when Txdata is held. To prevent metastable state, the sensitivity of the receiver should be set within an approwhen Txdata tranpriate range so that it can detect signal in sits, while it can ignore noise in when Txdata remains the same. Two receiver circuits are proposed to solve this problem in Section IV. III. ANALYSIS OF INDUCTIVE COUPLING A. Equivalent Circuit Fig. 4(a) depicts a proposed equivalent circuit of the inductive coupling. Since the receiver is designed to have high input impedance for received-voltage sensing, current through a receiver inductor is small enough to ignore self-induced voltage at the receiver inductor and induced voltage feedback to a transmitter from a receiver inductor. In addition, a coupling capacitor generated between inductors can be abbreviated because of long communication distance. From Fig. 4(a), transfer function is given by (1) MIURA et al.: INDUCTIVE COUPLING AND TRANSCEIVER CIRCUIT FOR INDUCTIVE INTER-CHIP WIRELESS SUPERCONNECT 831 Fig. 4. Electrical model of inductive coupling: (a) equivalent circuit; (b) frequency characteristics (L = L = 5 nH, C = 500 fF, C = 50 fF, R = R = 100 , k = 0:2, R = 50 ). Its frequency characteristic is depicted in Fig. 4(b). The transmitter inductor is modeled as a parallel resonator whose , and self-resonant frequency is given by by including transmitter’s output impedance, it behaves as a second-order low-pass filter. The inductive coupling functions as a differential operator, or a high-pass filter, whose . The receiver inductor is gain is determined by characterized as a low-pass filter whose cut-off frequency is . In total, the inductive coupling determined by behaves as a bandpass filter. Power/ground noise may be effectively cut off due to the filter characteristics. In inductive NRZ signaling, the input signal to the inductive which is given coupling is approximated by Gaussian pulse by Fig. 5. Characteristics of signals in inductive NRZ signaling in (a) time domain and (b) frequency domain. (2) is peak voltage, is time offset, and is pulse width where determined by data rate. Then, the frequency spectrum of is given by (3) Essentially, differential operation of inductive coupling is inbecomes the actual frequency evitable, therefore, spectrum to be analyzed. Fig. 5 describes the frequency spec. The peak frequency (fundamental) is trum of . Bandwidth of at least is required to damp given by the received signal and diminish inter-symbol interference (ISI). Fig. 6 shows that gain of the inductive coupling in high-freincreases. Therefore, a metal inductor quency decreases as should not be shared by the transmitter and the receiver, since . the transmitter exhibits large output capacitance for small Otherwise, fundamental as well as harmonics are attenuated and ISI is increased as shown in Fig. 6. B. Magnetic Field Modeling In order to extract the electrical parameters in (1), a theoretical model for analyzing magnetic field is developed, namely the current density fiber model. As depicted in Fig. 7, magnetic flux density is calculated by integrating contributions from all the Fig. 6. Received voltage when metal inductor is (a) shared and (b) not shared. current density fibers that are calculated by the Biot–Savart law. Self-inductances , , and mutual inductance are calculated by integrating penetrating though each inductor, and a . Since magcoupling coefficient is given by netic flux density generated by a square inductor is given by a superposition of magnetic flux density generated by four metal , can be easily obtained by calculation of only one lines, metal line. In addition, when metal inductors are aligned concan be also obtained by the same calculation becentrically, cause of the symmetry. This model is available to calculate when inductors are not aligned concentrically, which is equivalent to analyzing crosstalk between channels and it is demonstrated and evaluated by measurements in [15]. C. Experimental Result Accuracy of the models is examined by measuring metal inductors by the second and third metal layers and inductive coupling between the first and third metal layer in a test chip. Table I summarizes measured and calculated self-inductance of twolayer on-chip metal inductors. Calculation based on the current density fiber model has good agreement with the measurement since the error between them is about 5% in several inductor 832 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 4, APRIL 2005 (5) (6) (7) (8) (9) (10) Fig. 7. Current density fiber model for magnetic field modeling. TABLE I MEASURED AND CALCULATED SELF-INDUCTANCE OF METAL INDUCTORS Fig. 8. Measured and calculated S21 parameter of inductive coupling. layout parameters. The parameter of on-chip inductive coupling has been measured by a network analyzer and calculated by the proposed equivalent circuit model in Fig. 4(a) with replacing the current-controlled voltage source to a receiver infor 50- -terminated measurement. Fig. 8 shows ductance the results where good agreement between measurement and calculation are also found. D. Optimization of Inductor Layout Relations between electrical parameters ( , , , ) and layout parameters ( , , ) are approximately given by (4) where is communication distance between a transmitter and a receiver. In a face-to-back stacked structure, is almost determined by chip thickness. Parameters for two-layer metal inductors in 0.35- m CMOS process are used; wire space m, nH mm, pF mm , , and output capacitance of transmitter fF. is one of the layout parameters, but it should be the minimum value available in a fabrication process to provide large opening area of an inductor, because the opening area determines a coupling coefficient between inductors, which affects gain of inductive coupling much more than parasitic capacitance between metal lines. From (1), (4)–(10), received signal power is calculated. Layout parameters for an optimized inis miniductor are calculated and presented in Fig. 9 when mized under given conditions of communication distance, data ps), transmit power of rate of 1.25 Gb/s (pulse width ), and SNR budget of 20 dB. The noise 40 mW ( power assumed in this theory is thermal noise which is integrated and estimated as the same power of 20-mV-peak received dB denotes that received signal signal. Therefore, has 200-mV-peak voltage. The transfer function is maximized GHz). The within the operating frequency range ( transmitter and receiver inductors can be placed inside concentrically for high layout density. Because of the large output capacitance of the transmitter, the transmitter inductor is designed to have smaller self-inductance and series resistance to increase bandwidth, and as a result, metal wires should be wide. Therefore, the transmitter inductor should be placed inside of the receiver inductor concentrically. Otherwise, the opening area of the receiver inductor becomes small, which degrades coupling significantly. As shown in Fig. 9, inductor layout will linearly scale down as chip thickness scales. Increasing metal layers of the metal inductor contributes to increasing the gain of inductive coupling, which enables reducing the transmit power or area. IV. TRANSCEIVER CIRCUIT DESIGN A. NRZ Signaling and received voltage Waveforms of transmitted current in the inductive NRZ signaling are illustrated in Fig. 3. A transmitter is a kind of pulse generator providing bipolar pulse based on transition of Txdata. A receiver samples current induced by through the inductive coupling and voltage recovers data Rxdata. However, since is not generated when Txdata continues, the sensitivity of the receiver should be set within appropriate ranges so that it can detect signals in MIURA et al.: INDUCTIVE COUPLING AND TRANSCEIVER CIRCUIT FOR INDUCTIVE INTER-CHIP WIRELESS SUPERCONNECT Fig. 12. Sensing-time (T 833 ) control in (a) L = 0:4 m, (b) L = 1:2 m. Fig. 9. Optimal inductor layout parameters derived from theoretical models = 50 , SNR = 20 dB). ( = 300 ps, R Fig. 10. Transmitter. Fig. 13. Fig. 11. Sensing-time control receiver. when Txdata transits, while it can ignore noise in data remains the same. when Tx- B. Transmitter A proposed transmitter circuit is depicted in Fig. 10. A simple H-bridge circuit with a delay buffer is utilized to provide bipolar pulse current . flows in the transmitter inductor at the transition of Txdata for the period of delay time of a delay buffer. The delay buffer can be implemented with an odd-stage inverter chain. When the transceiver is not transmitting data, the loop of the transmitter inductor is opened by Tx/ . Otherwise, the induced current in the transmitter inductor counteracts the change by of magnetic field and reduces the received in a stacked bus structure as shown in Fig. 1. C. Receiver A sense-amplifier flip-flop circuit, shown in Fig. 11, is adopted as a receiver to detect small induced voltages. is k ) for voltage sensing. designed to have high resistance ( Due to this high resistance, current flow in a receiver inductor Majority vote receiver. becomes less than 1 mA so the receiver inductor does not affect coupling in a stacked bus structure. Two circuit techniques are proposed to solve the above-mentioned problem of metastable state in the inductive NRZ signaling. One is a sensing-time-control receiver, shown in Fig. 11. ) distinguishes between signal and noise. Sensing time ( As shown in Fig. 12, the receiver operates erroneously with too when the same data continues, while with too short long , the signal may not be able to be received correctly. Time under process variations can be increased by margin in enlarging channel length of the differential pair transistors, but is controlled by a duty at the cost of speed degradation. controller. The other circuit is called a majority vote receiver, shown in Fig. 13. Two sense amplifiers are employed; one is likely to output “high” and the other “low.” Rxdata is determined by majority vote as shown in the table in Fig. 11. The offset is designed by employing different channel length to differential pair transistors in the sense amplifiers. As shown in the SPICE mV is secured with simulation in Fig. 14, noise margin of m and 0.65 m for the differential pairs. The above-mentioned two receiver circuits with the transmitter are simulated by using SPICE. Noise is modeled as white Gaussian noise and given by voltage sources connected . The transceiver is simulated at receiver’s input resistance pseudorandom binary with transmitting and receiving sequence (PRBS) data. The shmoo plots in Fig. 15 are derived 834 Fig. 14. IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 4, APRIL 2005 Asymmetric differential pair in majority vote receiver. Fig. 16. Calculated BER dependence on communication distance. TABLE II TRANSCEIVERS WITH METAL INDUCTOR AND LAYOUT PARAMETERS Fig. 15. Shmoo plots: (a) sensing-time-control receiver; (b) majority vote receiver. by sweeping and the delay of receiver’s clock . The majority vote receiver operates faster than the sensing-time control receiver by 6% as shown in Fig. 15. V. INTER-CHIP COMMUNICATIONS The dependence of SNR on communication distance is calculated by the theoretical models and depicted in Fig. 16. As the diameter of the receiver inductor increases and the communication distance decreases, SNR is improved. When SNR is increased, the sense amplifier in the receiver recovers data faster, so the PASS area in Fig. 15 is shifted below. As a remargin) of the sensing-time-consult, the timing margin ( trol receiver at ps is increased up to 200 ps when dB. By using Gaussian distribution of the clock and data jitter in measurement system, the bit-error rate (BER) can be calculated by the timing margin. A test chip was fabricated in 0.35- m CMOS technology. Table II summarizes microphotographs of our implemented prototype transceivers with metal inductors. The layout parameters are the same as that utilized in the calculation in Fig. 16. The transmitter inductor has three turns and the receiver inductors with 100, 200, and 300 m diameter have four, five, and six turns, respectively. Fig. 17 shows a microphotograph of an experimental setup for evaluating inter-chip communication. We measured the test chip in a laboratory room without any special thermal/air control and electromagnetic shielding. Chips were mounted face-up on each printed-circuit board. Clock, power, and some digital control signals were provided through bonding wires. Transmitting data was generated by an on-chip linear feedback shift register (LFSR). Clock timing and duty ratio were changed by 70-ps steps by digital control. The upper board and the lower board with the chip were placed face-to-face. Communication distance was changed by moving the upper chip up m). In and down by a micromanipulator in a fine pitch ( this experimental setup, the chips communicate in face-to-face, not face-to-back, mounting, described in Fig. 1. The effect of the silicon wafer in the propagation was not considered. However, based on a simulation study by a 3-D electromagnetic field solver reported in [10], the difference can be negligible because the permeability of materials used in CMOS process (Si, SiO ) are the same as air. Reflection and absorption of the materials can be ignored. In addition, the signal attenuation caused by eddy current in a substrate is around 5% in the simulation results. The measured maximum communication distance is shown in Fig. 18. The measured results have good agreement with the calculated results in Fig. 16. A curve of denotes dB. Since the receiver’s sensitivity is set to ignore noise, the receiver cannot receive any data when the signal level is attenuated to smaller than the noise level ( ). As a result, no data transition is monitored in the received data. By increasing SNR to 26 dB and the timing margin to is achieved when communi200 ps, BER of less than cation distance is reduced to less than 60, 120, 150 m when m, respectively. The maximum data rate is 1.25 Gb/s/ch. Power dissipation is 43 mW in the transmitter MIURA et al.: INDUCTIVE COUPLING AND TRANSCEIVER CIRCUIT FOR INDUCTIVE INTER-CHIP WIRELESS SUPERCONNECT Fig. 17. 835 Microphotograph of experimental setup of inter-chip communications. TABLE III PERFORMANCE SUMMARY AND COMPARISON VI. PERFORMANCE SUMMARY AND SCALING SCENARIO Fig. 18. Measured maximum communication distance. and 2.6 mW in the receiver at 3.3 V. The power dissipation in the transmitter is linearly decreased by decreasing the clock rate and the switching activity due to the NRZ signaling. Since the receiver is sensitive to process variation, several chipsets have been tested. The effect of process variation cannot be found in the measurement because the receiver is designed in a longer channel length to overcome the variation. Table III summarizes the performance of the proposed scheme and compares it with wired approaches developed in 0.35- m CMOS [1], [2]. Data rate of 1.25 Gb/s with power dissipation of 46 mW was achieved. The minimum area for the interface is 0.025 mm at communication distance of 60 m. Compared to [1] and [2], the power dissipation is reduced by 25% and the area is reduced by a factor of 5 and 32, respectively. A scaling scenario of the proposed scheme can be derived by scaling the parameters used in the theoretical analysis. In 90-nm device generation, the number of metal layers is increased to seven, and supply voltages are scaled to 1 V. By utilizing a 90-nm BSIM model in SPICE simulation, data rate and power dissipation for inter-chip communications of three stacked chips were calculated, and are summarized in Table IV. Scaling in chip thickness as well as device size is effective in decreasing power dissipation and increasing bandwidth. When six metal layers are used for the metal inductor, the gain of inductive coupling can be increased by three times and, due to the voltage scaling by a factor of 3.3, 10 power reduction is obtained in total. In addition, if chip thickness is reduced to 30 m further 4 power reduction is obtained, as a result, power dissipation will be reduced to 1.1 mW/channel or bandwidth will be increased to 1 Tb s mm with power dissipation of 4.2 W by arranging 200 transceivers in 1 mm . 836 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 4, APRIL 2005 TABLE IV SCALING SCENARIO VII. CONCLUSION Inductive coupling for inter-chip communications has been investigated. Theoretical models for circuit design and magnetic field analysis were proposed, and their accuracy has been verified by measurement. A theory to minimize inductor layout size has been derived. The loop of a transmitter inductor was opened in the receiving signal to keep the signal from being attenuated by induced current in the transmitter inductor. Two receiver circuits were investigated to distinguish between signal and noise in the inductive NRZ signaling. The analysis and design has been verified and evaluated by measuring a test chip in 0.35- m CMOS. The maximum data rate was 1.25 Gb/s/channel. Power dissipation was 43 mW in the transmitter and 2.6 mW in the receiver at 3.3 V. ACKNOWLEDGMENT The VLSI chip in this study was fabricated in the chip fabrication program of the VLSI Design and Education Center (VDEC), University of Tokyo, with collaboration by Rohm Corporation and Toppan Printing Corporation. REFERENCES [1] G. W. Bosten, “Embedded low-cost 1.2 Gb/s inter-IC serial data link in 0.35 mm CMOS,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2000, pp. 250–251. [2] E. Yeung and M. A. Horowitz, “A 2.4 Gb/s/pin simultaneous bidirectional parallel link with per-pin skew compensation,” IEEE J. Solid-State Circuits, vol. 35, no. 11, pp. 1619–1628, Nov. 2000. [3] S.-J. Lee, S.-J. Song, K. Lee, J.-H. Woo, S.-E. Kim, B.-G. Nam, and H.-J. Yoo, “An 800 MHz star-connected on-chip network for application to systems on a chip,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2003, pp. 468–469. [4] K. Lee, S.-J. Lee, S.-E. Kim, H.-M. Choi, D. Kim, S. Kim, M.-W. Lee, and H.-J. Yoo, “A 51 mW 1.6 GHz on-chip network for low-power heterogeneous SoC platform,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2004, pp. 152–153. [5] J. Burns, L. McIlrath, C. Keast, D. P. Vu, K. Warner, and P. Wyatt, “Three-dimensional integrated circuits for low-power, high-bandwidth systems on a chip,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2001, pp. 268–269. [6] T. Ezaki, K. Kondo, H. Ozaki, N. Sasaki, H. Yonemura, M. Kitano, S. Tanaka, and T. Hirayama, “A 160 Gb/s interface design configuration for multichip LSI,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2004, pp. 140–141. [7] S. Mick, J. Wilson, and P. Franzon, “4 Gbps high-density AC coupled interconnection,” in Proc. IEEE Custom Integrated Circuits Conf. (CICC), May 2002, pp. 133–140. [8] K. Kanda, D. D. Antono, K. Ishida, H. Kawaguchi, T. Kuroda, and T. Sakurai, “1.27 Gb/s/ch 3 mW/pin wireless superconnect (WSC) interface scheme,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2003, pp. 186–187. [9] R. J. Drost, R. P. Hopkins, and I. E. Sutherland, “Proximity communication,” in Proc. IEEE Custom Integrated Circuits Conf. (CICC), Sep. 2003, pp. 469–472. [10] D. Mizoguchi, Y. B. Yusof, N. Miura, T. Sakurai, and T. Kuroda, “A 1.2 Gb/s/pin wireless superconnect based on inductive inter-chip signaling (IIS),” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2004, pp. 142–143. [11] N. Miura, D. Mizoguchi, Y. B. Yusof, T. Sakurai, and T. Kuroda, “Analysis and design of transceiver circuit and inductor layout for inductive inter-chip wireless superconnect,” in Symp. VLSI Circuits Dig. Tech. Papers, Jun. 2004, pp. 246–249. [12] D. Salzman and T. Knight, “Capacitive coupling solves the known good die problem,” in Proc. IEEE MultiChip Module Conf., Mar. 1994, pp. 95–100. [13] C. C. Tang, C. H. Wu, and S. I. Lin, “Miniature 3-D inductors in standard CMOS process,” IEEE J. Solid-State Circuits, vol. 37, no. 4, pp. 471–478, Apr. 2002. [14] T. Ohguro, N. Sato, M. Matsuo, K. Kojima, H. S. Momose, K. Ishimaru, and H. Ishiuchi, “Ultra-thin chip with permalloy film for high performance MS/RF CMOS,” in Symp. VLSI Technology Dig. Tech. Papers, Jun. 2004, pp. 220–221. [15] N. Miura, D. Mizoguchi, T. Sakurai, and T. Kuroda, “Cross talk countermeasures in inductive inter-chip wireless superconnect,” in Proc. IEEE Custom Integrated Circuits Conf. (CICC), Oct. 2004, pp. 99–102. Noriyuki Miura was born in Oita, Japan, on October 29, 1980. He received the B.S. degree in electrical engineering in 2003 from Keio University, Yokohama, Japan, where he is currently working toward the M.S. degree. Since 2002, he has been engaged in research on a 3-D-stacked inductive inter-chip wireless interface for System in a Package. In 2002, he was with the Hitachi Central Research Laboratory studying CAD tools for low-power VLSI circuits. He has made technical presentations and published technical papers at ISSCC, the Symposium on VLSI Circuits, CICC, and ASP-DAC. Daisuke Mizoguchi was born in Oita, Japan, on September 7, 1975. He received the B.E. and M.S. degrees in information science and electrical engineering from Kyushu University, Fukuoka, Japan, in 1998 and 2000. He is currently working toward the Ph.D. degree in electrical engineering at Keio University, Kanagawa, Japan. In 2000, he joined A Priori Microsystems, Inc., Kanagawa, Japan. He has been engaged in development and design of high-performance computer using FPGA boards. In 2001, he joined Keio University, Yokohama, Japan. He has been engaged in research on the inductive inter-chip communication scheme. Since 2003, he has been working on developing 3-D-FFT logic for Car–Parrinello calculation. MIURA et al.: INDUCTIVE COUPLING AND TRANSCEIVER CIRCUIT FOR INDUCTIVE INTER-CHIP WIRELESS SUPERCONNECT Takayasu Sakurai (S’77–M’78–SM’01–F’03) received the Ph.D. degree in electrical engineering from the University of Tokyo, Tokyo, Japan, in 1981. In 1981, he joined Toshiba Corporation, where he designed CMOS DRAM, SRAM, RISC processors, DSPs, and SoC solutions. He has worked extensively on interconnect delay and capacitance modeling known as the Sakurai model and alpha power-law MOS model. From 1988 to 1990, he was a Visiting Researcher at the University of California at Berkeley, where he conducted research in the field of VLSI CAD. Since 1996, he has been a Professor at the University of Tokyo, working on low-power high-speed VLSI, memory design, interconnects, ubiquitous electronics, organic ICs, and large-area electronics. He has published more than 350 technical publications including 70 invited papers and several books and filed more than 100 patents. Dr. Sakurai served as a conference chair for the Symposium on VLSI Circuits and ICICDT, a TPC chair for A-SSCC, a vice chair for ASPDAC and a program committee member for ISSCC, CICC, DAC, ICCAD, FPGA Workshop, ISLPED, TAU, and other international conferences. He is a plenary speaker for the 2003 ISSCC. He is an elected AdCom member for the IEEE Solid-State Circuits Society and an IEEE Circuits and Systems Society Distinguished Lecturer. 837 Tadahiro Kuroda (M’88–SM’00) received the Ph.D. degree in electrical engineering from the University of Tokyo, Tokyo, Japan, in 1999. In 1982, he joined Toshiba Corporation, where he designed CMOS gate arrays and standard cells. From 1988 to 1990, he was a Visiting Scholar with the University of California at Berkeley, conducting research in the field of VLSI CAD. In 1990, he returned to Toshiba, and was engaged in the research and development of BiCMOS ASICs, ECL gate arrays, highspeed CMOS LSIs for telecommunications, and lowpower CMOS LSIs for multimedia and mobile applications. In 2000, he moved to Keio University, Yokohama, Japan, where he has been a Professor since 2002. His research interests include low-power high-speed CMOS design for wireless and wireline communications, human–computer interactions, and ubiquitous electronics. He has published more than 180 technical publications including 40 invited papers and 17 books or book chapters, and has filed more than 100 patents. Dr. Kuroda served as a technical program committee chair for the Symposium on VLSI Circuits, a vice chair for ASP-DAC, held sub-committee chairs for ICCAD, A-SSCC, and SSDM, and was a program committee member for the Symposium on VLSI Circuits, CICC, DAC, ASP-DAC, ISLPED, SSDM, ISQED, and other international conferences. He is a member of the Institute of Electronics, Information and Communication Engineers of Japan.