TSM103/A

DUAL OPERATIONAL AMPLIFIER AND

VOLTAGE REFERENCE

.

.

..

.

.

.

..

.

OPERATIONAL AMPLIFIER

LOW INPUT OFFSET VOLTAGE : 0.5mV

typ.for TSM103A

LOW SUPPLY CURRENT : 350µA/op.

(@ VCC = 5V)

MEDIUM BANDWIDTH (unity gain) : 0.9MHz

LARGE OUTPUT VOLTAGE SWING : 0V to

(VCC - 1.5V)

INPUT COMMON MODE VOLTAGE RANGE

INCLUDES GROUND

WIDE POWER SUPPLY RANGE : 3 to 32V

±1.5 to æ16V

VOLTAGE REFERENCE

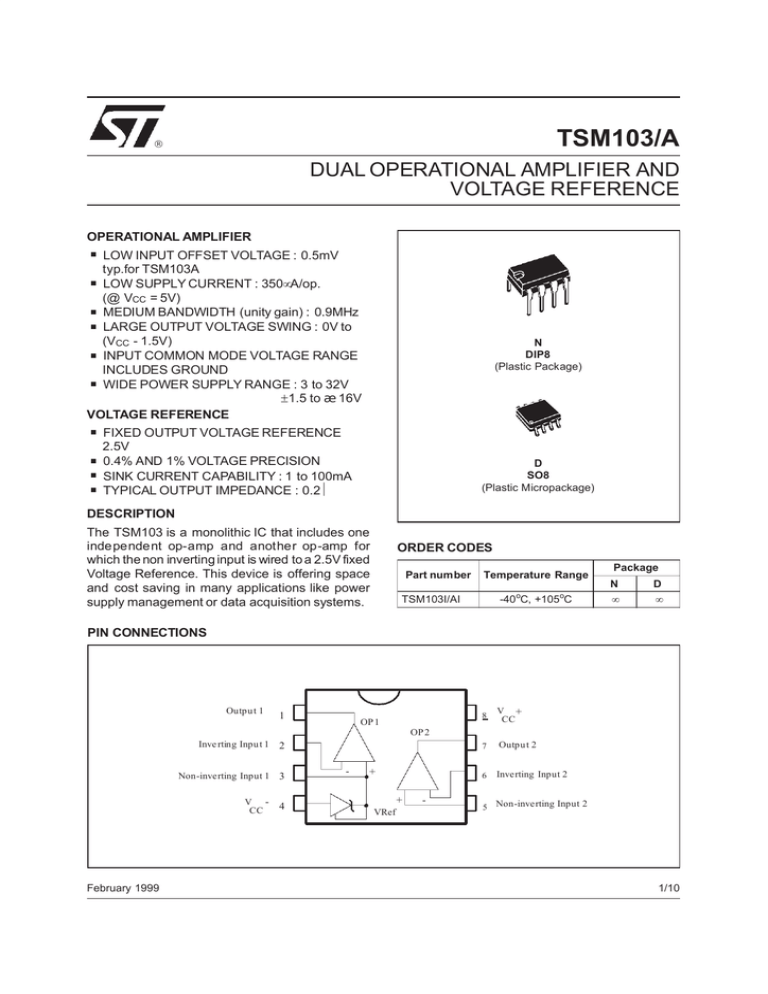

N

DIP8

(Plastic Package)

FIXED OUTPUT VOLTAGE REFERENCE

2.5V

0.4% AND 1% VOLTAGE PRECISION

SINK CURRENT CAPABILITY : 1 to 100mA

TYPICAL OUTPUT IMPEDANCE : 0.2Ω

D

SO8

(Plastic Micropackage)

DESCRIPTION

The TSM103 is a monolithic IC that includes one

independent op-amp and another op-amp for

which the non inverting input is wired to a 2.5V fixed

Voltage Reference. This device is offering space

and cost saving in many applications like power

supply management or data acquisition systems.

ORDER CODES

Part number

Temperature Range

-40oC, +105oC

TSM103I/AI

Package

N

D

•

•

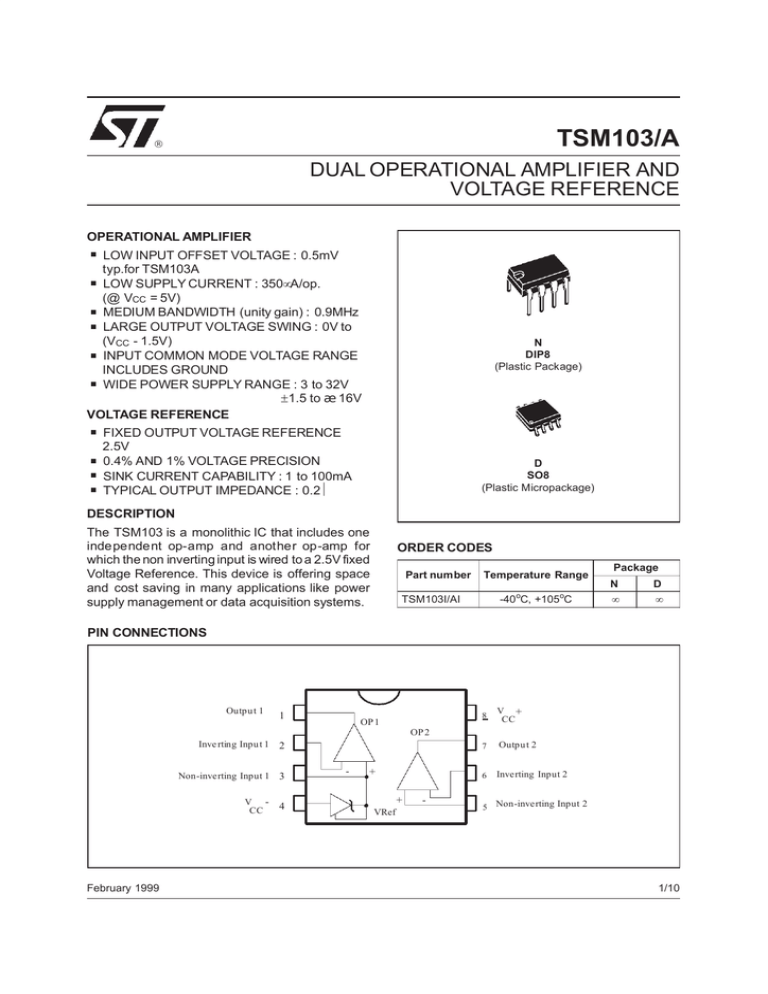

PIN CONNECTIONS

Outpu t 1

1

OP1

8

V +

CC

7

Outpu t 2

6

Inverting Input 2

OP2

Inve rting Inpu t 1 2

Non-inverting Input 1 3

V CC

February 1999

4

-

+

+

VRef

-

5 Non-inverting Input 2

1/10

TSM103/A

ABSOLUTE MAXIMUM RATINGS

Symbol

VCC

Vid

Vi

Toper

Tj

R thja

Parameter

Supply Voltage

Differential Input Voltage

Input Voltage

Operating Free-air Temperature Range

Maximum Junction Temperature

Thermal Resistance Juction to Ambient (SO package)

Value

36

36

-0.3 to +36

-55 to +125

150

175

Unit

V

V

V

o

C

o

C

o

C/W

ELECTRICAL CHARACTERISTICS

Symbol

ICC

2/10

Parameter

Total Supply Current, excluding Current in the

Voltage Reference

+

VCC = 5V, no load

Tmin. < Tamb < Tmax.

+

VCC = 30V, no load

Tmin. < Tamb < Tmax

Min

Typ

Max

0.7

1.2

2

Unit

mA

TSM103/A

OPERATOR 2 (independent op-amp)

VCC+ = +5V, VCC = Ground, Vo = 1.4V,Tamb = 25oC (unless otherwise specified)

Symbol

Vio

DVio

Iio

Iib

Avd

SVR

Vicm

CMR

Isource

IO

Isink

VOH

VOL

SR

GBP

THD

Note 1 :

Parameter

Input Offset Voltage

o

TSM103, Tamb = 25 C

Tmin. ≤ Tamb ≤ Tmax.

TSM103A, Tamb = 25oC

Tmin. ≤ Tamb ≤ Tmax.

Input Offset Voltage Drift

Input Offset Current

Tmin. ≤ Tamb ≤ Tmax.

Input Bias Current

Tmin. ≤ Tamb ≤ Tmax.

Large Signal Voltage Gain

VCC = 15V, R L= 2k, Vo = 1.4V to 11.4V

Tmin. ≤ Tamb ≤ Tmax.

Supply Voltage Rejection Ratio

VCC+ = 5V to 30V

Input Common Mode Voltage Range

VCC = +30V - see note 1

Tmin. ≤ Tamb ≤ Tmax.

Common Mode Rejection Ratio

Tmin. ≤ Tamb ≤ Tmax.

Output Current Source

VCC = +15V, Vo = 2V, Vid = +1V

Short Circuit to Ground

VCC = +15V

Output Current Sink

Vid = -1V,

VCC = +15V, Vo = 2V

High Level Output Voltage

VCC+ = 30V

Tamb = 25oC, RL = 10k

Tmin. ≤ Tamb ≤ Tmax.

Low Level Output Voltage

R L = 10k

Tmin. ≤ Tamb ≤ Tmax.

Slew Rate at Unity Gain

Vi = 0.5 to 3V, VCC = 15V

R L = 2k, CL = 100pF, unity gain

Gain Bandwidth Product

VCC = 30V, R L = 2k, CL = 100pF

f = 100kHz, Vin = 10mV

Total Harmonic Distortion

f = 1kHz

AV = 20dB, RL = 2k, VCC = 30V

C L = 100pF, VO = 2Vpp

Min.

Typ.

Max.

1

4

5

2

3

0.5

7

2

20

50

25

100

65

100

Unit

mV

o

30

50

150

200

µV/ C

nA

nA

V/mV

dB

0

0

70

60

+

V

(VCC ) -1.5

(VCC+) -2

85

dB

mA

20

40

mA

40

10

20

27

27

28

60

mA

V

mV

5

20

20

V/µs

0.2

0.4

0.5

0.9

MHz

%

0.02

The input common-mode voltage of either input signal voltage should not be allowed to go negative by more than 0.3V. The upper

end of the common-mode voltage range is VCC+ -1.5V

But either of both inputs can go to +36V without damage.

3/10

TSM103/A

OPERATOR 1 (op-amp with non-inverting input connected to the internal Vref)

VCC+ = +5V, VCC- = Ground, Tamb = 25oC (unless otherwise specified)

Symbol

Vio

DVio

Iib

Avd

SVR

Isource

IO

Isink

VOH

VOL

SR

GBP

THD

4/10

Parameter

Input Offset Voltage

Vicm = 0V

o

TSM103, Tamb = 25 C

Tmin. ≤ Tamb ≤ Tmax.

o

TSM103A, Tamb = 25 C

Tmin. ≤ Tamb ≤ Tmax.

Input Offset Voltage Drift

Input Bias Current

negative input

Large Signal Voltage Gain

Vicm = 0V

VCC = 15V, R L = 2k

Supply Voltage Rejection Ratio

Vicm = 0V

+

VCC = 5V to 30V

Output Current Source

Vo = 2V

VCC = +15V, Vid = +1V

Short Circuit to Ground

VCC = +15V

Output Current Sink

Vid = -1V,

VCC = +15V, Vo = 2V

High Level Output Voltage

+

VCC = 30V

Tamb = 25oC, RL = 10k

Tmin. ≤ Tamb ≤ Tmax.

Low Level Output Voltage

R L = 10k

Tmin. ≤ Tamb ≤ Tmax.

Slew Rate at Unity Gain

Vi = 0.5 to 2V, VCC = 15V

R L = 2k, CL = 100pF, unity gain

Gain Bandwidth Product

VCC = 30V, R L = 2k, CL = 100pF

f = 100kHz, Vin = 10mV

Total Harmonic Distortion

f = 1kHz

AV = 20dB, RL = 2k, VCC = 30V

C L = 100pF, VO = 2Vpp

Min.

Typ.

Max.

1

4

5

2

3

0.5

Unit

mV

o

µV/ C

nA

7

20

V/mV

100

dB

65

100

mA

20

40

mA

40

10

20

27

27

28

60

mA

V

mV

5

20

20

V/µs

0.2

0.4

0.5

0.9

MHz

%

0.02

TSM103/A

VOLTAGE REFERENCE

Symbol

IK

Parameter

Cathode Current

Symbol

Vref

∆Vref

Imin

|ZKA|

Parameter

Reference Input Voltage

o

TSM103, Tamb = 25 C

Tmin. ≤ Tamb ≤ Tmax.

TSM103A, Tamb = 25oC

Tmin. ≤ Tamb ≤ Tmax.

Reference Input Voltage Deviation Over

Temperature Range

VKA = Vref, IK = 10mA

Tmin. ≤ Tamb ≤ Tmax.

Minimum Cathode Current for Regulation

VKA = Vref

Dynamic Impedance - (note 1)

VKA = Vref, ∆IK = 1 to 100mA, f < 1kHz

Value

1 to 100

Unit

mA

Min.

Typ.

Max.

2.475

2.45

2.49

2.48

2.5

2.525

2.55

2.51

2.52

Unit

V

2.5

mV

7

30

0.5

1

0.2

0.5

mA

Ω

Note 1 : the dynamic impedance is defined as |ZKA| = ∆VKA/∆IK

5/10

TSM103/A

OPERATIONAL AMPLIFIERS

Unit Frequency = F(I)

Vcc=+/-15V, RL=2k, CL=100pF

1000

Unit Freq

Thousands

800

600

400

200

0

-0,015

-0,01

-0,005

0

source <=

I (A)

0,005

0,01

0,015

0,01

0,015

=> sink

GBP = F(I)

Vcc=+/-15V, RL=2k, CL=100pF

800

GBP

Thousands

600

400

200

0

-0,015

-0,01

-0,005

0

source <=

I (A)

0,005

=> sink

Phase and Gain Margin = F(I)

Vcc=+/-15V, RL=2k, CL=100pF

60

2

Phase Margin (deg)

-2

40

-4

30

-6

-8

20

-10

10

0

-0,015

6/10

-12

-0,01

-0,005

source <=

0

I (A)

0,005

=> sink

0,01

-14

0,015

Gain Margin (dB)

0

50

TSM103/A

Total Harmonic Distorsion THD = F(freq)

0,014

THD(%)

0,012

0,01

0,008

0,006

0,004

10

100

1000

10000

100000

Frequency (Hz)

Noise = F(frequency)

Noise(nV/SQR(Hz))

80

60

40

20

0

0,01

0,1

1

10

100

Frequency (Hz)

Vio Distribution - Operator 1

Vcc+=5V, Vcc-=0V

Distribution (%)

80

60

40

20

0

-3

-2,5

-2

-1,5

-1

-0,5

0

0,5

1

1,5

2

2,5

3

2,5

3

Vio (mV)

Vio Distribution - Operator 2

Vcc+=5V, Vcc-=0V

Distribution (%)

80

60

40

20

0

-3

-2,5

-2

-1,5

-1

-0,5

0

0,5

1

1,5

2

Vio (mV)

7/10

TSM103/A

VOLTAGE REFERENCE

Vref = F(Ik)

3

Vref (V)

2,5

2

1,5

1

0,5

0,0001

0,001

0,01

0,1

Cathode Current Ik (Amps)

Vref Stability = f(I,C)

0,06

Current (Amps)

Stable

0,04

Unstable

0,02

0

1,000000E-10

1,000000E-09

1,000000E-08

1,000000E-07

Capacitor(F)

8/10

1,000000E-06

0,00001

TSM103/A

PACKAGE MECHANICAL DATA

8 PINS - PLASTIC PACKAGE

Dim.

Millimeters

Min.

A

Typ.

Min.

3.32

a1

0.51

B

1.15

b

b1

Typ.

0.131

1.65

0.045

0.065

0.356

0.55

0.014

0.022

0.204

0.304

0.008

0.012

10.92

7.95

9.75

0.430

0.313

0.384

e

2.54

0.100

e3

7.62

0.300

e4

7.62

F

Z

0.300

6.6

i

L

Max.

0.020

D

E

Inches

Max.

0260

5.08

3.18

3.81

1.52

0.200

0.125

0.150

0.060

9/10

TSM103/A

PACKAGE MECHANICAL DATA

8 PINS - PLASTIC MICROPACKAGE (SO)

Dim.

A

a1

a2

a3

b

b1

C

c1

D

E

e

e3

F

L

M

S

Min.

Millimeters

Typ.

0.1

0.65

0.35

0.19

0.25

Max.

1.75

0.25

1.65

0.85

0.48

0.25

0.5

Min.

Inches

Typ.

0.026

0.014

0.007

0.010

Max.

0.069

0.010

0.065

0.033

0.019

0.010

0.020

0.189

0.228

0.197

0.244

0.004

o

45 (typ.)

4.8

5.8

5.0

6.2

1.27

3.81

3.8

0.4

0.050

0.150

4.0

1.27

0.6

0.150

0.016

0.157

0.050

0.024

8o (max.)

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the

consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from

its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications

mentioned in this pub lication are subject to change without notice. This publication supersedes and replaces all information

previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems

without express written approval of STMicroelectronics.

The ST logo is a trademark of STMicroelectronics

1999 STMicroelectronics – Printed in Italy – All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco

The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

http://www.st.com

10/10