AN2081

APPLICATION NOTE

How to Migrate from the

M95 SPI EEPROM to the M25PE SPI Serial Flash

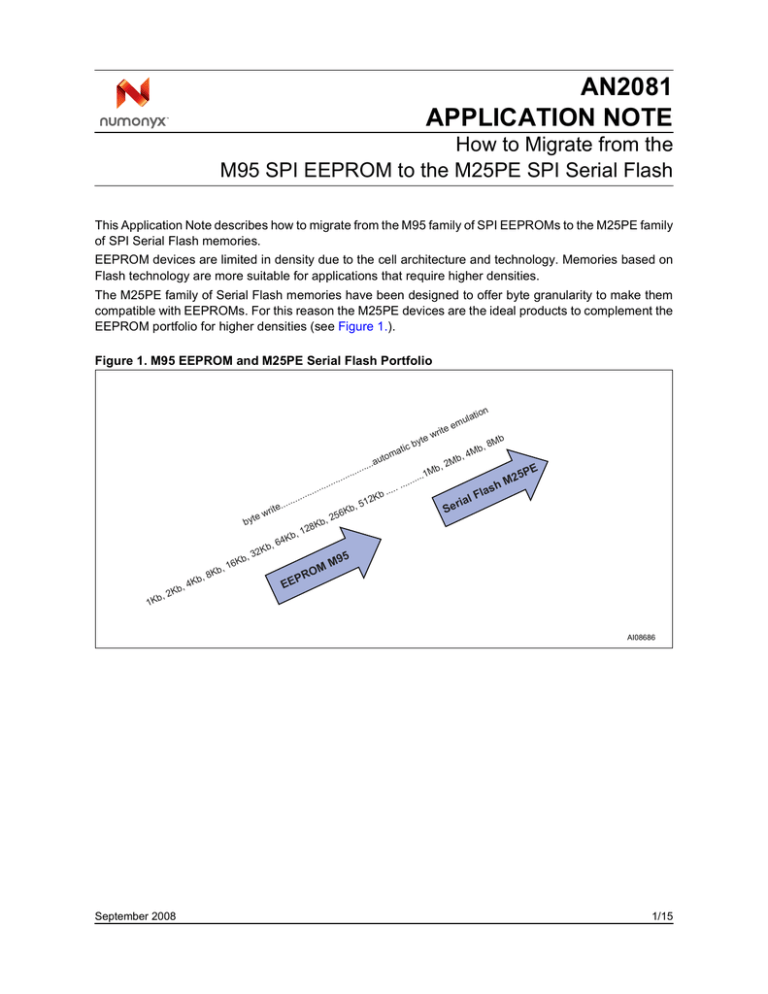

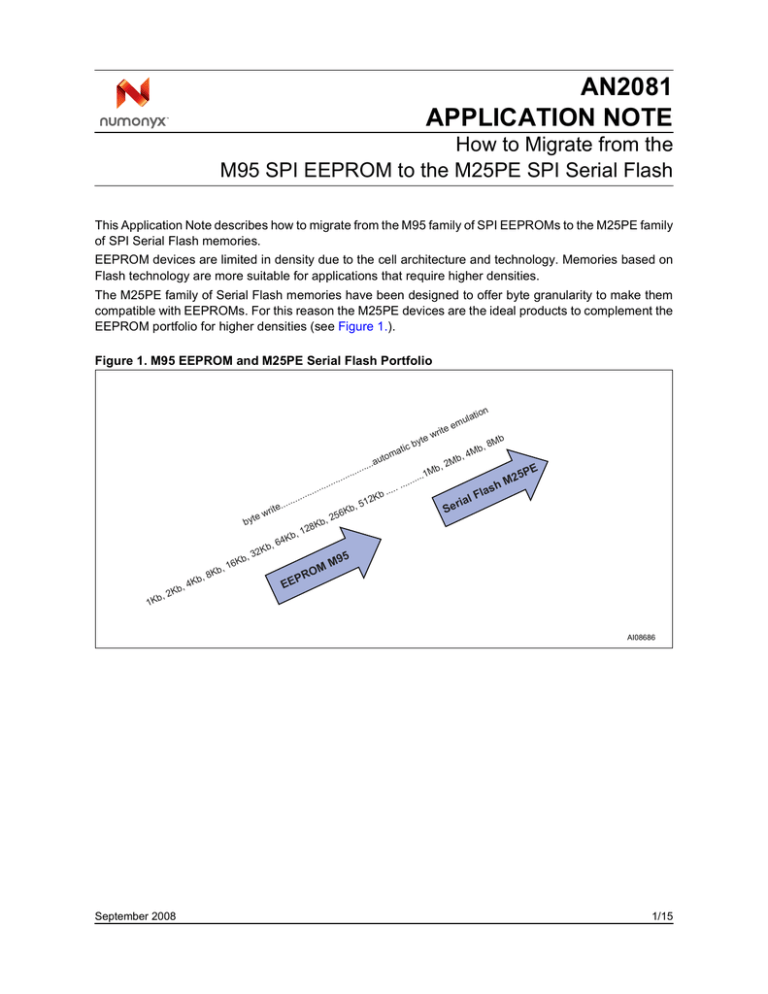

This Application Note describes how to migrate from the M95 family of SPI EEPROMs to the M25PE family

of SPI Serial Flash memories.

EEPROM devices are limited in density due to the cell architecture and technology. Memories based on

Flash technology are more suitable for applications that require higher densities.

The M25PE family of Serial Flash memories have been designed to offer byte granularity to make them

compatible with EEPROMs. For this reason the M25PE devices are the ideal products to complement the

EEPROM portfolio for higher densities (see Figure 1.).

Figure 1. M95 EEPROM and M25PE Serial Flash Portfolio

tion

ula

yte

b

atic

....

....

.....

....

.....

...

rite

56K

ew

byt

b, 2

b,

4K

b, 6

b

, 4K

Kb

,2

Kb

, 2M

E

25P

...

.....

l

al F

ri

Se

M

ash

K

128

K

, 32

5

Kb

, 16

b

, 8K

b

Mb

b, 8

Mb

..1

.....

2K

1

b, 5

wri

M

b, 4

om

aut

.....

....

.....

m

te e

M

RO

M9

P

EE

1

AI08686

September 2008

1/15

AN2081 - APPLICATION NOTE

TABLE OF CONTENTS

Figure 1. M95 EEPROM and M25PE Serial Flash Portfolio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

PINOUT COMPATABILITY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Figure 2. Pin Connections for 8 Pin Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

M95 (EEPROM) Hold Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

M25PE (Serial Flash) Reset Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

BOARD LAYOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 3. Cross sections of the MLP and SO8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 4. Board Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

ARCHITECTURE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 5. Comparison of Block Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

SPI PROTOCOL COMPATIBILITY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

PROGRAM AND ERASE GRANULARITY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 6. Example of Write Instruction for two Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 7. Automatic Steps in M95 Write Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Serial Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 8. Automatic Steps in M25PE Page Write Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

INSTRUCTION SET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 1. Instruction Comparison M95 vs. M25PE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 2. Additional Instructions in M25PE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

M95 EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 3. M95 Status Register Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 4. M95 Write-Protected Block Size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 9. M95 Protect State Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

M25PE Serial Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

CONCLUSION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

REFERENCES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

REVISION HISTORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 5. Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2/15

AN2081 - APPLICATION NOTE

PINOUT COMPATABILITY

Figure 2. gives the pinout for all the 8 pin packages in the M25PE and M95 families. The only difference

is pin 7, which is a RESET signal in M25PE devices, whereas it is a HOLD signal in M95 devices.

Figure 2. Pin Connections for 8 Pin Packages

S

Q

W

VSS

1

2

3

4

8

7

6

5

VCC

RESET (M25PE) HOLD (M95)

C

D

AI08681

M95 (EEPROM) Hold Input

The Hold (HOLD) input is used to pause any serial communications with the device without deselecting

the device. This signal is useful if, for example, the clock is free running (not controlled by the master) and

the master needs time to service an interrupt routine occuring during an M95 read sequence.

During the Hold condition, the Serial Data Output (Q) is high impedance, and Serial Data Input (D) and

Serial Clock (C) are Don’t Care. The memory will enter the Hold condition when: Hold (HOLD), Chip Select

(S) and Clock (C) are driven Low.

M25PE (Serial Flash) Reset Input

The M25PE Reset (Reset) input provides a hardware reset for the memory. In this mode, the outputs are

high impedance. It is useful during critical operations such as power up and power down and when there

is a problem with noise.

When Reset (Reset) is driven High, the memory is in the normal operating mode. When Reset (Reset) is

driven Low, the memory will enter the Reset mode. Driving Reset (Reset) Low while an internal operation

is in progress can effect the on-going operation (a write cycle, program cycle, or erase cycle).

If neither the Hold nor the Reset inputs are required in the application, then, as both signals are active low,

the pin should be connected High so that these features do not affect the application.

If the features are used, then the application must take into account the difference in their behavior.

3/15

AN2081 - APPLICATION NOTE

BOARD LAYOUT

The board layout can be adapted to receive the different packages.

■

SO8N compatible with the MLP (5x6mm) footprint

■

SO8W compatible with the MLP (8x6mm) footprint

The tracks of the footprints of the SO8N or MLP (5x6mm) can be stretched to accommodate the footprints

of the SO8W or the MLP (8x6mm).

Note: Care must be taken to avoid any short-circuit between the tracks of the SO8N or the MLP (5x6mm)

footprint and the central conductive pad on the underside of the MLP (8x6mm) package (see Figure 3.).

Figure 3. Cross sections of the MLP and SO8

0.07”

SO8

0.25”

0.04”

MLP

ai07605

Both these footprints can then be inserted inside the SO16W footprint (see Figure 4.).

VCC

RESET / HOLD

C

D

Figure 4. Board Layout

RESET

VCC

DU

DU

DU

DU

S

Q

VSS

S

Q

W

SO16W footprint

C

D

DU

DU

DU

DU

VSS

W

SO8N, SO8W footprint

(longer pads to accommodate both)

AI08682

4/15

AN2081 - APPLICATION NOTE

ARCHITECTURE

Figure 5. shows the Block Diagrams for both the M95 and M25PE devices. The diagrams highlight the

principle differences in the device architecture:

■

Byte Write for M95 devices directly through the SRAM buffer, Byte Write for M25PE using the SRAM

buffer to copy the content of the rest of the page (see PROGRAM AND ERASE GRANULARITY

section for more details)

■

Hardware and Software protection for the M95 devices, Hardware protection on last 256 pages for

M25PE devices (see PROTECTION section for more details).

Figure 5. Comparison of Block Diagrams

M95 EEPROM

M25 Serial Flash

M95

M25PE

SRAM Buffer

SRAM Buffer

D

C

D

C

Q

SPI

Peripheral

Q

Byte Write

S

HOLD

Control

Logic

Software Protection

Byte Write

S

RESET

Last Sector

SPI

Peripheral

Control

Logic

Hardware Protection

W

W

SRWD

Hardware Protection

(first 256 pages protected)

BP1 BP0 WELWIP

WELWIP

Status Register

Status Register

Ai08687

5/15

AN2081 - APPLICATION NOTE

SPI PROTOCOL COMPATIBILITY

Both the EEPROM and Serial Flash families are accessed by the Serial Peripheral Interface (SPI) bus.

The SPI protocol is commonly used by applications and gives a high speed access to the memory content

using only 4 pins:

Chip Select (S): this input is used to select or deselect the memory, it allows many SPI devices to be

connected in the one application

Serial Clock (C): this input signal provides the timing of the serial interface

Serial Data Input (D): this input is used to serially transfer data into the device.

Serial Data Output (Q): this output is used to serially transfer data out of the device.

The SPI protocol used for the EEPROM and the Serial Flash are compatible but care must be taken on

the timing as the Serial Flash operates at a higher frequency (see datasheets for details).

6/15

AN2081 - APPLICATION NOTE

PROGRAM AND ERASE GRANULARITY

EEPROM

M 95 EEPROMs have:

■

an Erase granularity of one byte, where the byte content is erased to FFh or 00h according to the

design choice

■

a Program granularity of one byte, where each bit of the byte can be independently programmed to

the opposite of the erase level.

In EEPROMs, program and erase operations are combined in the Write instruction. Therefore the application does not need to erase the byte before the program operation, as the byte erase operation is included in the instruction, which means that it is not necessary to know the content of the byte before the

update.

For example, if the application needs to update two bytes located at address N+2, it has to send the Write

instruction, followed by address N+2, followed by the two bytes of data (see Figure 6.).

To be able to do this, the EEPROM performs three different automatic internal operations (see Figure 7.):

Step 1: data are input sequentially and stored in the corresponding address of the buffer.

Step 2: the two bytes at address N+2 are erased

Step 3: the two bytes are programmed from the buffer into the memory array

All these operations are transparent for the application, as they are done automatically with the Write Instructions.

Figure 6. Example of Write Instruction for two Bytes

Data Line (Q and D)

A2

Instruction

Code

AA

Address N+2

AAh

55h

AI08683

7/15

AN2081 - APPLICATION NOTE

Figure 7. Automatic Steps in M95 Write Instruction

STEP 1, Data Input

Internal Buffer

data input

FFh FFh AAh 55h FFh

FFh

Memory Array

00000h

xxh xxh xxh xxh xxh

xxh

Address N+2 10h 06h 15h 00h 56h

33h

xxh xxh xxh xxh xxh

xxh

FFFFFh

STEP 2, Bytes Erased

Internal Buffer

FFh FFh AAh 55h FFh

FFh

Memory Array

00000h

xxh xxh xxh xxh xxh

xxh

Address N+2 10h 06h FFh FFh 56h

33h

xxh xxh xxh xxh xxh

xxh

FFFFFh

STEP 3, Bytes Programmed into Memory Array

Internal Buffer

FFh FFh AAh 55h FFh

FFh

Memory Array

00000h

xxh xxh xxh xxh xxh

xxh

Address N+2 10h 06h AAh 55h 56h

33h

xxh xxh xxh xxh xxh

xxh

FFFFFh

AI08684

8/15

AN2081 - APPLICATION NOTE

Serial Flash

ST’s Serial Flash memory have:

■

an Erase granularity of 256 Bytes (one Page), where the page content is erased to FFh, which is a

higher granularity compared to standard Flash memories that are erased at the block level.

■

a Program granularity of one Byte, where each bit of the byte can be independently programmed to

0 (equivalent to the EEPROM granularity in the case of a pre-erased Byte)

As the Erase and Program granularity are different, there are two different instructions to program and

erase a Serial Flash:

■

Page Erase instruction (erase only)

■

Byte Program instruction (program only)

These two different instructions are useful to optimize the update time or the memory cycling. If an area

is already erased, then the erase operation can be omitted which will speed up the overall programming

time and reduce memory cycling. The erase instruction can also be used to erase an area when the device

is idle, so that when the area is programmed later, only the program operation is required.

To simplify the byte granularity management, Numonyx Serial Flash feature an automatic byte write emulation equivalent to the EEPROM, where like the EEPROM, a Page Write instruction will erase and program one byte without knowing its previous value and without changing any other data in the page.

To take the same example as shown in Figure 6., if the application needs to update two bytes located at

address N+2, it has to send the Page Write instruction, followed by address N+2, followed by the two bytes

of data.

To be able to do this, the Numonyx Serial Flash uses an internal 256 Bytes SRAM buffer to backup the

rest of the page, which must be kept unchanged.

The Numonyx Serial Flash performs three different automatic operations (see Figure 8.):

Step 1: data are input sequentially and stored in the corresponding address of the buffer

Step 2: all unaddressed bytes of the page are copied from the memory array into the buffer

Step 3: the addressed page is erased

Step 4: the buffer content is programmed into the addressed page

All these operations are transparent for the application, as they are done automatically with the Page Write

Instruction.

9/15

AN2081 - APPLICATION NOTE

Figure 8. Automatic Steps in M25PE Page Write Instruction

STEP 1, Data Input

STEP 2, Page Copied into Buffer

(unaddressed bytes only)

Internal Buffer

data input

FFh FFh AAh 55h FFh

Memory Array

00000h

Internal Buffer

FFh

xxh xxh xxh xxh xxh

xxh

Address N+2 10h 06h 15h 00h 56h

33h

xxh xxh xxh xxh xxh

xxh

FFFFFh

10h 06h AAh 55h 56h

33h

Memory Array

00000h

xxh xxh xxh xxh xxh

Address N+2 10h 06h 15h 00h

xxh

56h

33h

xxh xxh xxh xxh xxh

xxh

FFFFFh

STEP 4, Bytes Programmed into Memory Array

STEP 3, Page Erased

Internal Buffer

Internal Buffer

10h 06h AAh 55h 56h

Memory Array

00000h

FFh FFh AAh 55h FFh

33h

FFh

Memory Array

00000h

xxh

xxh xxh xxh xxh xxh

xxh

Address N+2 FFh FFh FFh FFh FFh

FFh

Address N+2 10h 06h AAh 55h 56h

33h

xxh xxh xxh xxh xxh

xxh

xxh xxh xxh xxh xxh

xxh

xxh xxh xxh xxh xxh

FFFFFh

FFFFFh

AI08685

10/15

AN2081 - APPLICATION NOTE

INSTRUCTION SET

Table 1. shows a comparison of the instructions of the M95 and the M25PE families.

The first time a Serial Flash device is programmed the Page Program instruction (02h) is equivalent to the

EEPROM Write instruction (02h). This is because the Serial Flash is delivered with the content erased, so

the memory can be programmed byte by byte as for the EEPROM.

For subsequent program operations, where the initial byte content is not FFh, the application must use the

Serial Flash Page Write instruction (0Ah) to perform an operation equivalent to the EEPROM Write instruction (02h).

The M25PE family has additional instructions (see Table 2. ) that are not available in the M95 family.

One of these is the Read Identification instruction which can be used to differentiate the Serial Flash from

the EEPROM, allowing the application to select the appropriate instruction code. As the Read Identification instruction is not available in EEPROMs, the EEPROM will remain in High Impedance if this instruction

is sent on the SPI bus.

If the Output line (Q), is connected to VCC through a pull-up resistor or to ground (VSS) through a pull-down

resistor, the application will read FFh or 00h as the EEPROM signature.

Table 1. Instruction Comparison M95 vs. M25PE

Instruction Code

Instruction

Description

M95xx

M25PExx

WREN

Write Enable

06h

06h

WRDI

Write Disable

04h

04h

RDSR

Read Status Register

05h

05h

WRSR

Write Status Register

01h

01h

READ

M95 - Read from Memory Array,

M25PE - Read Data Bytes

03h

03h

M95 - Write to Memory Array

M25PE - Page Program

02h

02h

-

0Ah

WRITE, PP, PW

M25PE - Page Write

Table 2. Additional Instructions in M25PE

Instruction

Description

Instruction Code

Read Identification - provides the manufacturer, memory

and density ID

9Fh

Read Data Bytes at Higher Speed

0Bh

PE

Page Erase (256 Bytes at once)

DBh

SE

Sector Erase (64KBytes at once)

D8h

BE

Bulk Erase (the whole memory array)

C7h

DP

Deep Power-down - protects the memory contents and

reduces the power consumption

B9h

Release from Deep Power-down - exits from deep powerdown mode

ABh

RDID

FAST_READ

RDP

11/15

AN2081 - APPLICATION NOTE

PROTECTION

M95 EEPROM

The M95 family has various protection mechanisms:

■

To prevent data corruption, an internal VCC comparator inhibits all the M95 functions if the VCC voltage

is lower than the POR threshold.

■

The non-volatile Block Protect bits, located in the Status Register, allow parts of the memory to be

configured as read-only (see Table 3. and Table 4.).

■

The Hardware Protection mode can be used to prevent write operations in the Status Register,

thereby protecting bits SRWD, BP2, BP1 and BP0 from being modified (see Figure 5.). The mode is

entered by:

–

setting the Status Register Write protect bit (SRWD) to 1

–

applying a Low-level voltage to the Write Protect pin (W).

Once the Hardware protection mode is entered (State C in Figure 5.), the only way to exit is to apply VCC

on the Write Protect pin W. If the W pin is hardware connected to the ground (VSS), then it is impossible

to change the protection.

Table 3. M95 Status Register Format

b7

SRWD

b0

0

0

0

BP1

BP0

WEL

WIP

Status Register Write Protect

Block Protect Bits

Write Enable Latch Bit

Write In Progress Bit

Table 4. M95 Write-Protected Block Size

Status Register Bits

Protected Block

12/15

BP1

BP0

0

0

none

0

1

Upper quarter

1

0

Upper half

1

1

Whole memory

AN2081 - APPLICATION NOTE

Figure 9. M95 Protect State Diagram

W=1

SRWD=0

W=1

SRWD=1

Software WRSR

Hardware W=VSS

State-D

Software WRSR

Hardware W=VCC

Hardware W=VSS

Hardware W=VCC

State-A

Software WRSR

State-B

State-C

W=0

SRWD=0

W=0

SRWD=1

Hardware Protection:

All write accesses to the

Status Register are rejected

AI08689

M25PE Serial Flash

The M25PE family has various protection mechanisms:

■

To prevent data corruption, an internal VCC comparator inhibits all M25PE functions if the VCC voltage

is lower than the POR threshold.

■

Write operations are prevented for a further 15ms (max) after VCC goes above the POR value.

■

The Write protect pin (W) can be used to put the device in Hardware Protected mode, which protects

the upper 256 pages (64KBytes) against write operations.

13/15

AN2081 - APPLICATION NOTE

CONCLUSION

The M25PE is a family of Serial Flash memories with a Serial Peripheral Interface. The M25PE devices

have been designed to compliment ST’s Serial EEPROM family at higher densities, and so may be used

to replace an M95 in an application. The M25PE Serial Flash are fully hardware-compatible with the M95

EEPROMs and are also software-compatible, as long as the minor points highlighted in this application

notes are taken into account.

REFERENCES

The following datasheets are available ( on www.numonyx.com or from your Numonyx distributor):

■

■

SPI EEPROM

–

M95040, M95020, M95010

–

M95256, M95128

–

M95160, M95080

–

M95640, M95320

–

M95512

SPI Serial Flash

–

M25PE10

–

M25PE20

–

M25PE40

–

M25PE80

REVISION HISTORY

Table 5. Document Revision History

Date

Version

Revision Details

09-Dec-2004

1.0

First Issue

03-Sept-2008

2.0

Applied Numonyx branding.

14/15

AN2081 - APPLICATION NOTE

Please Read Carefully:

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH NUMONYX™ PRODUCTS. NO

LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY

RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN NUMONYX'S TERMS AND

CONDITIONS OF SALE FOR SUCH PRODUCTS, NUMONYX ASSUMES NO LIABILITY WHATSOEVER, AND

NUMONYX DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF

NUMONYX PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A

PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR

OTHER INTELLECTUAL PROPERTY RIGHT.

Numonyx products are not intended for use in medical, life saving, life sustaining, critical control or safety

systems, or in nuclear facility applications.

Numonyx may make changes to specifications and product descriptions at any time, without notice.

Numonyx, B.V. may have patents or pending patent applications, trademarks, copyrights, or other intellectual

property rights that relate to the presented subject matter. The furnishing of documents and other materials and

information does not provide any license, express or implied, by estoppel or otherwise, to any such patents,

trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or

“undefined.” Numonyx reserves these for future definition and shall have no responsibility whatsoever for conflicts

or incompatibilities arising from future changes to them.

Contact your local Numonyx sales office or your distributor to obtain the latest specifications and before placing

your product order.

Copies of documents which have an order number and are referenced in this document, or other Numonyx

literature may be obtained by visiting Numonyx's website at http://www.numonyx.com.

Numonyx StrataFlash is a trademark or registered trademark of Numonyx or its subsidiaries in the United States

and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2008, Numonyx, B.V., All Rights Reserved.

15/15