DC-link voltage balancing method for a hybrid asymmetric multilevel

DC-link voltage balancing method for a hybrid asymmetric multilevel converter

Marcin Zygmanowski, Jaros

ł

aw Michalak, Bogus

ł

aw Grzesik

SILESIAN UNIVERSITY OF TECHNOLOGY

Faculty of Electrical Engineering, Dept. of Power Electronics, Electrical Drives and Robotics ul. B. Krzywoustego 2

Gliwice, Poland

Tel.: +48 / (32) 237 12 47

Fax: +48 / (32) 237 13 04

E-Mail: marcin.zygmanowski@polsl.pl, URL: http://kener.elektr.polsl.pl

Acknowledgements

The work was funded by Polish National Science Center under the project N N510 214638.

Keywords

«Multilevel converters», «Voltage Source Inverters (VSI)», «Pulse Width Modulation (PWM)»,

«Converter control».

Abstract

The paper presents the dc-link voltage balancing method for a five-level hybrid asymmetric multilevel converter based on a neutral point clamped (NPC) converter with H-bridge (HB) converters. The considered converter, which is referred to as NPC-HB, is treated in this paper as a modification of the classic three-level NPC converter. It improves the harmonic performance of output voltage compared to the NPC converter. This improvement is made by increasing the number of levels in the converter output voltage. Nevertheless, due to the use of floating H-bridge converters inside the NPC-HB topology, the dc voltage balancing method is implemented. Basing on the converter ac side current and HB converter dc link voltage, the proposed method modifies the PWM modulation scheme in both

NPC and HB converters. This modification is applied to each switching period while the converter output voltage reference is kept unchanged. Such modulation scheme is characterized as robust and guaranteeing the low harmonic content in the output voltage. Other dc voltage balancing methods of the hybrid NPC-HB converter are compared in this paper. The proposed method is experimentally verified.

Introduction

Harmonic performance in a multilevel converter output voltage is typically improved by increasing the number of voltage levels [1], [2]. However, the quality of output voltage increases at the cost of a larger number of transistors and greater complexity of the converter. Therefore, multilevel converters with a limited number of voltage levels still dominate in most of the applications. The number of voltage levels generally results from the converter operational voltage and blocking capabilities of the devices. Much better improvement in the increasing of the number of voltage levels can be achieved by using hybrid asymmetric converters [3], [4], which consist of different technology devices or are composed of parts that are representing different basic multilevel converter topologies.

Together with increasing the number of voltage levels in output voltage, hybrid multilevel converters allow decreasing power losses inside the converter and equalizing power loss distribution among the switching devices. This important features cause that hybrid multilevel converters have been the subject of intensive worldwide research [5]-[8].

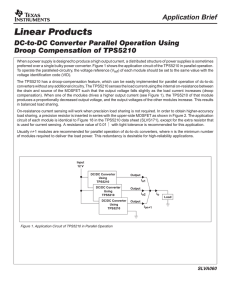

The converter considered in this paper consists of the three-phase NPC converter and three H-bridge converters connected in series to NPC converter as shown in Fig. 1. This topology is referred to as

V dcNPC

S

1A

S

1B

S

1C

S

7A

V dcHB S

5A i

A

A v

HBA

S

2A v

NPCA

S

2B

S

2C

S

8A

S

6A

0 v

NPCB

S

7B

V dcHB S

5B B v

NPCC v

HBB

S

3B

S

8B

S

6B

V dcNPC

S

3A

S

3C

S

7C

V dcHB S

5C C v

HBC

S

4A

S

4B

S

4C

S

8C

S

6C

Fig. 1: Hybrid asymmetric NPC-HB converter.

NPC-HB converter. One of the most important features of the NPC-HB converter is that only one dclink circuit in the NPC converter has to be supplied from the grid having dc-link capacitors in Hbrigde converters floating. Various algorithms exist to balance dc-link voltages in H-bridge converters.

In this paper, a relatively simple balancing method has been presented, which is based on the modification of modulating signals of NPC and H-bridge converters. A mathematical description of the method is given and verified experimentally. This method is compared to methods from [9], [10].

Operation of hybrid asymmetric NPC-HB converter

The NPC-HB converter belongs to a wide family of asymmetric converters which have different voltages in dc-link circuits. Depending on the dc-link voltage ratio half of the dc-link voltage of the NPC converter V dcNPC

V dcHB k dc

(1), which is the ratio between a

and dc-link voltages of H-bridge converters

, the NPC-HB converter can be maximally a five-, seven- or nine-level converter. k dc

V dcNPC

V dcHB

(1)

According to [5], when levels ( n max

= 5), for k k dc

= 1, the converter produces output voltage with a maximum of five voltage dc

= 2 this number increases to n

= 9. In this paper, the case when k dc max

= 7 (as shown in Fig. 2) and for k dc

= 3, n max

= 2 is considered. Such a converter generates output voltage in 12 different switching states (Fig. 2.b) where switching states 2, 5 and 8 can be divided into two states 2a,

2b, 5a, 5b, 8a and 8b. These states do not differ form each other in respect to the converter operation. a)

1 2 3 4 5 6 7 8 9 b)

1 v

A0

= 3 V dcHB v

HB

V dcHB v

A0

= 2 V dcHB

2a 2b

3 4 v

A0

= V dcHB v

NPC

V dcNPC

= 2 V dcHB v

A0

= 0

5a 5b

6 7 v

A0

= V dcHB v

A0

= -2 V dcHB

8a 8b

V dcNPC

+ V dcHB

= 3 V dcHB v

A0

9 v

A0

= -3 V dcHB

Fig. 2: Single-phase NPC-HB converter output voltage: a) waveforms, b) equivalent circuits.

The NPC-HB converter illustrated in Fig. 3.a, as a single-phase converter allows generating the modulated output voltage which has up to seven levels (Fig. 3.b). As the converter output voltage v

A0 is the sum of a three-level NPC converter output voltage v

NPC output voltage v

HB

, v

A0

= v

NPC

+ v

HB

and a three-level H-bridge converter

, the NPC output voltage can have a limited number of switchings e.g. four switchings per the fundamental period. The difference between the output voltage reference and the NPC converter output voltage v

A0

v

NPC

is generated by the H-bridge converter as a modulated voltage with a high switching frequency. This modulation technique is adapted from asymmetric cascaded converters [2], [3] and assures low switching power losses in the NPC converter. a) b) c)

S

MHB

V dcHB

A 1.0

V

A0,1h v

HB v

A0 v

HB

V dcHB

0.8

V

NPC,1h

0.6

V dcNPC

V dcNPC v

NPC α

1

0.4

0.2

V dcNPC

0 v

NPC

S

M

V dcNPC

+ V dcHB

0

V

HB,1h v

A0

-0.2

0 0.2

0.4

0.6

0.8

1 modulation index, m a

0 5 10 15 20

0 time, t (ms)

Fig. 3: NPC-HB converter output voltage generation for k dc

= 2: a) single-phase converter, b) voltage waveforms, c) output voltage normalized fundamental harmonics distribution among NPC and HB converters as a function of the modulation index m a

.

The method presented in Fig. 3 requires using dc voltage sources instead of capacitors in DC-link circuits of H-bridge converters. This issue can be explained by assuming that the output current is a sinusoidal waveform at the fundamental frequency. In such a case, active powers at the outputs of both converters are proportional to amplitudes of the output voltage fundamental components (Fig. 3.c) of each converter respectively. The negative values of the output voltage fundamental harmonic amplitude mean that this harmonics are shifted by 180 degrees from the sinusoidal reference signal S

M

In Fig. 3.c it can be seen that for different modulation indices m a generated by the H-bridge converter should be positive ( m a

(0.76 > m a

NPC converter is given by

there are regions where active power

< 0.37 or m a

> 0.76) or negative

> 0.37). The maximum normalized fundamental harmonic that can be generated by the

.

V

V

NPC,1hmax dcNPC

V dcHB

3

8 8

9

0.8

,

(2) where arcsin(1/3) = 19.47º is the minimum switching angle α

1

in the NPC converter output voltage for the presented method. The maximum fundamental component of the NPC converter given in (2) determines the maximum NPC-HB converter output voltage fundamental component in the case where

H-bridge converters utilize DC-link capacitors. The maximum normalized fundamental component given in (2) is achieved for sinusoidal modulating signal S

M

, and in the case of third harmonic injection this value increases up to 0.832. This relatively small increase 0.832/0.8 = 104% results from the fact that with third harmonic injection the switching angle α

1

decreases to 11.34º.

This relatively small utilization of the output voltage fundamental harmonic brings an idea of decreasing the maximum number of levels from n max

= 7 to n max

= 5 by using the modulated output voltage of the NPC converter in such a manner that this voltage contains the whole output voltage fundamental component. With the third harmonic injection the maximum normalized harmonic is

V

V

NPC,1hmax dcNPC

V dcHB

2 2

3 3

0.77

.

(3)

This value corresponds to the maximum value of the modulation index m amax

. This means that utilization of only five levels of the output voltage decreases the maximum fundamental component amplitude to 0.77/0.832 = 92.5%. The modulation method which is used for generating the NPC converter output voltage should take into account the possibility of balancing the dc-link capacitor voltages in the H-bridge converter.

1.0

V

A0,1h

0.8

0.6

0.4

0.2

0

V

NPC,1h

V

HB,1h m amax

-0.2

0 0.2

0.4

0.6

0.8

1 modulation index, m a

Fig. 4: Output voltage fundamental components of the NPC-HB converter with k dc

= 2 and a limited number of voltage levels n = 5 in case when the whole fundamental component is generated by the

NPC converter.

The modulation technique generating the NPC converter output voltage, with the fundamental component proportional to the reference fundamental signal, is presented in the next paragraph.

Balancing method of dc-link capacitor voltages of H-bridge converters

Switching patterns

Many different modulation techniques can be used to generate the output voltage of the NPC converter whose fundamental component is proportional to the reference signal according to Fig. 4. This necessary condition allows balancing the H-bridge converter dc-link capacitor voltages. Many modulation techniques exist e.g. a selective harmonic elimination method [10], which is promising because it allows controlling the number of switchings in the NPC converter. However, in this method the switching frequency of the H-bridge converters should be relatively high because the NPC converter generates uncontrolled harmonics, which should be rejected by the H-bridge converter. This method also requires large lookup tables of switching angles α depending on the modulation index. In literature other balancing methods are reported [6], [9].

The authors of this paper propose a different approach, which seems to be simpler than other balancing methods. This method is based on redundant switching states which produce the same output voltage but with a different sign of the H-bridge converter output voltage. This allows charging or discharging the dc-link capacitor (Fig. 5), which is the main idea of capacitor voltages balancing.

The H-bridge converter allows charging or discharging its dc-link capacitor only when the NPC-HB converter output voltage is equal to V dcHB

or V dcHB

(states 3 and 4 or 6 and 7 in Fig. 2). In other situations the H-bridge converter generates zero voltage, which does not influence the capacitor voltage. It should be noted that this method can only be used for the NPC-HB converter with a reduced number of voltage levels.

In Fig. 5 four modulation regions are presented in which the output voltage reference signal is between

2 V dcHB

> v

A0ref

≥ V dcHB

, V dcHB

> v

A0ref

≥ 0, 0 > v

A0ref

≥ V dcHB

, V dcHB

> v

A0ref

≥ -2 V dcHB

. In each of these regions two different switching patterns that allow charging or discharging of the H-bridge converter capacitor can be used. Switching patterns are applied to each of switching periods T

S

separately.

Switching patterns v

NPC v

A0ref v

HB

I II III IV V VI VII VIII

7 5 6 5 6

5

6

2 V dcHB

V dcHB

0

V dcHB

-2 V dcHB

Switching states v

A0

2 4 2 3 2 3

2

3

T

S

5

5 3 4 5 4 5

8

8 6 7 8 7

8

2 V dcHB

V dcHB

0

V dcHB

-2 V dcHB z

2 V dcHB

> v

A0ref

1

> V dcHB

0

V dcHB

0

> v

A0ref

> 0

1

0 > v

A0ref

1

> V dcHB

0

V dcHB

> v

A0ref

0

> -2 V dcHB

1

Fig. 5: Switching patterns I-VIII in switching periods T

S dc-link capacitor voltages.

which allow balancing the H-bridge converter

In Fig. 5 only switching states 2-8 (as defined in Fig. 2) are presented. This is because the number of voltage levels is limited to n = 5, and switching states 1 and 9 are no longer used in this method.

Switching patterns I-VIII, which are presented in Fig. 5, allow charging or discharging the dc-link capacitor depending on a direction of the output current i

A a reference voltage between 0 and V

. For instance, when the converter output has dcHB

switching patterns III and IV can be chosen. The variable z corresponds to a sign of the H-bridge converter output voltage (for z = 1, v

HB

> 0, for z = 0, v

HB

The choice of a particular switching pattern depends on the H-bridge converter dc-link voltage

< 0). deviation Δ v dcHB v dcHB

V dcHB

, which is equal to the difference between the actual voltage value and the rated value,

, and the sign of the output current i

A

. These two variables can be expressed in a logical form as the H-bridge converter output voltage sign z given by z if

i

A

0

i f

v dcHB

0

,

(4) where ↔ is the operator of logical equality or exclusive nor, and Δ v dcHB between the actual and rated values ( Δ v dcHB the switching pattern.

= v dcHB

- V dcHB

is a dc-link voltage difference

). The equation (4) determines the choice of

Modulator operation

Switching patterns presented in Fig. 5 require modifications in PWM modulators for both NPC and Hbridge converters. The NPC converter modulator in switching patterns II, IV, VI, and VIII does not generate any switching and the output voltage in these patterns is 2 V dcHB

, 0, 0 and -2 V

In switching patterns I, III, V, and VII the pulses within one switching period T

S dcHB

respectively.

are distributed in the same manner, starting with a higher voltage level, followed by lower voltage in the middle of the switching period T s

and finishing with a higher voltage. This means that the modulator for the NPC converter does not changes its structure in all switching patterns and only modulating signals need to be recalculated. The schematic diagram of the NPC converter modulator is presented in Fig. 6, where

S

S

1

MNPC1

and S

S

3

and S

2

S

4

MNPC2

are the modulating signals for transistor S

1

and S

2

respectively. Switching signals

constitute complementary pairs. In Fig. 6.b the generation of the NPC converter output voltage in switching patterns I and III is presented. In Fig. 6.c, the generation of voltage is presented for switching patterns V or VII. In other switching patterns the modulating signals S

MNPC1 to 11 (II), 01 (IV or VI) or 00 (VIII).

S

MNPC2

are equal

The PWM modulator of the H-bridge converter is shown in Fig 7.a and its operation is illustrated in

Fig. 7.b and 7.c. The classic operation of the H-bridge converter is given in Fig. 7.b for switching patterns II, IV, VI and VIII. The converter in this case generates two pulses in each switching period T

S

For switching patterns I, III, V and VII, the converter produces only one pulse per period T

S

.

.

a)

S c

S

MNPC1

S

MNPC2

0

1

S

1

S

3 b)

S

MNPC2

1

S

MNPC1 v

NPC

0

I or III

S c c)

S

MNPC2

1

S

MNPC1

0 v

NPC

V or VII

S c

1 0 0

0

S

2

S

4 T

S

T

S

T

S

T

S

Fig. 6: PWM modulator of NPC converter: a) block diagram, b) output voltage generation for positive voltages, c) output voltage generation for negative voltages. a)

S c

S

MHB1

S

MHB2

0

1

S

5

S

6 b)

S

1

MHB1

S

MHB2

0 v

HB

IV or VIII II or VI

S c c)

S

1

MHB1

S

MHB2

0 v

HB

I or V III or VII

S c

0

1

S

7

S

8

0

T

S

T

S

0

T

S

T

S

Fig. 7: PWM modulator of H-bridge converter: a) block diagram, b) output voltage generation with two pulses in one switching period, c) output voltage generation with one pulse in a switching period.

In Fig. 6 and 7 one can see that all modulating signals S

MNPC1

, S

MNPC2

, S

MHB1

and S

MHB2

have to be calculated in each switching patter separately. These calculations are presented for switching patterns I and II in the next subparagraph.

Modulating signals calculation

The considered NPC-HB converter generates output voltage which is proportional to the modulating signal S

M

according to v

A0

2 dcHB

v

NPC

v

HB

,

(5) where the modulation index S

M following conditions 1 > S

M

[-1, 1]. In switching pattern I the modulating signal satisfies the

> ½. The output voltages of the NPC converter and H-bridge converter are as follows v

NPC

S

MNPC1

2 V dcHB

,

v

HB

S

MHB2

V dcHB

(6)

The modulating signal S modulating signal S

MHB1 can be seen that S

MNPC1 found

MNPC2

= 1, because the output voltage of the NPC converter is positive and the

= 1, because only one pulse is generated by the H-bridge converter. In Fig. 5 it

= S

MHB2

and by rewriting (5) both modulating signals S

MNPC1

and S

MHB2

can be

S

M

2 V dcHB

S

MNPC1

2 V dcHB

S

MHB2

V dcHB

S V V dcHB

,

(7) thus,

S

MNPC1

S

MHB2

2 S

M

1

,

(8)

In the switching pattern II the NPC converter does not modulate its voltage and the modulating signals equal to 1 S

MNPC1

=1, S

MNPC2

= 1. According to Fig. 5 and 7.b, the output voltages of the NPC and Hbridge converters are given as

v

NPC

2 V dcHB

,

v

HB

2 S

MHB1

1

V dcHB

.

(9)

From Fig. 7.b the following relation can be obtained: S

MHB2 we obtain the following:

= 1S

MHB1

, and by substituting (9) into (5)

S

MHB1

S

M

1 2

,

(10) thus

S

MHB2

S

M

3 2

,

(11)

A similar procedure can be extended to other switching patterns, the results of such calculations have been given in Table I.

Table I: Modulating signals in all switching patterns

Switching pattern

V

VI

VII

VIII

I

II

III

IV z

0

1

1

1

0

0

0

1

S

MNPC1

2 S

M

-1

1

2 S

M

0

0

0

0

0

S

MNPC2

1

1

1

1

2 S

M

+1

1

2 S

M

+2

0

S

MHB1

1

S

M

-1/2

0

S

M

+1/2

1

S

M

+1/2

0

S

M

+3/2

S

MHB2

2 S

M

-1

S

M

+3/2

2 S

M

-S

M

+1/2

2 S

M

+1

S

M

+1/2

2 S

M

+2

S

M

-1/2

Simulation results

The dc-link voltage balancing method has been adapted to the three-phase converter simulation model, the results of which are presented in Fig. 8. The parameters of the simulated converter are presented in

Table II. The output voltage and current waveforms are compared to the waveforms of the NPC converter (NPC-3L) having the same parameters (Fig. 9). It is assumed that the NPC converter in both cases is supplied from two dc-voltage sources and third harmonic injection in modulating signals is done.

Table II: Parameters of the NPC-HB model

Parameter name

Line-to-line rms output voltage

NPC converter dc-link capacitor voltage

H-bridge converter dc link capacitor voltage

Output current amplitude

Fundamental frequency

Modulation index

Output phase shift angle (inductive)

Capacitance of H-bridge converter dc-link capacitor

Switching frequency

Symbol

V ll

V dcNPC

V dcHB

I

V f m m a

φ

C dcHB f

S

Value

1000 V

707 V

353 V

12.25 A

50 Hz

1.0

5 deg

0.75 mF

1 kHz or 3 kHz

a)

800

400

0

-400

-800

800

400

0

-400 f

S

= 1 kHz b)

800

400

0

-400

-800

800

400

0

-400 f

S

= 3 kHz

-800

400

0

-400

15

10

-5

-10

-15

5

0

10

0

THD

I

= 6.03%

-800

400

0

-400

15

10

-5

-10

-15

5

0

10

0

THD

I

= 1.44%

-10

0 5 10 time, t (ms)

15 20

-10

0 5 10 time, t (ms)

15

Fig. 8: Voltages and current waveforms of the NPC-HB converter simulation model: a) for switching frequency f

S

= 1 kHz, b) for switching frequency f

S

= 3 kHz. a) b)

800 800

20

400 f

S

= 1 kHz

400 f

S

= 3 kHz

0

-400

0

-400

-800

15

10

A

THD

I

= 10.17%

-800

15

10

A

THD

I

= 3.56%

-5

-10

5

0

-5

-10

5

0

-15

0 5 10 time, t (ms)

15 20

-15

0 5 10 time, t (ms)

15 20

Fig. 9: Output voltage and current of the three-level NPC converter simulation model: a) for switching frequency f

S

= 1 kHz, b) for switching frequency f

S

= 3 kHz.

Comparing the voltage waveforms of the NPC-HB converter (Fig. 8) with such waveforms from the

NPC-3L converter (Fig. 9) one can see that the output current total harmonic distortion THD

I

is lower in case of the NPC-HB converter. With the higher switching frequency dc-link voltage variations

Δ v dcHB

become lower. Moreover, the number of switchings in the NPC converter part of the NPC-HB converter is also reduced compared to the NPC-3L converter. This advantageous feature is explained in Fig. 10 when the number of switchings N

S

, defined as the number of device turning on and turning off in a single phase of the NPC converter of the NPC-HB converter, is given. The number of switchings N

S

of the NPC-HB converter are compared with such numbers of the NPC-3L converter. In the NPC-3L converter N

S

is proportional only to the switching frequency and is equal to

N

SNPC3L

= 2 f

S

/ f m

, where f m

is the fundamental frequency equal to f m

= 50 Hz. a) b)

120

NPC-3L

120 f

S

= 3 kHz

80

NPC-HB

80 NPC-3L

NPC-HB

40

NPC-3L

40

0

0 0.2

NPC-HB

0.4

0.6

modulation index, m a f

S

= 1 kHz

0.8

1

0

1 1.5

2 2.5

switching frequency, f

S

(kHz)

3

Fig. 10: Number of switchings N

S

in NPC converter single-phase of the NPC-HB converter: a) as a function of modulation index m a switching frequency for m a

for switching frequency f

S

= 1 kHz and 3 kHz , b) as a function of

= 1 and other parameters the same as in Table II

For each modulation index m a

(Fig. 10.a) the number of switchings N

S

NPC-3L converter and are slightly larger than 1/2 N

SNPC3L

is lower than this number in the

. This reduction is the advantage of the presented method. In Fig. 10.b it can be seen that similarly to the NPC-3L converter the number of switchings in NPC-HB converter increases with increasing switching frequency.

Experimental results

The considered NPC-HB converter has been build (Fig. 11.a) and tested. The H-bridge dc-link voltage balancing method, which is presented in this paper, has been implemented into the experimental model of the converter. The correctness of this method is proved by oscilloscope waveforms (Fig. 11.b), which are obtained for the same parameters as in Table II (with the switching frequency f

S

= 3 kHz).

In Fig. 11.b one can see the output voltage where some additional voltage pulses exists. These pulses are the result of nonequal switching times of the higher and lower blocking voltage IGBTs. a) b) v

A0 v dcHB i

A

Fig. 11: Experimental results of the NPC-HB converter model: a) converter photograph, b) output voltage and current with the HB-bridge dc-link voltage obtained at full load equal to 15 kVA

That pulses can be compensated by correcting the modulating signals from Table I. For presenting purposes (Fig. 11.b) in the control of the dc-link voltage v dcHB

a hysteresis band of 10 V is applied.

Comparison of NPC-HB converter with other solutions

The main advantage of the presented NPC-HB converter over other solutions is that the converter is built from two typical converters, the NPC and H-bridge converter. This component converters are available in single packages making the design of the NPC-HB converter easier. This is not applied to the converter ANPC-5L [11]. Beside having many superior features like minimum number of switchings on the higher voltage devices, the ANPC-5L converter is patented [11].

The presented dc-link voltage balancing method for the NPC-HB converter is similar to that used in

ANPC-5L because in both converters the redundant states, which allows balancing, exist when the converter output voltage is v

A0

= v dcHB

or v

A0

= v dcHB

.

The authors of this paper consider the balancing method based on SHE modulation [10] as interesting.

However, this method demands large lookup tables and requires higher switching frequency in the Hbridge converters. The proposed balancing method seems to be simpler to be implemented.

Conclusions

The dc-link voltage balancing method for the NPC-HB converter is presented in this paper. The method, which is based on modification of PWM switching patterns, shows benefits compared to the three-level NPC converter. These benefits are related to a lower THD of the output current and lower number of switchings in the component NPC converter.

Despite the higher number of switchings in the NPC converter compared to the ANPC-5L and NPC-

HB converter with SHE modulation, the proposed balancing method is relatively simple.

The method has been implemented and verified by using the experimental model of the NPC-HB converter. During experimental tests short pulses in the output voltage were observed, these pulses result from nonequal switching times of higher and lower blocking voltage switches. The authors believe that these pulses can be compensated in the converter PWM modulators.

References

[1] Rodríguez J., Lai J.-S. Peng F.Z.: Multilevel inverters: a survey of topologies. controls, and applications .

IEEE Trans. Ind. Electron. vol. 49, no. 4, Aug. 2002, pp. 724–738

[2] Rodríguez J., Franquelo L. G., Kouro S., Leon J. I., Portillo R. C., Prats M. A. M., Perez M. A.: Multilevel converters: an enabling technology for high-power applications . Proc. IEEE, vol. 97, no. 11, Nov. 2009, pp. 1786–1817

[3] Malinowski M., Gopakumar K., Rodriguez J. Perez M.: A survey on cascaded multilevel inverters . IEEE

Trans. Ind. Electron., vol. 57, no. 7, Jul. 2010, pp. 2197–2206

[4] Veenstra M.: Investigation and Control of a Hybrid Asymmetric Multilevel Inverter for Medium-Voltage

Applications . PhD thesis, Lausanne, Switzerland, 2003

[5] Veenstra M., Rufer A.: Control of a Hybrid Asymmetric Multilevel Inverter for Competitive Medium-

Voltage Industrial Drives . IEEE Trans. Ind. Applications., vol. 41, no. 2, Mar–Apr 2005, pp. 655–664

[6] Steimer P. K., Manjrekar M. D.: Practical medium voltage converter topologies for high power applications . IAS 2001, pp. 1723–1730

[7] Mekhilef S., Abdul Kadir M. N.: Voltage control of three-stage hybrid multilevel inverter using vector transformation . IEEE Trans. Power Electron., vol. 25, no. 10, Jan. 2010, pp. 2599–2606

[8] Chattopadhyay S. K., Chakraborty C., Pal B. C.: A hybrid multilevel inverter topology with third harmonic injection for grid connected photovoltaic central inverters . ISIE 2012, pp. 1736–1741

[9] Yinglin Xue, Zheng Xu, Qingrui Tu: Modulation and control for a new hybrid cascaded multilevel converter with DC blocking capability . IEEE Trans. Power Del., vol. 27, no. 4, Oct. 2012 pp. 2227–2237

[10] Silva C. A., Cordova L. A., Lezana P., Empringham L.: Implementation and control of a hybrid multilevel converter with floating DC links for current waveform improvement . IEEE Trans. Ind. Electron., vol. 58, no. 6, Jun 2011, pp. 2304–2312

[11] Winkelnkemper M., Wildner F., Steimer P. K.: 6 MVA five-level hybrid converter for windpower . PESC

2008, pp. 4532–4538