Design Note 03

(formerly Application Note 103)

Signal Limiter

for

Power Amplifiers

The circuits within this application note feature THAT4301 Analog Engine® to provide the

essential elements of voltage-controlled amplifier (VCA) and rms-level detector (RMS). Since

writing this note, THAT has introduced several new models of Analog Engines, as well as new

VCAs. With minor modifications, these newer ICs are generally applicable to the designs shown

herein, and may offer advantages in performance, cost, power consumption, etc., depending on

the design requirements. As well, a standalone RMS is available to complement our standalone

VCAs. We encourage readers to consider the following alternatives in addition to the 4301:

•

Low supply voltage and power consumption: 4320

•

Low cost, supply voltage, and power consumption: 4315

•

Low cost and power consumption: 4305

•

High-performance (VCA only): 2180-series, 2181-series

•

Dual (VCA only): 2162

•

RMS (standalone): 2252

For more information about making these substitutions, please contact THAT Corporation's

technical support group at apps_support@thatcorp.com.

THAT Corporation; 45 Sumner Street, Milford, Massachusetts 01757-1656; USA

Tel: +1 (508) 478-9200; Fax: +1 (508) 478-0990; Web: www.thatcorp.com; Email: info@thatcorp.com

Copyright © 2009, THAT Corporation; All rights reserved. Document 600034 Revision 02

Design Note 03

(Formerly Application Note 103)

Signal Limiter for Power Amplifiers

Abstract

Power amplifiers, when driven out of their

linear range of operation, sound particularly

bad, and can produce damage to themselves or

the transducers to which they are connected.

The design of traditional protection circuits

is complicated by the various performance,

cost, and sonic tradeoffs involved. There is

certainly no one right answer to the limiter

puzzle. The circuits presented here, however,

are designed to maintain a high level of sonic

integrity, while remaining cost-effective.

These circuits combine active limiting with a

diode-based clipper to provide excellent driver

protection while avoiding the sonic degradation

of simpler designs.

An innovative nonlinear

capacitor circuit further improves the sonic

performance of the limiter.

The design is based on the THAT 4301

Analog Engine®, and thus requires only a single

IC, a couple of transistors and diodes, and a

handful of passive components.

Signal Limiter for Power Applications

The simplest circuits used to prevent overload

in power amplifiers usually employ diode clippers.

These have the advantages of being both fast and

inexpensive. They also sound quite unpleasant

when the amplifier is overdriven for more than a

few tens of milliseconds. As a result, users may

avoid fully exploiting the amplifier’s available

headroom because they fear the sonic results of

overload. In the worst case, an amplifier with

otherwise admirable performance may gain a

reputation for poor sound quality.

The significantly improved version shown here

employs two stages of protection — a VCA-based

limiter which quickly and automatically reduces the

input signal level to just below the overload point,

and a conventional diode clipper to handle any

short duration excursions while the limiter stage

reacts.

The circuits shown are built around the THAT

4301 Analog Engine®. The THAT 4301 provides a

single-chip solution for a variety of analog signal

processing applications. It includes a high quality

Blackmer gain-cell VCA, an RMS-level detector, and

three general purpose op amps, two of which are

undedicated. The circuits shown are easily adaptable for use with separate THAT Corporation VCAs

and RMS-level detectors where even higher

performance is required.

Assumptions

We will approach the design of the circuit using

an approximately real-world example with the

following assumptions:

1. The power amplifier’s decibel voltage gain is

32 dB, a common value;

2. The maximum average power that can be dissipated by the 8 Ω load is 600 W;

3. The maximum peak power that can be dissipated by the 8 Ω load is 6 kW.

With these assumptions, we make the following

calculations:

1. The voltage gain of the power amplifier is

32

A V = 10 20 l 40

2. Assuming a sine wave output, the output voltage at

maximum average power dissipation is

Vout max avg P = 600W % 8 = 70V RMS

3. The output at maximum peak power dissipation

is:

Vin max peak P = 6000W % 8 = 220V RMS

Knowing these values, we can calculate the appropriate limiter and clipper output voltages as

Vin max avg P =

70V RMS

40

And Vin max peak P =

= 1.75V RMS

220V RMS

40

= 5.5V RMS

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright © 2009, THAT Corporation; Document 600034 Rev 02

Document 600034 Rev 02

Page 2 of 8

Design Note 03

Signal Limiter for Power Amplifiers

Basic Feedback Limiter with Diode Clipper

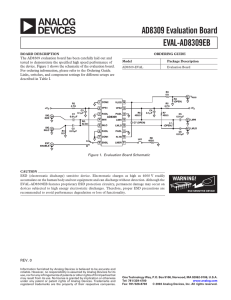

The circuit shown in Figure 1 demonstrates the

basic feedback limiter with adjustable clipper. The

input signal is fed to the limiter circuitry at the

node labeled “Input”. The limiter’s output is sent

to the power amplifier from the point labeled “To

Power Amplifier”. In addition, the output from the

power amplifier is fed back to the limiter circuit by

way of the node marked “From Power Amplifier

Output”.

threshold for long, the signal’s rms value will

exceed the limiter’s average power threshold,

causing the limiter to quickly reduce the level of

signal being fed to the amplifier. In this way,

inaudible (but potentially damaging) peaks of short

duration will be clipped, while longer duration

peaks will be handled by the limiter, and little

audible impairment should occur.

The Clipper

Under normal operation, the input signal is

below the limiter’s threshold and so the VCA is at

unity gain, its lowest distortion region.

Figure 2 shows the clipper circuit used in this

design.

A trans-impedance amplifier, OA3,

converts the output current from the VCA to a

voltage which drives the actual clipper circuitry.

When OA3’s output voltage exceeds the threshold

set by VR1, the transistor pair Q1 and Q2 combine

to bypass R2 and clip the output to a fixed level.

For peak output levels of short duration which

exceed the predetermined clip level, the clipper

circuit “hard limits” the output to this level,

performing very much like the (adjustable) diode

clipper that it is. If the output level remains above

+15

R3

10k

Q2

2N3906

D3

1N4148

Symmetry

Adjustment

+15

300k

VR1

20k

+15

R6

VR4

50k

220u

C6

R5

C11

51R

C3

R1 17

Input

20k

22u

14

EC+

SYM

20k

11

13

V+

IN

OUT

GND

EC-

9

OA3

V-

10

-15

R10

Zero dB Reference Level

10k

D1

1N4148

C13

R12

22n

R14

10k

19

OA1 20

U1D

4301P

Clipper Circuit

-15

C7

100n

VCA

18

Q1

2N3904

R4

10k

12

U1A

4301P

16

100k

D4

1N4148

47p

R2

-15

15

To Power Amp Input

D2

1N4148

Make-up Gain Adjustment

+15

+20dB

R8

VR3

50k

1M2

-20dB

-15

Control Port Buffer

7

OA2 6

8

U1C

4301P

RMS

Detector

R13

4

4k99

5

OUT

IN

CT

IT

1

C4

2

U1B

4301P

Threshold

Amplifier

R15

R16

820k

R7

75k

22u

91k

VR2

50k

From Power Amp

Output

R11

10k

R9

2M

-15

Stereo

Connection

C2

220u

Figure 1. Schematic of basic signal limiter

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright © 2009, THAT Corporation

Document 600034 Rev 02

Page 3 of 8

Design Note 03

Signal Limiter for Power Amplifiers

1. Vin dB is the input level in decibels and Vout

the output level in decibels,

is

2. GdB is the VCA gain in decibels, and

+15

R3

10k

dB

3. A is the gain between the detector and the

control port of the VCA.

Q2

2N3906

D3

1N4148

C11

VR1

20k

To Power Amp Input

D4

1N4148

47p

R2

20k

From VCA

OA3

12

R4

10k

U1A

4301P

Q1

2N3904

-15

The minus sign in the side-chain gain equation

comes from the fact that this is a compressor

circuit, and the gain of the VCA moves in the

opposite direction of output signal amplitude.

Combining these equations yields

V out dB = V in dB − A % V out dB

which can be rearranged to form

Figure 2. Detail of clipper circuit

Using our design example, the peak allowable

power is specified as 220 VRMS, and since we are

ultimately clipping the signal to a square wave, this

is equivalent to 220 Vpeak. Given the power amplifier’s gain of 40, the limiter must clip at 5.5 Vpeak.

The two 1N4148 diodes prevent base-emitter

breakdown in Q1 and Q2. The addition of these

diodes means that the clipping voltage will be two

diode drops (approximately 1.2 V) greater than the

voltage at the bases of Q1 and Q2. VR1 adjusts the

voltage at the base of Q1 between 0 and -7.5 V, and

at the base of Q2 between 0 and +7.5 V. Since we

want the limiter to clip at 5.5 V, VR1 should be

adjusted to provide -4.3 V and 4.3 V at the bases of

Q1 and Q2, respectively.

The Limiter

To form the limiter block, the VCA in Figure 1

is configured as a high-compression-ratio feedback

compressor. Under normal operation, the amplifier output is below the compressor’s threshold

voltage, the VCA’s EC- control port is kept at zero

volts, resulting in no compression or limiting

action. Above the threshold level, the threshold

amplifier conducts and closes the feedback loop

from the RMS level-detector to the VCA, resulting in

the desired limiter function.

Figure 3 shows a simplified diagram of a

feedback (FB) compressor. By inspection,

V out dB = V in dB + G dB,

And

V in dB

V out dB

=1+A

This is the compression ratio of the

compressor. To get the compressor to act as a

limiter, we need to set the compression value to a

high value. A suitable and convenient value is 21,

and we can calculate the gain required to achieve

this compression ratio as

A=

V in dB

V out dB

− 1 = 21 − 1 = 20

A side-chain gain of 20 will, therefore, yield a

compression ratio of 21, resulting in the expected

limiter behavior.

The RMS Level-Detector

THAT Corporation’s RMS level-detectors generate an output voltage that is proportional to the

signal power in decibels. A user-programmable

“reference level” determines the signal level for zero

Vin

Vout

Ge

-Ae

Feedback Compressor

G dB = −A % V enc dB, Where

Figure 3. General feedback compressor topology

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright © 2009, THAT Corporation

Document 600034 Rev 02

Page 4 of 8

volts output from the detector. The detector output

will then swing positive (for input signal levels

above the reference level) or negative (for signals

below reference) at a constant 6 mV/dB.

To calculate the true-rms value of an ac input

signal, THAT’s RMS level-detectors first full-wave

rectify, then log the signal. The logged signal is

then doubled, which effectively squares the signal

since the operation is carried out in the log

domain. The subsequent square root operation is

actually performed implicitly at the exponential

input of the VCA.

Design Note 03

Signal Limiter for Power Amplifiers

3rd harmonic distortion in the output of the VCA.

With this in mind, the filter time constants must

balance the need for low distortion with continuous

signals against the need for fast operation in the

presence of transients.

From long experience, a cutoff frequency of

approximately 5 Hz has been found to be an effective compromise. This frequency is well below the

audio band and is sufficient to keep distortion low.

The recommended value for IT (the timing current)

is 7.5 μA, resulting in a timing capacitor of approximately 10 μF.

A better solution to the distortion vs. speed

issue is presented later in this paper as Extra

Credit: The Nonlinear Capacitor.

Zero dB Reference Level

From Power

Amp Output

R16

R15

75k

820k

R11

10k

VR2

50k

R7

91k

C4

22u

R9

2M

RMS

1

4

IN OUT

2

5

CT

IT

U1B

4301P

To Side-chain

-15

Stereo Connection

C2

220u

Figure 4. Detail of RMS detector circuitry

The “mean” operation is carried out by filtering

the rectified and logged signal, and it is this

log-domain filter that sets the time constants

(attack and release times) for the limiter. Referring

to Figure 4, the log-domain filter consists of an

internal diode biased by a fixed DC current (IT),

along with external components R9, which establishes IT, and C2, the timing capacitor itself. The

time constant of the filter is calculated from:

$ = C2 %

VT

IC

and therefore

C2 =

1

2 % % fC %

VT

IC

A compromise is involved in setting the filter

time constants, because the filter also must smooth

the rectified and logged input signal. Without the

smoothing operation, the 2nd harmonic generated

by the rectification process result in high levels of

The above calculations assume a stand-alone

RMS level-detector. When the detector is placed in

a feedback compressor topology, the effective time

constant that results is calculated by taking the

level detector’s stand-alone time constant and

dividing it by the compression ratio. Therefore, if

we plan to operate with a compression ratio of, say,

20:1, we will need to increase the timing capacitor

by a factor of 20. So, for our design the timing

capacitor, C2, becomes 220 μF, the nearest

standard value.

The timing current is set by R9, and is calculated as

RT =

−V SS

IT

=

15V

7.5A

= 2 M

Knowing this, we can calculate the “zero dB reference current” for the RMS level-detector (recall that

this is the input current which result in zero volts

output from the detector. This is also the value that

will produce unity gain through the VCA):

I ref = 1.13 % I T = 8.5 A

As previously stated, this circuit is specifically

designed to limit at 70 VRMS. However, for the sake

of flexibility, we are going to provide a trim to

accommodate a range of 7 - 70 VRMS by adding the

resistive pad composed of R16, R11, and VR2.

This results in an approximately 10:1 divider.

With this pad in place,

reduced to 7 VRMS at the top

Now the input to the RMS

treated as a virtual ground.

a 70 VRMS input is

of the potentiometer.

level-detector can be

Knowing this, along

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright © 2009, THAT Corporation

Document 600034 Rev 02

Page 5 of 8

Design Note 03

Signal Limiter for Power Amplifiers

R10

10k

D1

1N4148

C13

To VCA

Control Port

22n

R14

19

OA1 20

U1D

4301P

R12

10k

7

OA2 6

1N4148

R8

From RMS

Detector

4k99

8

Make-up Gain Adjustment

+15

+20dB

100k

18

R13

D2

U1C

4301P

Threshold

Amplifier

VR3

50k

560k

-20dB

-15

Control Port Buffer

Figure 5. Detail of side-chain circuitry

with the detector’s reference level, we can calculate

the largest value of input resistor required as,

R RMS IN =

7V RMS

8.5A

A buffer =

= 820 k

This is the value that will be seen by the detector when the wiper of VR2 is at the bottom of its

range.

At the other extreme, we desire the limiter to

respond at a power amplifier output of 7 VRMS. At

this level, the 10:1 pad will result in 0.7 VRMS at the

top of VR2. The resistor value required to generate

the detector’s reference level is

R RMS IN =

0.7V RMS

8.5A

The gain of the control port buffer is,

−R14

R12

−100 k

10 k

=

= −10

for a net gain of 20.

To make the circuit more versatile, an optional

“make-up gain” circuit comprised of R8 and VR3

has been added to allow for convenient manual

gain adjustment of the limiter circuit over a range

of ±20 dB. To calculate the sensitivity of the

make-up gain circuit, we first compute the current

sensitivity at the inverting input of OA1,

= 82 k

I

dB

=

6.5 mV

dB

R12

13

mV

A

dB

= 10 k

= 1.3 dB

By choosing a value of 91 kΩ for R7, we get

81 kΩ as the parallel combination of R15 and R7

when VR2 is at the top of its range.

The Side-chain

The circuit in Figure 5 shows an isolated view of

the side-chain of Figure 1. When the signal is

above the limiter threshold voltage, the gain for the

threshold amplifier is,

Since the maximum voltage across R8 is ±15 V,

and we want the resulting current to cause a ±20

dB swing,

R8 =

15V

20 % 1.3

A

dB

= 576 k

560 kΩ is the closest 5% value to the calculated

A threshold =

−R10

R13

=

−10 k

4.99 k

= −2

value.

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright © 2009, THAT Corporation

Document 600034 Rev 02

Page 6 of 8

Design Note 03

Signal Limiter for Power Amplifiers

internal to the IC. During transients, the diode will

conduct only during short periods, and this can

result in high peak currents. In order to prevent

these currents from injecting unwanted signals

elsewhere in the circuit, a charging current path

directly from VCC is usually required.

Other Issues

The VCA in the THAT 4301, like all of the THAT

Corporation’s Blackmer gain-cell VCAs, operates in

Class AB mode. Due to minor differences between

the transistors in the gain cell, there is often a

slight asymmetry between the gain of upper and

lower halves of the output waveforms. The result

of this asymmetry is a potential maximum THD+N

of 0.7% at unity gain.

To accomplish this, C6 should be placed so that

its grounded side is close to the grounded side of

C2, and these two devices should connect to each

other before connecting to system ground.

If this maximum THD+N is acceptable in a

given application, no external distortion trim (R6

and VR4 in Figure 1) is required. This might be

the case, for example, where the limiter is feeding a

subwoofer

amplifier

or

other

low-fidelity

application.

Closing Thoughts

Although speaker protection can be had with

lower-cost amplifier clipping circuits, peaks of long

duration may still result in speaker damage. As

well, the sound of low-cost clippers may keep users

from using the maximum headroom available from

an amplifier.

With the distortion trim, THD+N can be

reduced to maximum 0.007% (unity gain with

0 dBV input at 1 kHz).

The high-fidelity limiter described in this application note keeps an amplifier sounding good even

when its input is overdriven. The result is a

cleaner, more powerful impression, and better

protection for the speaker system.

An

important

application

consideration

concerns the bypassing and layout of the THAT

4301. As was mentioned in the section on the RMS

level-detector, the timing capacitor is part of a log

filter composed of the capacitor and a diode

R15

From Power Amp

820k

4

To Side-Chain

IN

OUT

RMS

5

CT

1

C4

2

R7

100k

22u

IT

U1B

4301P

VR2

50k

R9

2M

-15

R17

D5

2M

D6

MBD101

MBD101

C8

C1

1u

47n

2

1

R18

3

U2A

LF353

200R

C5

10u

Figure 6. RMS detector with nonlinear capacitor circuit

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright © 2009, THAT Corporation

Document 600034 Rev 02

Page 7 of 8

Design Note 03

Signal Limiter for Power Amplifiers

Extra Credit: The Nonlinear Capacitor

We mentioned earlier that RMS level-detectors

exhibit low-frequency 2nd harmonic ripple (the

result of their finite averaging time) which results

in a 3rd harmonic component from the VCA. We

nearly eliminated this component by way of the log

filter capacitor, C2. However, while increasing the

value of this capacitor provides good distortion

performance, it also results in slower response

time than may be desired in some applications.

2. The value of C8 is chosen so that fC resulting

from C8 and R17 is below the audio range,

fC =

1

2 % R17 % C8

= 1.6 Hz

3. It may be shown that, when log-based RMS

level-detectors are connected to exponentiallycontrolled VCAs, the ratio of the ripple-induced 3rd

harmonic to fundamental for a given τ at a given

frequency ω is,

In order to keep distortion low and provide

rapid response to transient signals, a “nonlinear

capacitor” (NLC) circuit can be incorporated in the

design. This circuit effectively changes the timing

capacitor value based on the characteristics of the

incoming signal.

I 3rd

I 1st

=

This may be rearranged to give,

$2 =

In the NLC circuit, the RMS level-detector is

configured as a typical detector, but the timing

capacitor is replaced with C1 (see Figure 6), which is

connected to the virtual ground of op amp U2A. The

gain of this stage is set by the ratio of C1 and C8.

Dynamically, C1 and C5 are in parallel. Under

conditions where the op amp’s output is not limited

by D5 and D6 (”slow mode”), C5 is effectively multiplied by one minus the closed-loop gain of the U2A,

the result of the well-known Miller Effect. When D5

and D6 limit the output of the op amp, C5 (with no

Miller Effect multiplication factor) is simply in

parallel with C1 (”fast mode”).

The simplified transfer functions for this circuit

are:

For Steady-State Inputs: C TIME = C1 + C5 % 1 + C1

C8

For Transient Inputs:

C TIME = C1 + C5

Here are some important design equations and

a few tips on fine-tuning the values in the NLC

circuit:

1. The value of R17, the resistor which provides

a return path for the op amp’s bias current, is

chosen to produce a minimal DC offset as a result

of the bias current. If your diodes are leaky, you

may be able to use a much larger value of R17.

1

4 1 + (2 * ) 2 $ 2

2

I 1st

4 % I 3rd

(4 f

−1

)2

Presumably, one intends to design a low distortion circuit and, therefore, we may assume that,

I 1st

I 3rd

>> 1

Consequently,

$2

l

I 1st

4 % I 3rd

2

(4 f ) 2

We may then state that

$l

I 1st

4 % I 3rd

(4 f )

=

I 1st

16 f % I 3rd

Assume that we are willing to accept 1%

THD+N at 50 Hz. We can then calculate (for slow

mode operation)

$ Slow l

I 1st

16 f % I 3rd

=

1

16 f

%

I 1st

I 3rd

or

$ Slow l

1

16 % 50 Hz

% 100 = 0.04 s

A relatively complex analysis that is beyond the

scope of this paper will show that the average

ripple voltage at a given τ and frequency is,

V R avg =

VT

2 2 %*$

=

VT

4 2 %f$

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright © 2009, THAT Corporation

Document 600034 Rev 02

Page 8 of 8

At room temperature, VT = 26 mV, and from

our design requirement, the frequency of interest is

50 Hz. Therefore,

V R avg =

0.026 V

, or

4 2 % 50 Hz % 0.04

VR avg = 731 V = 1.03 mVpeak

We can convert this to decibels by dividing the

result by the THAT 4301’s control voltage constant

(6.5 mV per dB),

V R avg dB =

1.03 mV

V

0.0065 dB

IT

VT

We choose to allow 3 dB of change at the detector output before the diodes turn on and switch to

fast mode. This provides ample margin above the

0.16 dB calculated in section 3 above, thus preventing 50 Hz sine wave signals from activating fast

mode.

If we use Schottky diodes, and allow for the 3

dB swing before diode turn-on,

AV =

0.4 V

3 dB % 6.5

which sets

capacitors,

= 0.16 dB

4. Let us assume that we want the NLC’s fast

mode to be 20 times faster than the slow mode. We

can use the equation,

C Slow = C.R. % $ Slow

Design Note 03

Signal Limiter for Power Amplifiers

l 220 F

(where C.R. = the compression ratio)

to determine the required effective timing

capacitance in slow mode. The fast mode capacitance would then be,

AV =

mV

dB

l 20.5

the

ratio

of

the

gain-setting

C1

C8

Note that if an even larger band is needed, one

may use the transistor arrangement shown in

Figure 2 in place of diodes in this circuit.

6. Combining some of the equations in 4 and 5

above, we may state that,

C1 + C5 % 21.5 = 220 F

and

C Fast =

C Slow

20

= 11 F

C1 + C5 = 11 F

The slow mode capacitance is calculated as,

C Slow = C1 + C5 1 +

It follows that,

C1

C8

whereas the fast mode capacitance is simply C1

in parallel with C5, or

C Fast = C1 + C5

Since we

capacitance,

already

11 F − C5 + C5 % 21.5 = 220 F

and then

C5 =

know

our

desired

fast

C1 = 11 F − C5

220 F −11 F

20.5

= 10.2 F

We can now determine that

C1 = 11 F − 10.2 F l 1 F

and finally

5. The required gain is determined by calculating how many decibels will correspond to a single

diode drop. Green LEDs have a forward drop of

approximately 2.2 V, while red LEDs have a

forward drop closer to 1.6 V.

Anti-paralleled

silicon diodes have a forward drop of about 0.65 V,

and anti-paralleled Schottky and germanium

diodes have a forward drop of approximately 0.4 V

(all depending, of course, on the current through

the diode).

C8 =

C1

20.5

= 47 nF

This circuit can be used to replace C2 in

Figure 1. By doing so, the basic limiter circuit

becomes much more flexible, eliminating the need

to trade fast attack times for distortion

performance.

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright © 2009, THAT Corporation