Practical On-Line Identification of

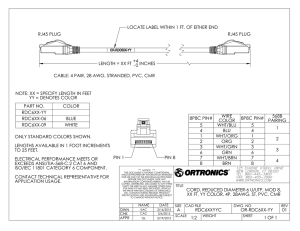

advertisement

Practical On-Line Identification of

Power Converter Dynamic Responses

Botao Miao, Regan Zane, Dragan Maksimovic

Colorado Power Electronics Center

ECE Department

University of Colorado at Boulder, USA

Email: {botao.miao, reganzane, maksimov)@colorado.edu

Absfrucf-A practical approach for on-line identification of

power converter dynamic responses using low-cost digital

hardware is presented, The development provides a first step

towards adaptive power delivery in electronic systems and can be

used for simple off-line controller design. A hardware efficient

algorithm is derived and verified with experimental results using

a 90 W forward converter with an FPGA-based digital controller.

1.

INTRODUCTION

Digital control of high-frequency switching power

converters has been shown to provide many possible benefits,

including improved immunity to noise and parameter

variations, reduction of external components, real-time

programmability and Integration with advanced features such

as adaptive calibration and health monitoring (diagnostics) [ 131. In this paper, we lay the foundation for broadening the

benefits of digital control by presenting a practical approach

for performing active identification of the open-loop

characteristics of digitally controlled power convertcrs. These

findings provide the first step towards automating the control

loop design for switched-mode power converters, or adaptively

tuning the controllcr parameters to address changes in

operating conditions. Thcse capabilities can be particularly

beneficia1 in multi-module power delivery systems where selfcontroller design techniques may utilize the identification

results to update control parameters to maintain stability at the

individual module level, or to feed information back to a lower

bandwidth system level controller.

We focus our attention on nonparametric methods [4-8] with

the objective of accomplishing on-line assessment of system

dynamic responses and stability margins with only limited

knowledge of the system. This allows accurate identification in

the presence of system faults, load or source changes, or other

unpredictable system variations. The control to output impulse

rcsponse is determined through cross-correlation methods [4],

using injection of a pseudo random binary sequence (PRBS)

into the control input for system perturbation and identification.

Detailed analysis o f the identification method applied to power

converters and further algorithm optimizations are given in [9],

whereas this paper focuses on application of the basic approach

and realistic hardware implementation.

The digcst includes a brief review of the correlation method

applied to identification of digital systems in Section 11,

followed by a fast and efficient algorithm for hardware

implementation based on the Walsh-Hadamard transformation

(WHT) to realize the correlation operations in Section 111. In

Section IV considerations for hardware implementation are

discussed. An experimental platform is then described together

with experimental results in Section V to demonstrate active

identification of a 90 W 50 V to 15 V forward converter with

an FPGA-based digital controller.

11. CROSS-CORRELATION

METHOD

..

4I

1

Here we briefly review application of the cross correlation

method to digitally sampled and controlled switching power

converters. In steady state, for small-signal disturbances, a

power converter can be regarded as a linear time-invariant

discrete-time system, where the sampled system can be

described by

Switched-Mode Power Converter b-1

1

I

Idenfgcation & design

P

where y(m) is the sampled output signal; u(m) is the input

digital control signal; h(m) is the discrete-time system impulse

response; and v(m) represents disturbances, including

Figure 1. lntellieent converter module block diagram

switching noise, measurement error, quantization noise, etc.

The cross-correlation of the input control signal u(m) and the

This work is supponed by Mr. Roben Button at the NASA Glenn Research

Cenler in Cleveland, Ohro as part of NASA’s research and development output signal y(m) is given by

program entitled “lntelligenl Power Management and Distribution Systems”.

0-7803-89751/05/$20.00 02005 IEEE

57

#bit

10 9 8 7 6 5 4 3 2 I

M-sequence PRBS

q

Kw""( m - j ) + R",( m )

=

,=I

I

where R,,(m) is the auto-correlation of the input signal. Now, if

the input control signal u(m) is selected to be white noise, then

we benefit from the following characteristics:

(3)

In other words, the auto-correlation of the input R,,(m) is an

ideal delta function and the cross correlation of the white noise

input with disturbances v(m) i s ideally zero. Under the

conditions of (3), the cross-correlation of (2) can be reduced to

R,(d =h(m).

DFP

(5)

H W ) .

However, (5) is only exact for ideal white noise injection

and infinite samples in (2). A simple compromise in a digitally

controlled power converter is to approximate white noise

through use of PRBS perturbations. The PRBS is periodic and

deterministic and can be easily generated in a digital system

using a shift register with feedback. An n-bit shift register can

generate several diff'erent sequences, including the maximum

length sequence (M-sequence) as shown in Fig. 2, with a data

length ofp = 2"- 1. The corresponding P M S can be obtained

by replacing 1 by +e and 0 by -e in the M-sequence.

A detailed analysis of the noise effects on identification,

selection criteria for the PRBS sampling frequency fo and

length p , and modifications to the basic correlation approach

for improved results are given in [ 9 ] . Here we focus more on

the practical aspects of implementation. The following section

describes an efficient and fast algorithm for hardware

implementation.

111. EFFICIENT

ALGORITHM

REALIZATION:

THEWALSH-

HADAMARD

TRANSFORMAT~ON

(WHT)

For a PRBS signal with a period of p , the cross-correlation

of (2) can be rewritten in a more suitable form for hardware

implementation as

R,

(nl) =

5

y(n)u(n

n=Q

+m)

Figure 2. Thc M-sequence generated by a IO-bit shift register

where in) is a periodic signal. If the periodp is selected to be

sufficiently long compared to the impulse response time and

the non-idealities of the PRBS are neglected [ 9 ] , then the

cross-correlation can again be related to the system impulse

response as

h ( p - m ) = R,v((m) m = 1 , 2 ; . . p .

Equations (6) and (7) can be written in matrix form as

(4)

Thus the cross correlation of the input and output samples

results in the discrete time system impulse response. From here,

the measured impulse response can be used to derive a suitable

model of the power converter for use in an indirect adaptive or

self-designing controller 1141. In addition, the response can be

converted to the frequency domain for graphical visualization

of the control to output transfer function by applying the

discrete Fourier transform (DFT)

RYY(m)= h(m)

4i)

-1XOR

M = L2;.

.p

9

(6)

H p - o I= U Y

k(1) 4 2 ) 143)

h(P

'..

- 1)

u(p)

1

v(oj

H p - m-[h(p;2)]

j_[

40)

yjl)

v(p-1)

which can be implemented directly in hardware, but require

approximately p z additions, where p = 2" - 1, for an n-bit

PRl3S sequence. While this is possible, it may not be practical

in many applications. The complexity of (8) can be reduced

significantly by exploiting symmetry properties and

manipulating the matrix to leverage existing fast transform

algorithms. We show here how the fast WHT algorithm [ l l , 121

can be used to realize (8) in a parallel structure with only

2" . n total additions.

The characteristics of thc matrix U in (8) must first be

related to a Hadamard matrix W so that the fast WHT can be

utilized. This requires defining a modified matrix with

normalized PRBS data (recall that each PRBS input u(m) has

only two possible values), adding an additional row and

column so that the square matrix has an even order of (p+l),

and adding a zero to each of thc vectors so that (8) becomes

"

*

Hp-m= - U . Y

>

1

r I I

1

1

-1

1

i(l) ti(2)

,.

:

.*.

1

t1 + I

i(p)

+1, for

..

i(p) ;[I)

'.'

+I +1

t1 -1 + I -1

t 1 t l - 1 -1

+ 1 -1 -1 + I

w . x = t1 + I + I tl

+ I -1 + I - 1

+ I + I -1 - 1

-t 1 - 1 -1 t l

-

U

=-e

qp-I)

0

0

+I

+I

t 1 -1

+I +I

t l -I

-1 -1

+I

+l--x(l)+1 -1 x(2)

-1

-I

+I

-1 x(5)

+1 4 6 )

t l 47)

-1

-1

-1

-1

-I

+I

-1

+I

tl - 1

-1

t l

43)

44)

-

~(8)

_L

With the system in the form of (9),it can be shown that

fi.fiT

&.&(p+I).I,

(10)

where I is the identity matrix and 6' represents the transpose

matrix of . By definition, the Walsh-Hadamard matrix W

also has the property as follows [ 1 1 , 121

w.w'T = w ' . w = ( p + l ) . l ,

(1 1)

which implies that the fi and W matrices are equivalent and

that there exist two permutation matrices such that

ri = PL.w .P,,

(1 2)

where PL and Ps are @+l).(p+l) permutation matrices

describing the respective vector orderings. Note that PL and Ps

depend only on the input M-sequence, which is known for a

given n-bit PRES [IZ]. The key result of (12) is that we can

now write (9) as

*

"

Hp-m= -U.Y = -Pi.,U'. Ps . I 9

Figure 3. (a) The matrix form and (b) the butterfly structure of an 8point WHT (3-bit) processing block. where ~ ( mrepresents

)

the output

data from performing a WHTB on the input datar(ni).

cycles for computation) [ 131. To illustrate the trade-off, we

consider three options: parallel, series, and parallellseries

combinations, in the context of a IO-bit WHT example with 8bit wide data (i.e. identification using a 10-bit PRBS, 8-bit

output voltage sensing). A fully parallel solution is based on a

direct hardware realization of a butterfly structure similar to

Fig. 3(b) with 10 butterfly columns (vs. 3 columns in Fig. 3@))

and 1,024 input and output points. Such a WHT1024 structure

(a 1,024-point WHT processing engine) requires 10,240 twoinput 8-bit adders and 2,048 8-bit data registers to store the

input data and output results. The reorder matrices PL and Ps

can be hard wired if the numbcr of bits (n=lO) in the PRBS are

fixed. The total computation time is only limited by logic

delays through the asynchronous hardware, which could be on

the order of nanoseconds.

A direct series solution performs only one addition per clock

cycle, as shown in the flow chart of Fig. 4. The only hardware

requirements are the ability to perform two-input addition and

access and write between two data registers based on preset

address registers (to sequence through the butterfly structure

and perform PL and Ps operations). One approach to manage

the data is to precompute and store the memory locations of

the two inputs for each addition. Since there are 2" . total

additions, 2"" .n address registers are required. For the 1 0-bit

WHT example, 20,480 10-bit address registers are required.

(13)

which shows that the impulse response (normalized and in

reverse order) can be computed using the fast WHT algorithm

by:

1) Reordering the sampled data f according to Ps;

2) Performing the WHT algorithm on the reordered data;

3) Reordering the transformed data according to Pi.

The fast WHT algorithm can be calculated in a butterfly

structure much like the DFT, as shown in Fig. 3 for an 8-point

WHT. The butterfly structure requires only addition and

subtraction (no multiplication), requiring a total of only 2" n

operations. In addition, the parallel structure allows direct

trade-off between hardware area and computational speed

requirements. The 8-point WHT example of Fig. 3 would

apply to identification with a 3-bit PRBS, requiring only 24

additions. A more realistic 10-bit PRBS example is discussed

to explain the trade-off between the number of hardware

adders and the total clock periods to complete the calculation

in the following section.

I

Iv.

HARDWARE IMPLEMENTATION CONSIDERATIONS

The butterfly structure of the fast WHT provides a degree of

freedom for algorithm implementation based on the trade-off

between hardware area and calculation speed (required clock

59

one compromise for the IO-bit WHT example is to split the

structure into two columns with a 5-bit WHT processing

engine (WHT32). This solution requires 64 operations of the

WHT32' structure (32 for each column). The number of clock

cycles required depends on the number of instructions needed

to sequence sets of 32 data values into and out of the structure

for each operation, which could vary between 2 and 64

depending on how memory pointers are used in the controller.

For example, if 6 instructions are required for each operation

of the WHT32 structure, the identification algorithm would

complete in 384 dock cycles, or -20 p using a 20 MHz clock,

requiring less than 6 kBytes total memory.

The three methods are compared in Table I to illustrate the

direct trade-off between hardware adders, memory and time

when implementing the proposed identification algorithm.

While hardware acceleration can be used to significantly

reduce time and memory requirements, it appears that a direct

series solution would be suitable for most applications using

the lowest cost micro-controllers available today or a small

portion of a larger system controller.

Save sensed data in Reg-1

+

Reorder data from Reg-1 to R e g 2

based on Pr

+

Initialize: out = i =j = I, in = 2

i

Select data pair from Reg-in

based on butterfly

4

]Add data & stack result into Reg-out]

TABLEI

Figure 4. Series implementalion of the fast WHT algorithm for an n-bit

WHT, resulting in a butterfly structure with 2" rows and n columns.

Registers Reg-I and Reg-2 have 2" positions each for altemately

staring input, intermediate, and output data.

Only two 8-bit wide, 2" long data registers are required to act

alternately as inputs and outputs while processing the butterfly

structure. For the 10-bit WHT example, the total storage

requirement for data and address registers is still less than

30 Kbytes. The total number of clock cycles depends on the

number of instructions required to perform a two-input

addition (including selecting input data, performing the

addition, and storing the result). If y is the number of

instructions required per addition for a given controller, then

the total instructions required to realize the series WHT

algorithm of Fig. 4 is given by

#hSI

= 2" ' n . y + 4 . n

+2 4 ,

(14)

where y can range from 2 to 8 depending on the controller

instruction set. For a typical value of y = 6 for a low-cost

micro-contrrollcr and the 10-bit WHT example, #inst = 63,528.

Even in a low-cost 20 MHz simple instruction set microcontroller, the series solution requires only -3 ms for

computation and -30 kBytes memory storage.

A final solution is to use hardware acceleration for a

combined series and parallel realization. Hardware acceleration

is achieved by implementing any subsection of the n-bit WHT

butterfly (similar to Fig. 3(b)) directly in hardware, then

sequencing data into and out of the WHT processing engine in

a manner similar to Fig. 4. The total number of required

additions is still given by 2" .n , which can be realized using

any combination of hardware and clock cycles. For example,

registers

1

I

I

I

Parallel

v.

10,240

1

2,048

EXPERIMENTAL SYSTEM:

1

1

1

1

1

I

0

I

I

FORWARD

CONVERTER WITH

DIGITAL

CONTROL

The digitally controlled forward converter shown in Fig. 5

was constructed and used to experimentally verify the

proposed system identification method. The input voltage is

Yg = SO V and the output voltage is V = 15 V. The output filter

inductor L is 100 pH, and the output filter capacitor is

C = 330 pF. The converter operates at the nominal load of 6 A.

The switching frequency isfs = 100 kHz. The turns-ratio of the

transformer is 1:l:l. The input filter parameters are

Lf = 1.9 mH and C, = 66 pF.

The digital controller was implemented using a Xilinx

Virtex-I1 FPGA. The FPGA-based controller includes a IO-bit

digital pulse-width modular (DPWM), a PRBS generator, and a

data collection and identification processing unit. The

converter output voltage, scaled by a 1O:l resistive voltage

divider, is sampled by an AID converter (TI-THS1230, only

used X-bits). The sampling rate equals the switching frequency.

The entire system was operated to demonstrate closed-loop

operation with on-line identification of the control to output

60

experimental digital signals of the PRBS and output voltage

disturbance are illustrated in Fig. 6. It is seen that this

operation does not disturb the normal operation of the

converter.

Figure 7 shows the experimental result - the impulse

response of the fonvard converter with an undamped input

filter. The measured impulse response was then converted to

the frequency domain using the DFT for visualization and

comparison with analog frequency measurements. Figure 8

compares the magnitude and phase responses obtained by the

online identification method (dotted line) and by the network

analyzer measurement (solid line) under the same operating

conditions. It is seen that the matching between the responses

is quite good in a wide range of frequencies, including the

sharp dynamics of the undamped input filter.

Figure S. Digitally controlled fonvard converter: V, = 50 V, V,,,= 15 V,

luu,

5 6 A, I : 1: 1 transformcr, L = IO0 pH, C 330 pF, X = 100 kHz. The

digital controller IS implemented on a Xiiinx Virkx-I1 FPGA. An 8-bit A/D

is used and sampled at the converter switching frequency.

Vi. CONCLUSIONS

5

We have presented a practical approach for on-line

identification of power converter dynamic responses using

low-cost digital hardware. These results provide the first step

towards adaptive power delivery in electronic systems where

self-controller design techniques may utilize the identification

results to update control parameters for stability management

or to provide information to a system controller. In addition,

the results can be used directly for simple off-line analysis and

design of digital controllers using only the controller hardware

itself. Our approach is based on operating the converter openloop for a brief interval (tens of ms) for PRBS injection, output

sampling, and identification processing. The identification

processing is performed using the fast WHT algorithm, which

allows parallel processing with only 2" n total additions (no

multiplication) for an n-bit PRBS. It is shown that the

algorithm can be realized using a series algorithm suitable for

any low-cost micro-controller, with computation times less

than 3 ms (20 MHz clock) and requiring less than 30 kBytes of

memory. Experimental results were presented for a digitally

controlled 50-to-15 V forward converter operating at 100 kHz

using an FPGA-based digital controller, demonstrating

successful control to output dynamic response identification.

transfer function of the experimental forward converter. One

period 10-bit maximum length PRBS was generated by the

FPGA and injected to the digital duty cycle command. The

total data length is p = 2'O-l = 1023. The PRBS frcquencyfo

equals the switching frequencyf;., which means that the process

of collecting data lasts piJ; = 10 ms. This time is selccted

sufficiently long to capture the complete impulse response of

the converter. The corresponding frequency resolution is

100 Hz, which can be compared to the resolution

bandwidth setting in a standard analog measurement of

converter transfer functions using a network analyzer.

The 10-bit PRBS generator was implemented using a shift

register as shown in Fig. 2, where the outputs u(i) arc input to

the DPWM to create stcp changes in the duty cycle. The

steady-state duty cycle is 0.3 and the PRBS magnitude is

e = 0.024 (i.e. +I- 1% changc in duty cycle). The additional

output voltage ripple caused by the PRBS perturbation is about

*0.5 V, or about *3% of thc DC output voltage (again, for only

approximatcly a 10 ms identification interval). The

0.04 I

1

'4

-0.04

a

i

0.002

0.W4

0.006

0.008

0.01

O8/

OR:

0.w32

0.008

t

i

n

-0 2

I

0.M4

0.w36

h e (second)

i

7v

a0 d2 .

0

a

0.01

-04'

O

1

2

3

second ( 5 ]

I

5

4

10.'

Figure 7 . Measured impulse response of the forward converter

based on experimental dola and reatization of the proposed WHT

based identification algorithm.

Ftgure 6.

Experimentally injecred PRBS (top) and resulting

disturbance of the output voltage (botlom), bascd on samples captured

and stored on the FPGA during operalion.

61

Frequency

D. Maksimovic, R. Zane, R. Erickson. "Impact of digital control in power

electronics," invited paper to be presented at the IEEE I~i/erna/iunul

Symposium on Power Semicanducrur Devices & ICs, Kirakyushu, Japan,

May 2004, pp. 13-22.

L. Ljung, S j ~ t e m1den~r;licufion:theoryJbr the user, znded, Prentice- Hall,

N.J., 1999.

G. F. Franklin, J. D. Powel\ and M . Workman, Digird Cunlral of

Dywnric Systems, 3rd Edition. Addison-Wesley, 1997.

B. Iohansson and M. Lenells, "Possibilities of obtaining small-signal

models of DC-to-DC power convertcrs by means of system

identification," Telecommunications Energy Conference, INTELEC 2000,

pp. 65-75.

F. Huynh and E. H. Cho, "Empirical small-signal modeling of switching

conveflers using PSpice," in Proc. IEEE Power Electronics Speciuhts

Cotderence, 1995, pp. 801-808.

D.Maksimovic, "Computer-aided small-ssgnal analysis based on impulse

response of DUDC switching Power Converters," IEEE Tronsuc/iortson

Power Elecrronics, voI. 15, no. 6, pp. 1183-1191,Nov. 2000.

E. Mao, R. Zane, D. Maksimovic, "A Modified Cross-Correlation

Method for System Identification of Power Converters with Digital

Control," in Proc. lEEE Power Eleciroaics Speciuiisrs Conference, Jun.

2004, pp. 1728-3733.

[ 101 R. W.Erickson and D.Maksimovic, Fundumentols ofpower Elec!ronics,

2%d, Boston: Kiuwer Academic Publishers, 2001.

[ I I ] M. Cohn, A. Lenipel, "On fast M-sequence transforms", lEEE Tram. blf:

?%POT tT'-23(1977), pp. 135-137.

[I21 Erich E. Sutter, "The fast m-transform: a fast computation of crosscorrelations with binary m-sequence". Socielyjor Industriul orid Applied

Muthemutics 1991, V01.20, h'o.4, pp. 686-694.

[ 131 Alaqeeli A. and Starzyk J . , "Hardware Implementation for Fast

Convolution with a I" Code Using Field Programmable Gate Array,"

Proc. of 33rd Southeuslern Symposium on Sysfeni Theory, Athens, OH,

pp, 197 -201,March200l.

[14] K. Astram, B. Winenmark, Adaprive C o ~ o lZded,

,

Addison Wesley,

NY, 1995.

(H2)

Figure 8. Experimental frequency response of a IO0 kHz, 90 W forward

converter based on the proposed system identification method. Dotted result

(blue) is based on measured data from the digital identification system. The

solid line (red) is measured hy a network analyzer.

REFERENCES

S. 3.Leeb, Editor, Special issue on Digital Contiol, IEEE Trunsucrrons

on Power Electronics, Vol. 18, No. 1, Part 11, pp. 293-504, Jan. 2003

R. Erickson, D.Maksimovic, and R. Zane, "Advancing Digital Control of

Switched-Mode Converters," special presentation session on current

topics in power electronics research, IEEE Applied Power Electronics

ConJerence, February 2004.

62