Chaos receiver - School of Electronic and Communications

advertisement

The investigation of chaos for the purpose of creating a secure

system of receiving data over a link from a chaotic transmitter

by

David Mitchell

This Report is submitted in partial fulfilment of the requirements of the

BACHELOR OF ENGINEERING TECHNOLOGY (DT008) Degree of the

Dublin Institute of Technology

Supervisor: Mr. Paul Tobin, School of Electronic & Communications

Engineering

-1-

The requirement of the project was to simulate and build a secure data

receiver using chaos. However, in order to create a receiver, it was

required that the transmitted signal had to be investigated. This involved

looking at the circuit and how it created and modulated a signal to be

transmitted.

Using SmartDraw, Figure 1 was drawn showing the block diagram of a

communications system using chaos.

Figure 1: Secure Communications Block diagram

The amplitude modulated carrier was modulated by binary data and a

chaotic signal. The generation of the binary data was investigated at the

outset. The binary NRZ data is a Pseudo-Random Binary Sequence (PRBS)

signal generated using a PRBS generator circuit comprising a digital clock,

an 8-Bit SIPO Shift Register, and an exclusive-OR gate in a feedback loop.

-2-

PRBS signal

Figure 2 shows the circuit used to generate a short sequence of data, i.e.

the PRBS signal.

Figure 2: PRBS generator

Figure 3 shows the output observed from the PRBS generator. It can be

seen clearly that the output is indeed a Pseudo-Random Binary Sequence

signal. It must be noted however that this signal repeats every 63ms. The

length of the sequence is determined by:

N=

fc

103

=

= 63 where f is the spacing between the lines of the PRBS

f 15.74

and fc is the frequency of the digital clock.

Figure 3: PRBS data signal

-3-

The next step in creating the chaotically-masked AM signal was to encrypt

the data using a chaotic signal. This was done by adding the PRBS signal

to a chaotic signal which was generated using a nonlinear dynamic system

known as Chua’s circuit, developed by Leon Chua. This circuit is a Chaotic

Lorenz system, capable of producing a chaotic attractor.

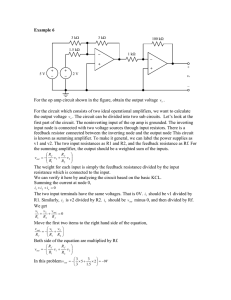

Figure 4 below shows the circuit diagram for the Chua circuit used in the

simulation.

Chua_Out

V

R6

220

11

-15V

V-

20

OUT

C4

3

0.1u

C2

100n

-

+ 4

U1A

OUT

OUT

6

- 11

TL084

+15V

V+

R17

5k

7

9

TL084

V-

R7

Res = 1.74K

0

- 11

8

V-

R8

20k

PARAMETERS:

V+

+

+

C3

4.7n

1

10

V+

-15V

TL084

2

5

4

U1C

+15V

U1B4

R13

+15V

R5

22k

-15V

100

XaxisC2

R15

{Res}

XaxisC1

R14

R9

3.3k

220

R12

2.2k

Figure 4: Chua’s Circuit

To look at the operation of the Chua circuit more closely, the circuit was

looked at and tested as separate parts. The first part in the Chua circuit is

the nonlinear negative resistance (NLR) part. A DC supply was connected

to the NLR circuit, consisting of two operational amplifiers and six

resistors.

-4-

Figure 5: NLR circuit

The nonlinear negative resistance circuit produced the a nonlinear output

shown in Figure 7 when a DC sweep was performed on the circuit by

measuring the resultant input current over a range of voltage values.

Shown in the output are two equilibrium points which shows that the

circuit has a double chaotic attractor, which gives it the double scroll look.

These equilibrium points are at (-1.9, 0, 1.5) and at (1.9, 0 -1.5).

Ga = − R3−1 − R6 −1

Gb = − R3−1 + R4 −1

q=

R5 Esat

R5 + R6

These equations relate to the graph below, Figure 6. They are used to

determine the equilibrium points.

-5-

Figure 6: NLR equilibrium points

Figure 7: NLR output showing equilibrium points

After simulating the nonlinear negative resistance and obtaining an

output, the circuit was built on a breadboard and measurements were

taken to verify the nonlinear negative resistance from a built circuit.

-6-

The table shows the results taken of voltage against current. Using the

equation of V=IR, resistance can be calculated and nonlinear negative

resistance values can be obtained.

8.0V

-4.67mA

7.5V

-4.27mA

-0.5V

0.2mA

7.0V

-3.95mA

-1.0V

0.34mA

6.5V

-3.61mA

-1.5V

0.55mA

6.0V

-3.30mA

-2.0V

0.7mA

5.5V

-2.96mA

-2.5V

0.9mA

5.0V

-2.67mA

-3.0V

1.3mA

4.5V

-2.31mA

-3.5V

1.6mA

4.0V

-1.97mA

-4.0V

2.0mA

3.5V

-1.60mA

-4.5V

2.2mA

3.0V

-1.30mA

-5.0V

2.55mA

2.5V

-0.95mA

-5.5V

2.9mA

2.0V

-0.70mA

-6.0V

3.23mA

1.5V

-0.55mA

-6.5V

3.6mA

1.0V

-0.36mA

-7.0V

3.92mA

0.5V

-0.16mA

-7.5V

4.25mA

0V

0mA

-8.0V

4.6mA

-7-

Using the Sigma Plot package, Figure 7 was obtained using the values

from the table.

Nonlinear Negative Resistance Graph

10

8

6

Voltage (V)

4

2

0

-2

-4

-6

-8

-10

-6

-4

-2

0

Current (mA)

Figure 8: NLR graph

-8-

2

4

6

Figure 8 below shows the conventional linear oscillator used in the Chua

circuit, made up of an inductor L, resistors RL, R, R1 and parallel

capacitors C1 and C2.

The value of inductor L however was fixed and a variable inductance was

desired. To achieve this result, a gyrator was used in place of the

inductor.

Out

V

{Res}

100

XaxisC22

R1

XaxisC12

RL

20

R

C1

100n

C2

4.7n

NLR

2

L1

10mH

1

0

Figure 9: Linear Oscillator circuit

-9-

Shown in Figure 10 below, is the circuit diagram of the gyrator, with key

components RL, R and C, used to replace the inductor L of value 10mH.

The value of inductance was calculated using the equation:

L = RL CR

TL084

13

RL

Zin

11 -15V

V-

20

OUT

C

12

0.1u

14

+ 4 +15V

U1D V+

R

5k

0

Figure 10: Gyrator circuit

Figure 11 is the Fourier Frequency Transform (FFT) of the output signal

from the Chua circuit, and shows a 4 kHz peak, the main resonant

frequency.

Figure 11: Oscillating frequency

- 10 -

Having looked at both the nonlinear negative resistance and the linear

oscillator of the Chua circuit, the full circuit itself was then simulated,

using the same value of components shown in the testing stages. The

resonant frequency of the oscillator remains at 4 kHz.

Shown in Figure 12 is the voltage across variable resistor in the oscillator.

The voltage is measured over a time base. The output was seen to be

chaotic as there was no specific pattern observed. The output is a result of

the signal produced by the oscillator being bifurcated by the nonlinear

negative resistance. The chaotic signal has a continuously changing

amplitude. This confirmed that the desired random output was obtained

and that the signal produced was indeed chaotic.

Figure 12: Chaotic output

- 11 -

Figure 13 below shows the chaotic output from the circuit known as a

Lorenz Attractor. This is produced by plotting on the vertical axis, the

output voltage and changing the horizontal axis from time to the voltage

across the capacitor C2. Such an effect is produced as a result of a

combined oscillating effect and a nonlinear negative resistance. The

attractor is a result of the oscillating output being bifurcated by the

nonlinear negative resistance.

Figure 13: Lorenz Attractor

- 12 -

Shown in Figure 14 is a block diagram of the transmitter circuit. Using a

summing amplifier, the PRBS signal, the Chaotic Signal and a DC offset

are added together. This was the signal used to modulate the carrier

signal and the output of this addition is shown below in Figure 15.

Figure 14: Transmitter

Figure 15: Modulating signal

- 13 -

Now that the modulating signal was obtained, that signal was then used

to modulate an AM carrier with a frequency of 50kHz and an amplitude of

5V, this carrier signal is shown below in Figure 16.

Figure 16: AM carrier

Finally to obtain a signal capable of being transmitted, the modulating

signal was multiplied by the carrier. The DC offset contained in the

modulating signal shifts the signal level up so that the resulting modulated

signal does not contain points at 0V as anything multiplied by 0, gives 0

back out.

- 14 -

Figure 17 below shows the transmitted signal that contains a PRBS signal

encrypted using a chaotic signal.

Figure 17: Modulated transmitter output

The transmitted signal has been looked at through its numerous stages.

This was necessary in order to design a receiver capable of demodulating

the signal and recovering the data.

- 15 -

Chaotic Receiver

Figure 18 shows the block diagram of the chaotic receiver. This receiver

takes in the encrypted, transmitted signal and its output is the recovered

PRBS signal.

Figure 18: Communications Receiver

The first part in the design of the receiver was to rectify the signal. Half

wave rectification was implemented using a single diode. This was done

because the incoming signal is a bipolar signal and a uni-polar signal was

desired. Figure 19 shows the rectifier part of the receiver. The rectifier

only consists of a single diode with a load resistor attached. The diode is

placed in forward bias so that rectified signal is a positive DC signal.

D1

Input

Rectif ied

D1N4148

R9

1k

0

Figure 19: Half wave rectifier

- 16 -

Shown below in Figure 20 is the rectified, positive uni-polar signal. This

signal contains the PRBS signal which is encrypted by the chaotic signal

produced by the Chua circuit.

Figure 20: Rectified signal

The chaotic signal then needed to be subtracted from the rectified signal.

This was done using a difference amplifier which is a subtractor. It

provides an output that is proportional to the difference between its input

voltages.

Shown below in Figure 21 is the rectified signal which will have the chaos

signal also shown below subtracted from it.

- 17 -

Figure 21: Rectified signal and chaotic signal

Figure 22 shows the diagram of the difference amplifier used to subtract

the chaos from the rectified signal. The amplifier must have R1=R2 and

R3=R4 for the amplifier to work properly. The output is then found to be:

Vout =

R3

(V2 −V1 )

R1

0

R4

40k

+15V

4

U12A

R2

rectif ied_in

3

V+

+

100k

OUT

R1

chaos_in

2

100k

- 11

TL084

1

V- -15V

R3

40k

Figure 22: Difference Amplifier

- 18 -

Dif f out

Shown in Figure 23 is the output obtained from the difference amplifier

when the chaos was subtracted from the rectified signal. We can see here

the outline of the PRBS signal.

Figure 23: Difference amplifier output

With the chaos subtracted, a voltage comparator, shown in Figure 24, was

used to compare the input signal voltage level to a fixed DC reference

voltage and output the relationship between them. The fixed DC value

was set to 2Vdc.

0

5Vdc

V23

U4B4

5

V+

+

OUT

6

V22

- 11

TL084

7

V-

2Vdc

0

Figure 24: Voltage Comparator

- 19 -

Figure 25 shows the output of compared relationship between the inputs

of the comparator. As the voltage reference is set to 2Vdc, whenever the

other input goes the above 2V, the output will go high and when it drops

below 2V, the output will go low.

Figure 25: Comparator Output

Figure 26 is the circuit for the summing amplifier used to shift the

comparator output down by 0.5V dc by adding DC voltage to it. This

brought the output closer to 0V.

R33

1k

R30

-15V

TL084

2

1k

R31

11

V-

OUT

1k

3

1

+ 4

U12A V+ +15V

0.5Vdc

V8

0

0

Figure 26: Summing Amplifier

- 20 -

Figure 27 below is the output of the summing amplifier which level shifted

the comparator output down by 0.5V as desired but is inverted as a result

of the way in which a summing amplifier operates. To restore the signal to

a positive state, an inverting op amp configuration was used.

Figure 27: Summing Amplifier output

Shown in Figure 28 is the Inverting op amp configuration used to restore

the output from the summing amplifier to a positive state.

R35

1k

-15V

TL084

6

R34

11

V-

-

1k

OUT

5

7

lev elled

+ 4

U12B V+ +15V

0

Figure 28: Inverting Amplifier

- 21 -

V

The signal from the transmitter had been rectified, the chaotic signal was

subtracted and the voltage comparator was used as a level detector and

then the signal was shifted using a summing amplifier and an inverting

amplifier. Then signal was filtered at two stages and another comparator

was used as a voltage detector. The signal then had to be reduced and

level shifted to recover the PRBS signal.

Figure 29 is a low pass CR filter. This was used to filter the output from

the comparator. The cut-off frequency of this filter is shown below:

fc =

1

1

=

≈ 21.22kHz

3

2π CR 2π (15e )(500e −12 )

R28

lev elled

cr_out

15k

C10

500p

0

Figure 29: Low pass CR filter

To show how the CR filter was designed, the spectrum of the input signal

was looked at in Figure 30.

Figure 30: Spectrum of the levelled signal being input into the CR filter

- 22 -

After the comparator stage, there were many frequencies passing through

the circuit. The spectrum of the signal was looked at and the values

chosen for the components gave the desired break frequency. The output

from the CR filter was to be passed into another comparator.

Figure 31 shows the output from the CR filter with the desired break

frequency implemented.

Figure 31: CR filter output

Figure 32 is the comparator used to compare the difference between the

voltage from the output of the CR filter against a reference voltage of

0.5V. The output of this is shown below.

- 23 -

0

4

V24

5Vdc

12

+

V+

U11D

cr_out

TL084

0.5Vdc

0

-

comp2_out

V-

13

V25

14

11

OUT

0

Figure 32: Comparator

Figure 33 shows the output of compared relationship between the inputs

of the comparator. As the voltage reference is set to 0.5Vdc, whenever

the other input goes the above 0.5V, the output will go high and when it

drops below 0.5V, the output will go low.

5.0V

2.5V

0V

0s

1.00ms

2.00ms

3.00ms

4.00ms

4.46ms

V(COMP2_OUT)

Time

Figure 33: Comparator output

Using another low pass CR filter with the same value components as

before, Figure 34 shows the filtered output from the second comparator.

- 24 -

When the original PRBS signal is compared to the recovered signal, we

can see it is nearly identical.

Figure 34: CR filter output

Finally to match the voltage of the original PRBS signal, a non-inverting op

amp was used to adjust the gain of the filtered signal. Then the signal was

passed through a summing amplifier and an inverting amplifier to shift the

level of the signal and then restore it to a positive state. These stages are

shown below.

Shown in Figure 35 is the non-inverting op amp configuration used to

adjust the gain of the filtered signal to as close to the original PRBS signal

as possible.

- 25 -

+15V

R40

U12D

4

cr_out2

12

V+

+

1k

OUT

13

TL084

- 11

14

gain

V

V- -15V

R38

450

R39

1k

0

Figure 35: Non-inverting op amp circuit

The signal with adjusted gain from the non-inverting amplifier is shown in

Figure 36. This signal was then shifted down by adding DC to it using a

summing amplifier and an inverting amplifier.

Figure 36: Filtered output with increased gain

Figure 37 shows the final part of the receiver consisting of a summing

amplifier and an inverting amplifier used to level shift the signal by adding

DC to it and restoring the signal to a positive state.

- 26 -

Figure 37: Summing amplifier with inverting amplifier

The final output from the receiver is shown in Figure 38. The PRBS signal

was recovered almost exactly as the original signal appears. Using a

series of filters and comparators, level shifting and gain adjustment, the

PRBS was recovered.

Figure 38: Recovered PRBS

- 27 -