A Collector-Up SiGe-HBT for High Frequency Applications

advertisement

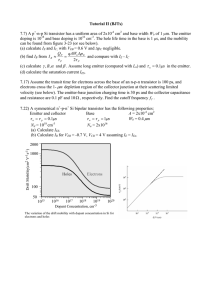

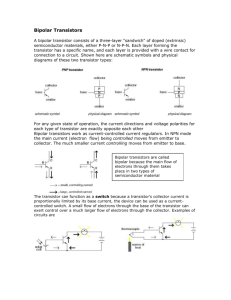

A Collector-Up SiGe-HBT for High Frequency Applications Mojtaba Joodaki1, Hartmut Hillmer2 1 2 Infineon Technologies AG, Campeon 1-12, 81726 Munich, Germany University of Kassel, Dept. of Technological Electronics, Institute of Nanostructure Technologies and Analytics (INA), Heinrich-Plett Street 40, D-34132 Kassel, Germany, Tel: +49 89 234 45912, E-Mail: mojtaba.joodaki@infineon.com Short Abstract— A new method for realization of a collector-up SiGe-HBT on SOI substrate for high frequency applications is introduced and its dc and ac characteristics are predicted using a two dimensional device simulator. The simulation results show considerable improvements in all aspects of dc current gain, fT, fmax, and maximum available gain/maximum stable gain (MSG/MAG) in comparison with a state of the art emitter-up SiGe-HBT with similar doping profile and germanium content. Another advantage of common-emitter collector-up transistor is that the emitter is connected to the ground and the substrate capacitor is shorted. This provides a higher frequency performance for circuit designs. Keywords-SiGe HBTs; RFapplications; collector-up bipolar transistor; RF integrated circuits. I. INTRODUCTION Improvement of the SiGe-HBTs performance for high frequency applications has a very high priority in semiconductor business. Everyday we face new high frequency designs which require low-cost devices with higher frequency performance. For such applications the device of the choice is SiGe-HBT. Since in a bipolar transistor a very low emitter resistance is needed, conventionally it is realized in emitter-up configuration. In this way emitter is highly doped and collector is realized through an arsenic doped n-buried layer, which results in an acceptable collector resistance. These are all achieved at the cost of high collector-base and collectorsubstrate capacitance. Recently, device engineers are interested to implement a low-resistance silicide layer instead of the arsenic n-buried layer, which could provide a much lower resistance [1]. In this case, collector-up transistor can be realized with a low emitter-resistance. On the other hand, in the last decade several genuine approaches for fabrication of emitter-up SiGe-HBT are introduced, which extremely enhanced the performances [2]. Although the methods of realization are different but most of them aimed at achieving two main goals; low-base resistance and a structure free from parasitic homo-junction bipolar transistor at the emitter-base junction. In the proposed fabrication process lateral solid-phase epitaxy of amorphous silicon [3] with a thick in-situ p-doped polysilicon base are used to achieve the above mentioned goals in the collector-up SiGe-HBT. In the next section the new fabrication process is described. Section III covers the simulation results and section IV is the conclusion. II. THE FABRICATION PROCESS At the first step a SOI substrate with silicide strips for the low-resistance emitter contacts should be prepared (Fig. 1a). This is explained in reference [1]. Then an n+ layer for emitter is provided using a phosphor or arsenic implantation. The phosphor implantation gives a lower resistance but a higher diffusion constant of doping, which requires a thicker emitter to have a low doping concentration emitter at the emitter-base junction. This implantation could also be done later in the process, the same as selectively implanted collector (SIC) in the emitter-up structure. But this might induce some defects in the base and collector. In this work the silicon thickness is 250 nm, which is adequate to achieve a thick external base layer and a low doping concentration emitter at the base-emitter junction. In the next step a thin layer of silicon dioxide is thermally formed and patterned and silicon is etched and a 50 to 100 nm thick thermal oxide is made (Fig. 1b). Then at both sides of the transistor two windows are opened to be used as seed for lateral epitaxial overgrowth over oxide process [3] and covered by silicon nitride. Using the lateral epitaxial overgrowth and a CMP the highly p-doped crystalline external base areas are made. After CMP the structure in Fig. 1d is achieved. In this part to have a crystalline silicon layer over the active area of the device for the following epitaxial SiGe base and silicon collector, a 10 to 20 nm thick silicon layer with low doping is deposited. Since the oxide between base and emitter is thinner than 100 nm the silicon layer over it will also be crystalline. After that a 5 nm SiGe emitter-base spacer, 10 nm high concentration boron doped SiGe, and 10 nm SiGe basecollector spacer are epitaxially deposited. A low percentage of carbon concentration should be used with the highly boron doped SiGe to reduce the boron out-diffusion to the emitter. In this part collector epitaxy is made and the structure is etched as shown in Fig. 1e. To hinder any undesired direct contact of base and emitter outside of active area of the transistor and reach the n+-doping for emitter contact, the silicon at the both sides of the structure is etched. A thin silicon dioxide is thermally formed and followed with a thicker low temperature oxide deposition. The openings for emitter and collector contacts are created and using the same phosphor implantation, the n+ areas for emitter and collector are achieved. Fig. 1f shows the final structure. (a) (b) n--Si (c) + n -Si p+-Si or Poly Oxide Silicide (d) SIC Nitride n+-Poly (e) C E B (f) Figure 1. The proposed fabrication process for the collector-up SiGe-HBT. B E III. SIMULATION RESULTS To present the advantages of the collector-up configuration over the emitter-up SiGe-HBT, the 2D device simulator of ATLAS from Silvaco Inc is implemented. The dc and ac simulations are performed for both emitter-up and collector-up transistors with similar material properties and model parameters. The model parameters are adjusted using measured data of a fabricated emitter-up SiGe-HBT (SiGe2RF). For a reasonable comparison all the doping profiles, germanium contents, and geometrical dimensions for both devices are the same. The only differences are that in the collector-up transistor the collector is 75 nm thinner and the SIC is not used and a uniform phosphor doping of 1e17 cm-3 is used instead. It is known that SIC will improve high frequency performance but may degrade the collector-emitter breakdown voltage. Fig. 2 shows the standard emitter-up structure of SiGe-HBT. Both devices have an emitter area of 0.5µm×1µm. Figs. 3 and 4 show the Gummel-plots and dc current gains for both structures, respectively. Since the parasitic pn-junction between mono-emitter and implanted external base has a considerable effect on the base current of emitter-up configuration, the current gain of the collector-up transistor is improved. All the simulations are performed at collector voltage of 1.5 V. 1.0E-02 Ib-Collector up Ic-Collector up 1.0E-04 Ib-SiGe2RF Ib & Ic [A] Ic-SiGe2RF 1.0E-06 1.0E-08 1.0E-10 1.0E-12 0.4 0.6 0.8 1 Vbe [V] Figure 3. Gummel-plots for the collector-up and SiGe2RF (emitter-up) transistors. 1600 Collector up SiGe2RF Current gain 1200 Emitter 800 400 Base Base 0 1.0E-13 1.0E-11 1.0E-09 1.0E-07 1.0E-05 1.0E-03 1.0E-01 Ic [A] Figure 4. Dc common-emitter current gain for the collector-up and SiGe2RF (emitter-up) transistors. SIC Figure 1. The emitter-up n-buried SiGe-HBT layer structure used in the simulations. Figure 2. The emitter-up SiGe-HBT structure used in the simulations. Since SIC is not used in the collector-up configuration a collector-base breakdown voltage of 11.5 V is achieved while 9 V for the emitter-up configuration. But as the corresponding current gain is higher in collector-up configuration the emitterbase breakdown voltages of both structure are equal to 2.5 V. A higher collector-base breakdown voltage is desired in many RF applications. Figs. 5, 6, and 7 depict the MSG at 2 GHz, fT, and fmax for both emitter-up and collector-up variants, respectively. Collector-base capacitor for the both variants is extracted from S-parameters and is 1.55E-14 F for the emitterup transistor and 6.9E-15 F for the collector-up transistor. This means a reduction of more than 55%. Since collector capacitor is effectively reduced and the effect of the parasitic pn-junction in low doped emitter is reduced in the collector-up structure, the MSG, fT, and fmax all are improved by 36%, 23%, and 84%, respectively. Large improvement of fmax results from improvement of fT and reduction of collector-base capacitor and base resistance. 40 MSG at 2 GHz [dB] 30 SiGe2RF Collector up 20 10 0 0.0E+00 7.0E-04 1.4E-03 2.1E-03 Ic [A] Figure 5. MSG at 2 GHz for the collector-up and SiGe2RF (emitter-up) transistors. 1.0E+11 fT [Hz] 8.0E+10 6.0E+10 SiGe2RF Collector up 4.0E+10 2.0E+10 0.0E+00 0.0E+0 2.0E0 04 4.0E04 6.0E04 8.0E04 1.0E03 1.2E03 1.4E03 1.6E03 1.8E03 Ic [A] Figure 6. Transit frequency (fT) for the collector-up and SiGe2RF(emitter-up) transistors. 2.5E+11 fmax [Hz] 2.0E+11 1.5E+11 SiGe2RF Collector up 1.0E+11 5.0E+10 0.0E+00 0.0E+00 3.0E-04 6.0E-04 9.0E-04 1.2E-03 1.5E-03 1.8E-03 Ic [A] Figure 7. Maximum oscillation frequency (fmax) for the collector-up and SiGe2RF(emitter-up) transistors. IV. CONCLUSION In this paper a new fabrication process is introduced for realisation of the collector-up SiGe-HBT. Using a two dimensional device simulator the dc and ac characteristics of the transistor are predicted and compared to those of a standard emitter-up SiGe-HBT (SiGe2RF) with similar doping, emitter size, and Ge concentration in the base. In the collector-up structure by shorting the substrate and emitter to the ground the effect of the substrate capacitor is cancelled out and the collector-base junction has a lower capacitance. In addition the effect of the parasitic bipolar transistor is minimised and collector-base breakdown voltage is improved. The simulation results show great improvements in fT, fmax, and MSG for the collector-up structure while the collector-emitter breakdown voltage is almost the same for both variant. REFERENCES [1] [2] [3] R. Wilson, C. Quinn, B. Mcdonnell, S. Blackstone, and K. Yallup, “Bonded and trenched SOI with buried silicide layer,” ESC Symp. on Semicond. Wafer Bonding, Reno, May 1995. J.-S. Rieh, B. Jagannathan, H. Chen, K. T. Schonenberg, D. Angell, A. Chinthakindi, J. Florkey, F. Golan, D. Greenberg, S. J. Jeng, M. Khater, F. Pagette, C. Schnabel, P. Smith, A. Stricker, K. Vaed, R. Volant, D. Ahlgren, G. Freeman, K. Stein, and S. Subbanna, “SiGe HBTs with cutoff frequency of 350 GHz,” IEEE IEDM, pp. 771-774, 2002. Y. Morimoto, S. Nakanishi, N. Oda, T. Yamaji, H. Matuda, H. Ogata, and K. Yoneda, “Influence of the existence of an underlying SiO2 layer on the lateral solid-phase epitaxy of amorphous silicon”, J. Electrochem. Soc. vol 141, No. 1, January 1994.