EDN Access--08.15.97 Buck regulator generates flexible VTT for PECL

advertisement

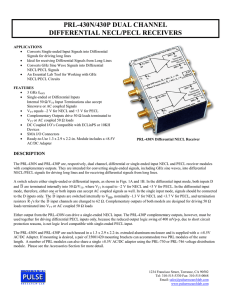

EDN Access--08.15.97 Buck regulator generates flexible VTT for PECL EDN Staff - August 15, 1997 August 15, 1997 Buck regulator generates flexible VTTfor PECL Bruce D Moore, Maxim Integrated Products, Sunnyvale, CA The positive emitter-coupled logic (PECL) in most high-speed clockdistribution and -recovery circuits requires a termination voltage, VTT, that imposes special requirements on the VTT supply. First, the typical switching thresholds for PECL must refer to VDD instead of ground (VOL=VDD-1.32V+400 mV, and VOH=VDD-1.32-400 mV). The level of VTT, typically at VDD-2V, is slightly below VOL to ensure that the open-emitter outputs always source current (Figure 1a). Unlike most power-supply voltages, therefore, the supply must regulate VTT with respect to VDD instead of ground. A second possible requirement for the VTT supply is that it must be able to both source and sink current. This requirement does not apply for standard PECL, but for PECL that employs current-source outputs, as in some ASIC standard-cell libraries (Figure 1b). The high and low logic levels cause a typical current-source PECL output (terminated by 50 ohms) to switch between 8 and -8 mA, producing signal levels of VTT+400 mV and VTT-400 mV. For compatibility with standard PECL receivers, this output must have a termination voltage that is slightly higher than the standard VTT, such as VDD-1.32V. For differential outputs centered at 1.32V, the termination current should cancel and produce a net VTT current of zero. Device mismatches and skew, however, usually cause VTT to source or sink some current. In contrast, VTT for standard PECL must always sink current. Large systems that draw 1 or 2A of VTT current require a serious power-supply design. (Smaller systems can use a power op amp as the VTT source.) The dc/dc converter of Figure 2, for example, generates a regulated VTT output that you can adjust to VDD-2V or VDD-1.32V, thereby accommodating either standard or ASIC-type PECL. To change the range from VDD-2V to VDD-1.32V, simply change R1 from 6.04 kilo ohms to 560 ohms. The design accomplishes the regulation with respect to VDD rather than ground by using an op-amp integrator, IC2, which drives the feedback input of IC1, and a low-voltage reference diode, IC3 (a 1.25V version of the popular 2.5V TL431), whose cathode connects to VDD. To enable the output to source and sink, a synchronous rectifier, Q2, and other circuitry allow the inductor current to reverse direction. Most controller ICs in a high-efficiency power supply don't allow such reversals, because reversals allow excessive noload supply current. However, in this circuit, IC1 has logic-control input (SKIP), which, when high, disables the internal currentlimiting circuit that prevents the reversal of inductor current. SKIP was intended to suppress ringing in noise-sensitive wireless applications for switch-mode converters operating in the discontinuous-conduction mode. Here, SKIP allows current to flow from the output back into the inductor and through Q2 to ground. This synchronous-switch technique has a limitation: When the net output current is negative (sinking), VDD must also sink current. The buck topology then works in reverse and becomes a boost topology. Excess current flowing into the 5V supply is not necessarily a problem, provided that other 5V loads in the system can accept the current. The efficiency of the circuit is greater than 92% at 1A and greater than 85% at 0.1A. If you try to accomplish the same design with a power op amp, efficiency would be about 60% relatively independent of load. When sinking current, the circuit acts as a boost-topology converter with about 85% efficiency. In this case, any power from the output goes back into the 5V source, albeit with some friction losses. (DI #2070) Figure 1 The standard PECL interface (a) requires a termination voltage, VTT, that allows the open-emitter outputs to always source current. However, some ASIC standard-cell PECL interfaces (b) require VTT that can both source and sink current. Figure 2 To enable the output to both source and sink current, Q2, IC1's SKIP input, and associated circuitry allow the inductor current to reverse direction. | EDN Access | Feedback | Table of Contents | Copyright c 1997 EDN Magazine, EDN Access . EDN is a registered trademark of Reed Properties Inc, used under license. EDN is published by Cahners Publishing Company , a unit of Reed Elsevier Inc.