A New High Breakdown Voltage Lateral Schottky Collector Bipolar

advertisement

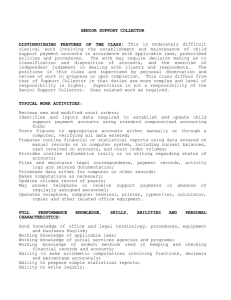

2496 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 52, NO. 11, NOVEMBER 2005 A New High Breakdown Voltage Lateral Schottky Collector Bipolar Transistor on SOI: Design and Analysis M. Jagadesh Kumar, Senior Member, IEEE, and Sukhendu Deb Roy Abstract—Using two-dimensional process and device simulation, we present for the first time, a new high breakdown voltage twozone base extended buried oxide (BOX) lateral Schottky Collector Bipolar Transistor (SCBT) on silicon-on-insulator with a breakdown voltage as high as 12 times that of the conventional lateral Schottky collector bipolar transistor. We have explained the new design features of the proposed Schottky collector structure and the reasons for its significantly improved breakdown performance. The proposed structure is expected to be suitable in the design of the new generation scaled high voltage Schottky collector bipolar transistors for low power high speed analog applications. Index Terms—Breakdown voltage, buried oxide (BOX), lateral Schottky collector bipolar transistor (SCBT), silicon-on-insulator (SOI), two-zone base. I. INTRODUCTION T HE concept of Schottky Barrier Collector Transistor (SBCT) has been introduced by May [2] to minimize the collector storage time, suppress the minority carrier reverse injection into the base and reduce collector series resistance. Since then the SBCTs have been a subject of intense investigations for their practical applications in high speed switching and nonsaturating logic circuits or in class-D amplifier stages, and a number of [3]–[18] show adequate treatment on their practical design and implementation both for small and large dimension devices. However, all these designs were based on vertical current concept and did not become popular due to the difficulties in integrating them in a standard CMOS process. The other class of Schottky collector bipolar transistors recently proposed by Kumar et al. [19]–[24] is the lateral Schottky collector bipolar transistor (SCBT) on SOI technology. Their simulation results show that lateral SCBTs have promising applications in high speed analog and mixed signal circuit designs and especially in nonsaturating VLSI logic circuits on BiCMOS technology. However, a major drawback of either vertical or lateral Schottky collector bipolar transistors is their extremely low collector breakdown voltage V). This is because of the presence of an accumulated or depleted space-charge region over a very small region [1], which produces a high electric field at the Schottky collector–base interface. In addition, due to the Manuscript received January 28, 2005; revised July 13, 2005. The review of this paper was arranged by Editor M. A. Shibib. The authors are with the Department of Electrical Engineering, Indian Institute of Technology, New Delhi 110 016, India (e-mail: mamidala@ieee.org). Digital Object Identifier 10.1109/TED.2005.857171 Fig. 1. (a) Schematic cross section of the conventional SCBT, (b) two-zone base SCBT (TSCBT), and (c) two-zone base extended BOX SCBT (TESCBT). field-induced barrier lowering effect and the image force [1], nonsaturating reverse leakage current becomes large to cause their premature breakdown. In this paper, using two-dimensional (2-D) simulation, we demonstrate for the first time that by applying a combination of a two-zone base region and an extended buried oxide (BOX) in a lateral Schottky collector bipolar transistor, the collector breakdown voltage can be enhanced by as large as 12 times that of a conventional lateral Schottky collector bipolar transistor. The proposed two-zone base region has a high doped base at the emitter side and a low doped base at the collector Schottky metal side. The doping level of the low doped base is chosen such that in the absence of an externally applied bias it gets completely depleted. This reduces the electric field at the metal–base interface, thereby improving the breakdown voltage. However, breakdown voltage is still limited by the high electric field at the 0018-9383/$20.00 © 2005 IEEE KUMAR AND ROY: NEW HIGH BREAKDOWN VOLTAGE LATERAL SCHOTTKY COLLECTOR BT 2497 TABLE I DEVICE PARAMETERS Fig. 2. Doping profiles of the TSCBT compared with that of the conventional SCBT. TABLE II SIMULATION PARAMETERS Fig. 3. Gummel plots of the TESCBT compared with that of the conventional SCBT. Fig. 5. Common–emitter I–V characteristics of the TESCBT compared with that of the TSCBT and the conventional SCBT: t = 0:2 m and = 1:8 m. t In the following sections, we have explained the proposed device structure, its possible fabrication procedure, and the reasons for its significantly improved breakdown performance. Fig. 4. Collector current versus current gain of the TESCBT compared with that of the conventional SCBT. II. DEVICE STRUCTURE AND SIMULATION PARAMETERS Schottky metal–BOX interface. This shortcoming is eliminated by using an extended BOX region below the two-zone base to support the high electric field resulting in a significant improvement in the breakdown voltage. Fig. 1 shows the schematic cross section of a conventional SCBT, a two-zone base SCBT (TSCBT), and a two-zone base extended BOX SCBT (TESCBT) structure. The process steps for realizing the conventional SCBT in the 2-D process simulator ATHENA [25] are similar to those proposed in [19]. In 2498 Fig. 6. (a) Potential contours and (b) lateral electric field distribution for the conventional SCBT. the case of a TSCBT structure, a two-step base implantation process can be used using an additional mask to generate the high doped and low doped two-zone base region. For obtaining the TESCBT, the process steps are exactly the same as above except that the starting wafer has the extended BOX, which is obtained on the handling wafer prior to the wafer bonding or layer transfer process. For all the structures, an optimized 1.0- m-thick field oxide over the two-zone base is used to facilitate spreading of electric field lines. In addition, the collector Schottky metal electrode on the field oxide is extended from the collector–base interface and optimized to act as the metal plate field termination. The doping profiles for the conventional and TSCBT structures obtained by ATHENA using the above process are shown in Fig. 2. The doping profile for the TESCBT is exactly same as that of the TSCBT. The above structures created in the process simulator ATHENA are imported to the 2-D device simulator ATLAS [26] for evaluating their electrical characteristics. The various models activated in the simulations are Fermi–Dirac distribution for carrier statistics, Klaassens unified mobility model for dopant-dependent low-field mobility, analytical field dependent mobility for high electric field, Slotboom model for bandgap narrowing, Selberherrs ionization rate model for impact ionization and Shockley–Read–Hall (SRH) and Klaassen Auger IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 52, NO. 11, NOVEMBER 2005 Fig. 7. (a) Potential contours and (b) lateral electric field distribution for the TSCBT: SME length = 1:0 m. recombination models for minority carrier recombination lifetime. The SRH recombination lifetime for silicon is chosen to cm and for be 2.0 s for a carrier concentration of all other concentrations recombination lifetimes are calculated using Roulstons equation [27]. For simulating the Schottky junction properties, standard thermionic emission model is invoked and the image force barrier lowering effect parameter is included. For a better comparison of the breakdown voltage, the common emitter peak current gain of all the three structures is chosen to be identical ( 30) by an appropriate choice of the emitter and base dopings as shown in Fig. 2. For each is structure, the collector–emitter breakdown voltage (BV calculated at the collector current of m . The Gummel plots and current gain curves for the above structures are compared at V in Figs. 3 and 4, respectively. The device dimensions and appropriate model parameters used in our simulation are given in Tables I and II. III. RESULTS AND DISCUSSION The output characteristics of the TSCBT and TESCBT are compared with that of the conventional lateral SCBT in Fig. 5. Clearly, in the case of TSCBT, the breakdown voltage increases to 13.2 V when compared with that of the conventional SCBT whose breakdown voltage is 2.3 V. This is an improvement KUMAR AND ROY: NEW HIGH BREAKDOWN VOLTAGE LATERAL SCHOTTKY COLLECTOR BT Fig. 8. (a) Potential contours and (b) lateral electric field distribution for the = 1:8 m and SME length = 1:5 m. TESCBT: t of about 5.7 times. However, the TESCBT exhibits a breakdown voltage of 28.4 V, which is about 12 times that of the conventional SCBT. This is a remarkable improvement in the breakdown voltage of a Schottky collector bipolar transistor not reported so far in literature. This enhancement in breakdown voltage can be understood by observing the potential contours and the corresponding electric field line crowding for all the three structures as shown in Figs. 6–8. In the case of the conventional SCBT, we notice from Fig. 6(a) that the potential contours crowd at the base–metal junction. This makes the electric field reach its critical value at the junction of this device at a lower collector–base reverse bias as shown in Fig. 6(b) resulting in an early breakdown voltage at 2.3 V. In the case of TSCBT, we observe from Fig. 7(a) that the potential counters are more uniformly distributed at the collector base–metal junction because of the lightly doped part of the two-base region. As a result, the critical electric field is reached at a higher collector–base reverse bias as shown in Fig. 7(b) leading to a higher breakdown voltage of 13.2 V. However, the potential contours of the TSCBT are still crowded in the BOX under the base–metal junction. If these potential contours can be more uniformly distributed, one would expect a further improvement in the collector breakdown voltage of the SCBT. This is achieved in the TESCBT structure in which the BOX thickness is extended under the low doped base and metal collector regions. It is clear from Fig. 8(a) that the potential 2499 Fig. 9. (a) Breakdown voltage versus SME length on the field oxide for the TSCBT and TESCBT structures: t = 0:2 m and t = 1:8 m. (b) Breakdown voltage versus extended BOX thickness to show the effect of extended BOX thickness on the breakdown voltage of the TESCBT: SME length = 1:5 m. contours are now more uniformly distributed not only at the base–metal junction but also in the oxide regions. This makes it possible to apply a large collector–base reverse bias before the critical electric field is reached as shown in Fig. 8(b) resulting in a breakdown voltage of about 28.4 V for the TESCBT. This improvement in breakdown voltage is more than two times that of the TSCBT and as high as 12 times that of the conventional lateral SCBT. Fig. 9(a) shows the effect of Schottky metal extension (SME) on the breakdown voltages of the TSCBT and TESCBT. We observe that the SME distributes the peak electric field away from the Schottky metal-base interface. However, it is not as effective as the low doped depleted base region and the contribution to the improvement in the breakdown voltage by using SME alone is about 5% and 12%, respectively, for the TSCBT and TESCBT structures. Fig. 9(b) shows the effect of increasing the thickness of the extended BOX on the breakdown voltage. It shows that the breakdown voltage increases with the increase in extended BOX thickness and finally saturates to a constant value when the BOX thickness is about 1.8 m below the bottom silicon-BOX interface. This is expected when both the components of the electric field are responsible in the avalanche process and hence increasing the extended BOX thickness beyond a certain thickness does not improve the breakdown voltage. 2500 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 52, NO. 11, NOVEMBER 2005 IV. CONCLUSION Based on 2-D numerical studies, we have demonstrated the highest collector breakdown voltage for a Schottky collector bipolar transistor not reported so far in literature. Our proposed structure has a low doped base at the collector side and a high doped base at the emitter side and also an extended buried oxide below the Schottky metal-base region. We have demonstrated that the above design allows significant improvement in collector breakdown voltage, which is about 12 times higher when compared with the conventional thin film lateral schottky collector bipolar transistor on silicon-on-insulator (SOI). We have explained the improvement in breakdown voltage as due to the spreading of the electric field away from the Schottky collector metal-base interface into the depleted low doped base and suppression of vertical breakdown at the Schottky metal-buried oxide interface by the extended buried oxide. Our proposed structure is expected to have wide applications in the design of high voltage, high speed Schottky collector lateral bipolar transistors on SOI for the new generation analog circuits such as the low power RF amplifiers, current and voltage precision circuits, bandgap reference circuits [28]–[34]. REFERENCES [1] S. M. Sze, Physics of the Semiconductor Devices, 2nd ed. New York: Wiley, 1981. [2] G. A. May, “The Schottky-barrier-collector transistor,” Solid State Electron., vol. 11, no. 6, pp. 613–619, 1968. [3] S. C. Blackstone and R. P. Mertens, “Schottky collector I/SUP 2/L,” IEEE J. Solid-State Circuits, vol. SSC-12, no. 3, pp. 270–275, Mar. 1977. [4] F. W. Hewlett, “A compact efficient Schottky collector transistor switch,” IEEE J. Solid-State Circuits, vol. SSC-14, no. 5, pp. 801–806, May 1979. [5] S. Hau, L. J. Cornell, W. Eccleston, and J. S. Roberts, “Emitter-down, Schottky collector HJBT for very fast, high-density logic applications,” Electron. Lett., vol. 24, no. 15, pp. 971–973, 1988. [6] S. Hall, L. J. Cornell, W. Eccleston, and J. S. Roberts, “Direct coupled logic using an integrated, emitter-down, Schottky collector, heterojunction bipolar transistor with a MESFET load,” in Proc. Inst. Elect. Eng. Colloquium Heterojunction Quantum Well Devices: Physics, Engineering Applications, 1988, pp. 19/1–19/3. [7] S. Akbar, N. Anantha, C. Hsieh, and J. Walsh, “Method of fabrication of Schottky bipolar transistor,” IBM Technol. Disclosure Bull., vol. 33, p. 11, Apr. 1991. [8] S. Akbar, S. Ratanaphanyarat, J. B. Kuang, S. F. Chu, and C. M. Hsieh, “Schottky-collector vertical PNM bipolar transistor,” Electron. Lett., vol. 28, no. 1, pp. 86–87, 1992. [9] J. L. Pelouard, N. Matine, F. Pardo, D. Sachelarie, and J. L. Benchimol, “Fully self-aligned InP/InGaAs heterojunction bipolar transistors grown by chemical beam epitaxy with a Schottky collector,” in Proc. Int. Conf. Indium Phosphide Related Materials, 1993, pp. 393–396. [10] O. Nur and M. Willander, “Switching characteristics of pSi=nSi Ge =CoSi Schottky collector HBT,” Microelectron. J., vol. 24, no. 7, pp. 823–830, 1993. , “The high-speed performance of p Si=n Si Ge =CoSi [11] Schottky collector HBTs,” Microelectron. J., vol. 25, no. 6, pp. 399–406, 1994. [12] U. Bhattacharya, M. J. Mondry, G. Hurtz, I. H. Tan, R. Pullela, M. Reddy, J. Guthrie, M. J. W. Rodwell, and J. E. Bowers, “Transferred substrate Schottky-collector heterojunction bipolar transistors: first re,” IEEE Electron Device Lett., vol. sults and scaling laws for high f 16, no. 8, pp. 357–359, Aug. 1995. [13] U. Bhattacharya, M. J. Mondry, G. Hurtz, J. Guthrie, M. J. W. Rodwell, T. Liu, C. Nguyen, and D. Rensch, “100 GHz transferred-substrate Schottky-collector heterojunction bipolar transistor,” in Proc. Eighth Int. Conf. Indium Phosphide Related Materials, 1996, pp. 145–148. 0 0 [14] H. Beneking, “The collector function in semiconductor devices,” IEEE Trans. Electron Devices, vol. 43, no. 9, pp. 1416–1427, Sep. 1996. [15] B. Agarwal, D. Mensa, R. Pullela, Q. Lee, U. Bhattacharya, L. Samoska, transferred-subJ. Guthrie, and M. J. W. Rodwell, “A 277 GHz f strate heterojunction bipolar transistor,” in Proc. Ninth Int. Conf. Indium Phosphide Related Materials, 1997, pp. 633–636. [16] Q. Lee, S. C. Martin, D. Mensa, R. P. Smith, J. Guthrie, and M. J. W. Rodwell, “Submicron transferred-substrate heterojunction bipolar transistors,” IEEE Electron Device Lett., vol. 20, no. 8, pp. 396–398, Aug. 1999. [17] T. Arai, H. Tobita, Y. Harada, M. Suhara, Y. Miyamoto, and K. Furuya, “Proposal of buried metal heterojunction bipolar transistor and fabrication of HBT with buried tungsten,” in Proc. Eleventh Int. Conf. Indium Phosphide Related Materials, 1999, pp. 183–186. [18] A. Girardot, A. Henkel, S. L. Delage, M. A. DiForte-Poisson, E. Chartier, D. Floriot, and S. Cassette, “High-performance collector-up InGaP/GaAs heterojunction bipolar transistor with Schottky contact,” Electron. Lett., vol. 35, no. 8, pp. 670–672, Apr. 1999. [19] M. J. Kumar and D. V. Rao, “A new lateral PNM Schottky collector bipolar transistor on SOI for nonsaturating VLSI logic design,” IEEE Trans. Electron Devices, vol. 49, no. 6, pp. 1070–1072, Jun. 2002. [20] M. J. Kumar and C. L. Reddy, “2D-simulation and analysis of lateral SiC N-emitter SiGe P-base Schottky metal-collector (NPM) HBT on SOI,” Microelectron. Reliab., vol. 43, no. 7, pp. 1145–1211, 2003. [21] M. J. Kumar and D. V. Rao, “A new lateral SiGe-base PNM Schottky collector bipolar transistor on SOI for nonsaturating VLSI logic design,” in Proc. 16th Int. Conf. VLSI Design, 2003, pp. 489–492. [22] M. J. Kumar and C. L. Reddy, “A new dual-bandgap SiC-on-Si p-emitter, SiGe n-base, lateral Schottky metal-collector (PNM) HBT on SOI with reduced collector–emitter offset voltage,” in Proc. IEEE Tencon Conf. Convergent Technologies for Asia-Pacific Region, vol. 1, 2003, pp. 493–495. [23] M. J. Kumar and D. V. Rao, “Proposal and design of a new SiC-emitter lateral NPM Schottky collector bipolar transistor on SOI for VLSI applications,” Proc. Inst. Electr. Eng.–Circuits, Devices Systems, vol. 151, no. 1, pp. 63–67, 2004. [24] M. J. Kumar and C. L. Reddy, “Realizing wide bandgap P-SiC-emitter lateral heterojunction bipolar transistors with low collector–emitter offset voltage and high current gain—a novel proposal using numerical simulation,” Proc. Inst. Electr. Eng.—Circuits, Devices and Systems, vol. 151, pp. 399–405, Oct. 2004. [25] Athena Users Manual, Silvaco International, Santa Clara, CA, 2000. [26] Atlas Users Manual, Silvaco International, Santa Clara, CA, 2000. [27] D. J. Roulston, N. D. Arora, and S. G. Chamberlain, “Modeling and measurement of minority-carrier lifetime versus doping in diffused layer of n p silicon diodes,” IEEE Trans. Electron Devices, vol. ED-29, pp. 284–291, 1982. [28] J. A. Appels and H. M. J. Vaes, “High voltage thin layer devices,” in IEDM Tech. Dig., 1979, pp. 238–241. [29] E. Arnold, “Silicon-on-insulator devices for high voltage and power IC applications,” J. Electrochem. Soc., vol. 141, no. 7, pp. 1983–1988, 1994. [30] J. Kim, S. Matsumoto, T. Sakai, and T. Yachi, “Breakdown voltage improvement for thin-film SOI power MOSFETS by buried oxide step structure,” IEEE Electron Device Lett., vol. 15, no. 5, pp. 148–150, May 1994. [31] V. M. C. Chen and J. C. S. Woo, “A low thermal budget, fully selfaligned lateral BJT on thin film SOI substrate for low power BiCMOS applications,” in Symp. VLSI Tech. Dig., 1995, pp. 133–134. [32] S. Kawanaka, T. Fuse, K. Inoh, T. Shino, H. Nii, T. Yamada, M. Yoshimi, and S. Watanabe, “3-D simulation analysis of high performance SOI lateral BJT for RF applications,” in Proc. IEEE Int. SOI Conf., 1998, pp. 29–30. [33] T. Yamada, H. Nii, K. Inoh, T. Shino, S. Kawanaka, Y. Minami, T. Fuse, Y. Yoshimi, Y. Katsumata, S. Watanabe, J. Matsunaga, and H. Ishiuchi, “A novel high-performance lateral BJT on SOI with metal-backed single-silicon external base for low-power/low-cost RF applications,” in Proc. Bipolar/BiCMOS Circuits Technology Meeting, 1999, pp. 129–132. [34] H. Nii, T. Yamada, K. Inoh, T. Shino, S. Kawanaka, M. Yoshimi, and on Y. Katsumata, “A novel lateral bipolar transistor with 67 GHz f thin-film SOI for RF analog applications,” IEEE Trans. Electron Devices, vol. 47, no. 7, pp. 1536–1541, Jul. 2000. KUMAR AND ROY: NEW HIGH BREAKDOWN VOLTAGE LATERAL SCHOTTKY COLLECTOR BT M. Jagadesh Kumar (SM’99) was born in Mamidala, Andhra Pradesh, India. He received the M.S. and Ph.D. degrees in electrical engineering from the Indian Institute of Technology (IIT), Madras, India. From 1991 to 1994, he did his post-doctoral research in modeling and processing of high-speed bipolar transistors in the Department of Electrical and Computer Engineering, University of Waterloo, Waterloo, ON, Canada. While with the University of Waterloo, he also did research on amorphous silicon TFTs. From July 1994 to December 1995, he was initially with the Department of Electronics and Electrical Communication Engineering, IIT, Kharagpur, India, and then joined the Department of Electrical Engineering, IIT, Delhi, India, where he became an Associate Professor in July 1997 and a Professor in January 2005. His research interests are in VLSI device modeling and simulation for nanoscale applications, IC technology, and power semiconductor devices. He has been a Reviewer for the IEE Proceedings on Circuits, Devices and Systems, IEE Electronics Letters, and Solid-State Electronics. His teaching has often been rated as outstanding by the Faculty Appraisal Committee, IIT, Delhi. Dr. Kumar is a Fellow of the Institute of Electronics and Telecommunication Engineers (IETE) of India. He has been a Reviewer for the IEEE TRANSACTIONS ON ELECTRON DEVICES. He was Chairman, Fellowship Committee, 16th International Conference on VLSI Design, New Delhi, in 2003. He is Chairman of the Technical Committee for High Frequency Devices, International Workshop on the Physics of Semiconductor Devices, New Delhi, in 2005. 2501 Sukhendu Deb Roy received the M. Tech. degree in laser science and its applications from Devi Ahilya Vishwavidyalaya, Indore, India, in 1999. He is currently pursuing the Ph.D. degree at the Department of Electrical Engineering, Indian Institute of Technology, Delhi, India, with a focus on improving the tradeoff between the high breakdown voltage and lattice heating effect in thin film lateral bipolar transistors on SOI or partial SOI structures. His other interests include design and analysis of high-voltage Schottky collector bipolar transistors.