1 ECE 310L : L Read the lab assignment in its

advertisement

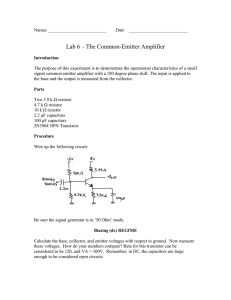

ECE 310L : LAB 10 PRELAB ASSIGNMENT: Read the lab assignment in its entirety. 1. For the circuit shown in Figure 3, compute a value for R1 that will result in a 1N5230B zener diode current of approximately 5mA (you can ignore the effect of base current). Assume Vin is 8V. OBJECTIVES: Construct and verify the operation of an NMOS unity gain amplifier. Construct and verify the operation of a BJT unity gain amplifier. Use an emitter follower/source follower to improve the load regulation of a zener diode voltage regulator. MATERIALS: DC Power supply Oscilloscope Signal Generator DMM Solderless breadboad Hookup Wire Resistors: Various Capacitors: 10uF, 100nF Diode: 1N5230B Transistors: ZVN3306A, 2N2222A BACKGROUND: Some amplifiers are design to act primarily as buffers, where they isolate circuits by providing high input impedance while a voltage gain of nearly one, or unity gain. The common-drain NMOS amplifier shown in Figure 1 is one such amplifier, and is commonly referred to as a source follower. The name source follower indicates the output is taken from the source and is in phase with input, i.e. VS “follows” VG. The term common drain comes from the idea that the drain is connected directly to VDD with no load resistance and in the AC analysis the supply rail, VDD, is a ground reference. The voltage gain (AV) of the source follower is inherently less than one and is generally in the range 0.8 – 0.9. The current gain can be much higher than one, though, allowing the source follower to buffer between a high-impedance source and a low-impedance load. 1 Figure 1 A similar configuration that provides approximately unity gain along with current amplification is the BJT common-collector amplifier or the emitter follower. The emitter follower is the BJT equivalent of the NMOS source follower. This lab will explore the operation of these amplifiers and examine the gain and phase response. Figure 2 2 The input coupling capacitors are very large, so their poles will be near 0. The low frequency response of the system will thus be determined by C2. The RC time constant will set the cut-off frequency so in this design the significant time constant will be C2 and the equivalent resistance seen by C2. In the NMOS amplifier the time constant will be determined by the output capacitor, C2, which is in series with the load resistor and the parallel combination of the source 1 resistor and the impedance seen in the NMOS source, . gm 2I D gm VGS VTN 1 100k 100nF 1.2k || g m In the BJT amplifier, the time constant will be determined by the output capacitor, C2, which is in series with the load resistor and the parallel combination of the emitter resistor and the impedance seen in the BJT emitter, re. re 1 rTH , gm re 1 4.7 k || 4.7 k 40 I c 200 1 where g m 470 || 40 I c VT IC 4.7 k || 4.7 k 100k 100nF 200 Then, you will use the NMOS source follower and the BJT emitter follower configurations to help improve the line/load regulation of a zener diode voltage regulator and allow for higher load current. The BJT version of this circuit is shown in Figure 3. Figure 3 SETUP: Turn on power to the DMM, oscilloscope, power supply, and signal generator. Set the power supply +25V current limit to 100mA. 3 Pay careful attention to the transistor pin-out as shown below to avoid damaging them. ZVN3306A pin-out 2N2222A pin-out LAB ASSIGNMENT: 1. Use the DMM to measure the values of the resistors. Use the measured component values in your calculations. 2. Construct the circuit shown in Figure 1. Connect the oscilloscope to measure the input and VOUT. 3. Measure and record the operating point of the transistor (ID, VDS). Note that there is no drain resistor to permit easy measurement of ID, but you can measure IS. 4. Measure and plot the gain and phase characteristics of the amplifier from 10Hz to 100kHz. Use a 1Vpp sinusoid as the input. 5. Increase the input signal peak-to-peak voltage until the output signal becomes distorted or clips. What are the input and output voltage levels at this point? How do these voltages relate to the bias point of the amplifier? 6. Construct the circuit shown in Figure 2. 7. Measure and record the operating point of the transistor (IC, VCE). Note that there is no collector resistor to permit easy measurement of IC, but you can measure IE. 8. Measure and plot the gain and phase characteristics of the amplifier from 10Hz to 100kHz. Use a 1Vpp sinusoid as the input. 9. Increase the input signal peak-to-peak voltage until the output signal becomes distorted or clips. What are the input and output voltage levels at this point? How do these voltages relate to the bias point of the amplifier? 10. Construct the circuit shown in Figure 3. Set Vin to 8V. Use a value for R1 that will result in a 1N5230B zener diode current of approximately 5mA (you can ignore the effect of base current). Use 10kΩ for the initial load resistor (this will be considered the no-load condition). 4 11. Measure the output voltage VREG. 12. Add a parallel load resistor that will increase the output current to approximately 25 mA. Measure the output voltage VREG. 13. Add a parallel load resistor that will increase the output current to approximately 50 mA. Measure the output voltage VREG. 14. Leave the load set to approximately 50mA, and reduce Vin to 7.2V. Measure the output voltage VREG. 15. Increase Vin to 8.8V. Measure the output voltage VREG. 16. Replace the BJT with the NMOS FET, and repeat steps 10-15. REPORT: Write your report per the criteria in the syllabus and the sample lab report posted on the course web page. In your report, also answer the questions below; 1. Plot your gain (dB) and phase measurements versus the input frequency. Use a logarithmic scale for frequency. 2. How does the measured low-frequency response of the amplifiers compared to the expected values? 3. Compare the performance of the voltage regulators to each other. Calculate line and load regulation for both regulator configurations. 5