I-Type Instructions

advertisement

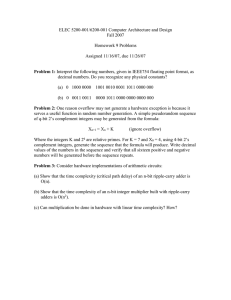

COSC2200: Hardware Systems Assembly to Machine Instruction 66 Outline • R-type yp instructions – Arithmetic – Shift – Logic • I-type instructions – Immediate – Load/store – Branch • J-type instruction 67 1 MIPS R-format Instructions op rs rt rd shamt funct 6 bits 5 bits 5 bits 5 bits 5 bits 6 bits • Instruction fields – op: operation code (opcode) – rs: first source register number – rt: second source register number – rd: destination register number – shamt: shift amount (00000 for now) – funct: function code (extends opcode) R-Type MIPS Instructions • Opcode: p 000000 • Instruction add rd, rs, rt and rd, rs, rt sub rd, rs, rt addu rd, rs, rt or rd, rs, rt Function 100000 100100 100010 100001 100101 2 R-format Example op rs rt rd shamt funct 6 bits 5 bits 5 bits 5 bits 5 bits 6 bits add t0, s1, s2 special s1 s2 t0 0 add 0 17 18 8 0 32 000000 10001 10010 01000 00000 100000 000000100011001001000000001000002 = 0232402016 How about sub s1, t0, t1 Shift Operations op rs rt rd shamt funct 6 bits 5 bits 5 bits 5 bits 5 bits 6 bits • shamt: how many positions to shift • Shift left logical (function: 000000) – Shift left and fill with 0 bits – sll by i bits multiplies by 2i • Shift right logical (function: 000010) – Shift right and fill with 0 bits – srl by i bits divides by 2i (unsigned only) 3 AND Operations • Function: 100100 • Useful to mask bits in a word – Select some bits, clear others to 0 and t0, t1, t2 t2 0000 0000 0000 0000 0000 1101 1100 0000 t1 0000 0000 0000 0000 0011 1100 0000 0000 t0 0000 0000 0000 0000 0000 1100 0000 0000 OR Operations • Function: 100101 • Useful to include bits in a word – Set some bits to 1, leave others unchanged or t0, t1, t2 t2 0000 0000 0000 0000 0000 1101 1100 0000 t1 0000 0000 0000 0000 0011 1100 0000 0000 t0 0000 0000 0000 0000 0011 1101 1100 0000 4 NOT Operations • Useful to invert bits in a word – Change 0 to 1, and 1 to 0 • MIPS has NOR 3-operand instruction – a NOR b == NOT ( a OR b ) – Function: 100111 nor t0, t1, zero Register 0: always read as zero t1 0000 0000 0000 0000 0011 1100 0000 0000 t0 1111 1111 1111 1111 1100 0011 1111 1111 MIPS I-format Instructions op rs rt constant or address 6 bits 5 bits 5 bits 16 bits • Immediate arithmetic, load/store instructions, and branch – rt: destination or source register number – Constant: –215 to +215 – 1 – Address: offset added to base address in rs 5 I-Type Instructions • Opcode: all opcodes except 000000, 00001x, and 0100xx Instruction Opcode Notes addi rt, rs, immediate 001000 addiu rt, rs, immediate 001001 andi rt, rs, immediate 001100 beq rs, rt, label 000100 bne rs, rs rt, rt label 000101 lui rt, immediate 001111 lw rt, immediate(rs) 100011 sw rt, immediate(rs) 101011 xori rt, rs, immediate 001110 I-Type Example • Machine code 0xac240204 0x14040002 the branch target offset: the immediate field || 00. 00 is appended because instructions are word-aligned. 6 Jump Addressing op address 6 bits 26 bits • Jump (j and jal) targets could be anywhere in text segment – Encode full address in instruction – b label opcode: 000010 – jal label opcode: 000011 Direct jump addressing PC: the address of the instruction following the jump Full target address = PC31…28 : (address × 4) PC31…28 Address 4bits 00 26bits 2bits Why can we concatenate 00 to the address? Target Addressing Example • Loop code from earlier example – Assume Loop at location (80000)10 Loop: sll t1, s3, 2 80000 0 0 19 9 4 0 add t1, t1, s6 80004 0 9 22 9 0 32 lw t0, 0(t1) 80008 35 9 8 0 bne t0, s5, Exit 80012 5 8 21 2 addi s3, s3 s3, s3 1 80016 8 19 19 1 j 80020 2 Exit: … Loop 20000 80024 7 Assembler Pseudoinstructions • Most assembler instructions represent p machine instructions one-to-one • Pseudoinstructions: figments of the assembler’s imagination → add $t0, $zero, $t1 blt $t0, $t1, L → slt $at, $t0, $t1 move $t0, $t1 bne $at, $at $zero $zero, L – $at (register 1): assembler temporary Summary • R-type yp – Opcode: 000000 – Function determines the specific operation • I-type – Opcode: 100011 lw 101011 sw • J-type – Opcode: 000010 and 000011 81 8