ISSN : 2348 - 9065 (Online)

ISSN : 2349 - 3143 (Print)

International Journal of Research in Electronics

and Communication Technology (IJRECT 2014)

Vol. 1, Issue 3 July - Sept 2014

An Overview to ASICs: Application Specific Integrated Circuits

Kiran V. Itagi, IIRekha N. Guravvgol, IIISalma M. Khan

I

I,II,III

Dept. of Electronics & Communication, Shaikh College of Engineering and Technology,

Belgaum, Karnataka, India

Abstract

ICs or integrated circuits are those tiny silicon chips that contain thousands of electronic circuits embedded within. Every year,

engineers pack more circuits into these ICs by inventing new ways to advance etching technologies and optical imaging technologies.

Companies like Intel, packed their latest Pentium chip with over a hundred million transistors. These companies see their investments

pay off handsomely because they sell millions of chips every year and hence enough of revenue is reverted back to pay the development

expenses. Some of the IC manufacturers satisfy the need for lower cost IC development with a technology called application specific

integrated circuits, or ASICs. ASICs lower the developing costs of an IC for a specific application by sharing a standard basic design

among many applications.

Keywords

Application specific, gate arrays, design flow, standard cells, requirements capture, FPGA.

I. Introduction

Application specific integrated circuits are customized pieces

of computer hardware that are designed solely to perform one

specific function. ASICs are basically non standard integrated

circuits that have been designed for a specific use or application.

The cost of an ASIC design is high and hence tends to be reserved

for high volume products. . IC manufacturers satisfy the need for

lower cost IC development with a technology called application

specific integrated circuits, or ASICs. ASIC technology has helped

to develop a complex IC with hundreds of thousands of transistors

in a reasonable amount of time [1].

ASICs can improve speed because it is specifically designed to

do one task. It can be made smaller and can be designed to use

less electricity. An ASIC can be found in almost any electronic

device and its use can range from custom rendering of images to

sound conversion. Because ASICs are all custom made and only

available to the company that designed them, they are considered

as a technology the company’s under monopoly.

The development and manufacture of an ASIC design including

ASIC layout is a very expensive process. To reduce the costs

of the design process, there are several levels of customization.

These levels help to reduce costs to considerable heights for

designs where large levels of customization of the ASIC are not

required.

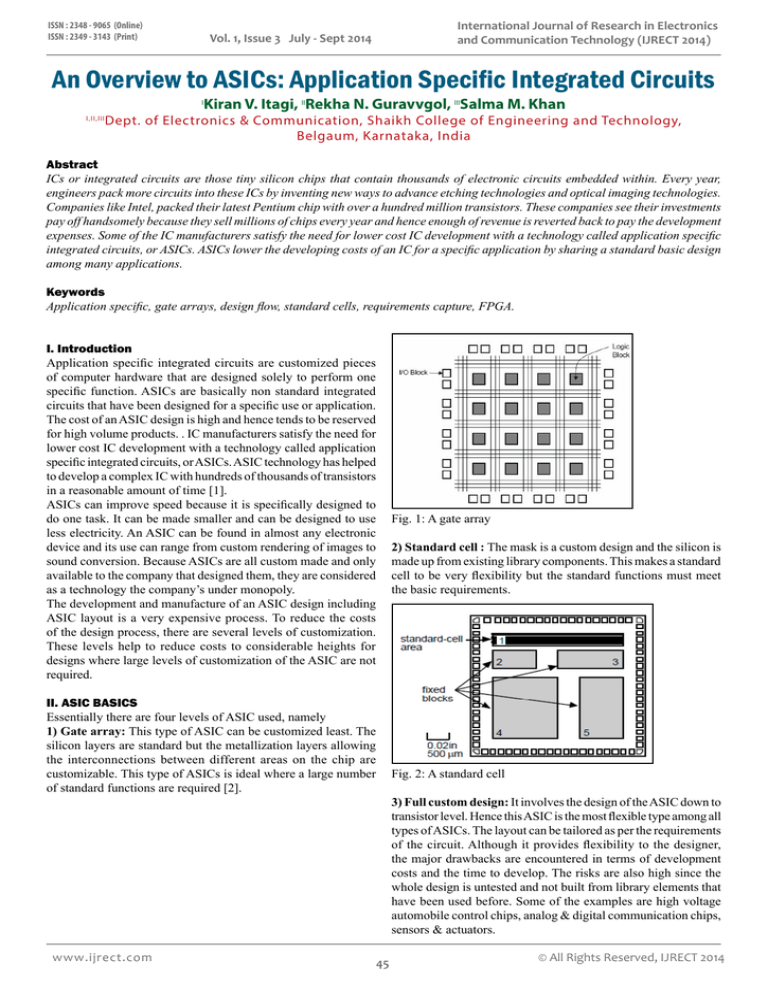

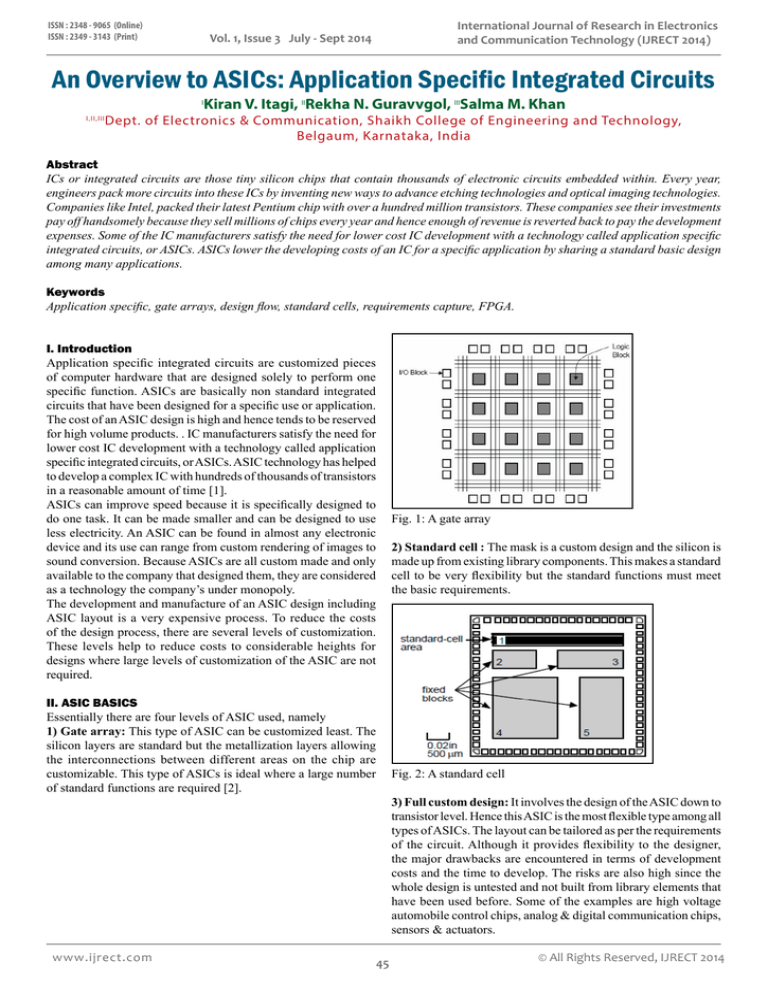

Fig. 1: A gate array

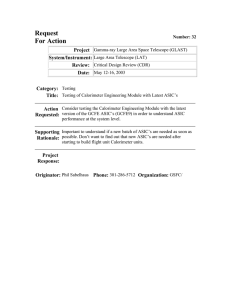

2) Standard cell : The mask is a custom design and the silicon is

made up from existing library components. This makes a standard

cell to be very flexibility but the standard functions must meet

the basic requirements.

II. ASIC BASICS

Essentially there are four levels of ASIC used, namely

1) Gate array: This type of ASIC can be customized least. The

silicon layers are standard but the metallization layers allowing

the interconnections between different areas on the chip are

customizable. This type of ASICs is ideal where a large number

of standard functions are required [2].

www.ijrect.com

Fig. 2: A standard cell

3) Full custom design: It involves the design of the ASIC down to

transistor level. Hence this ASIC is the most flexible type among all

types of ASICs. The layout can be tailored as per the requirements

of the circuit. Although it provides flexibility to the designer,

the major drawbacks are encountered in terms of development

costs and the time to develop. The risks are also high since the

whole design is untested and not built from library elements that

have been used before. Some of the examples are high voltage

automobile control chips, analog & digital communication chips,

sensors & actuators.

45

© All Rights Reserved, IJRECT 2014

International Journal of Research in Electronics

and Communication Technology (IJRECT 2014)

Vol. 1, Issue 3 July - Sept 2014

4) Field programmable logic: A field programmable logic device

is a chip whose logic structure is directly configured by the end user.

Here both the time to market and financial risks can be substantially

reduced. The two major classes of field programmable logic are

Programmable Logic Devices (PLDs) and Field Programmable

Gate Arrays (FPGAs). These have emerged as cost effective ASIC

solutions because they provide low cost prototypes with instant

manufacturing.

HDL behavioural model is simulated to check whether the

design meets the specifications after which a net list also

called structural model is generated by a logic synthesizer

which contains only references to logic cells [4]. Layout

for any type of ASIC may be generated from the structural

model produced by logic synthesis.

c) System partitioning: Microelectronics systems usually

consist of many functional blocks. Sometimes a functional

block becomes too large to fit in a single ASIC. In such

cases, the blocks have to be split or partitioned into a number

of ASIC pieces by specifying goals and objectives. The

main objective here is to minimize the number of external

connections between the ASICs, by keeping them smaller

than a minimum size. CAD tools can be used for this type

of partitioning [4].

d) Floorplanning: Floorplanning is the first step in the physical

design of an ASIC; it is a mapping between the logical and the

physical description [5]. A well thought-out floor plan leads to

an ASIC design with higher performance and optimum area.

Floor plan determines the size of the design cell and creates

the boundary and the core area, and creates wire tracks for

the placement of standard cells in the blocks. The goals of

floor planning are to arrange the blocks on a chip, decide

the location of the I/O pads, decide the location and number

of the power pads decide the type of power distribution,

and decide the location and type of clock distribution. The

main aim of floorplanning is to minimize the chip area and

minimize the interconnect delay.

e) Placement: Placement is a very important and vital step in

ASIC design; it is the part of the design flow that assigns exact

location for the different circuit components in the chip’s core

area [6]. The placement has to be done by optimizing the

objectives such as: minimizing the total wire length between

the circuit components, minimizing the delay, the overall

power consumption, reduce congestion by efficient and

clever placement of circuit components so that the distance

between the components is less and hence there is no roundabout interconnections between the circuit components.

f) Routing: The routing is also a very important step in the

physical design of an IC, routing is basically done in two

stages: Global routing and detailed routing [7]. Fig.3(a)

illustrates the routing process, after placement we have a

layout which contains the information about location of

blocks, I/O pads and pins of blocks at chip boundaries. We

also have a netlist which describes a list of connections by

indicating which pins should be electrically connected to form

a set of nets. Fig.3(b) illustrates some global routing paths. It

first divides the routing region into tiles and then generates a

“loose” route for each connection by finding the tile-to-tile

paths to connect pins. Fig.3(c) shows detailed routing which

decides the exact route for each net by searching within tileto-tile path.

III. Development Stages of An ASIC

The development of an ASIC requires several stages and each

stage must be undertaken very carefully because errors later in the

process become progressively more costly to correct. The stages

involved in the development of ASIC are :

1. Requirements capture: All the circuit requirements are to

be captured so that the design can be set in place correctly.

Changes in the requirements in the design at a later stage

cause additional expenses to be invested in the design.

2. Modeling: At this stage it becomes necessary to model the

high level functionality of the ASIC design to ensure that

correct approach has been taken. This modeling is usually

done in software. In some of the cases, the circuit’s block

diagram can be imported into the design tool to enable the

ASIC modeling to be completed. ASIC modeling is one of the

most important stages because it ensures that the truncation

and the rounding elements are designed correctly. Any kind

of mismatch can create large problems later in the design

that can be difficult to locate and correct [3].

3. ASIC package selection: Some of the criteria that has to be

considered to choose the package for the ASIC are:

i. Number of connections required

ii. Anticipated heat dissipation

iii. Manufacturing process for the circuit

IV. Design Flow

A generic ASIC design flow is basically classified into two

levels: logical level design and physical level design. The first

level of design i.e., logical design consists of design entry, system

partitioning and logic synthesis. The second level of design i.e.,

physical level consists of floor planning, placement, and routing.

The sequence of steps for ASIC design is as follows

a) Design entry: The idea of design entry is to define

microelectronics system to a EDA (electronic design

automation) tool [4]. The conventional method of design

entry was schematic entry. The schematic shows how all

the components are connected in an ASIC. The output of a

schematic-entry tool is a netlist file that contains a description

of all the components in a design and their interconnections.

As ASICs have become very complex in design, other designentry methods are getting more common. Other design entry

methods use graphical methods, such as a schematic, text files

such as a programming language which are most popularly

known programming languages are VHDL and VERILOG

which allows generating the netlist directly from logic

synthesis.

b) Logic Synthesis: Synthesis is the process of converting

the abstract representation of a circuit to a less abstract or

functionally equivalent representation (close to device level).

This is done in two phases; first a HDL behavioural model is

created using graphic or text design which does not contain

any reference to logic cells (gates) in the second phase the

© 2014, IJRECT All Rights Reserved

ISSN : 2348 - 9065 (Online)

ISSN : 2349 - 3143 (Print)

(a)

(b)

(c)

Fig. 3: Routing process. (a) Initial routing process. (b) Global

routing.(c) Detailed routing.

46

www.ijrect.com

ISSN : 2348 - 9065 (Online)

ISSN : 2349 - 3143 (Print)

International Journal of Research in Electronics

and Communication Technology (IJRECT 2014)

Vol. 1, Issue 3 July - Sept 2014

The steps involved in the design of an ASIC are as shown in

Fig.(4)

Table 1: FPGA v/s ASIC

Fig. 4: ASIC design flow

V. Factors Required to Choose ASICs

ASICs have very high density in terms of logic gates on the chip;

hence the resulting product will have higher scalability. It is

possible to tailor the ASIC design to meet the exact requirement for

the product and using an ASIC the overall design can be contained

in one integrated circuit and the number of additional components

can be significantly reduced. As a result they are widely used in

high volume products like cell phones or other similar applications,

often for consumer products where volumes are higher, or for

business products that are widely used.

An ASIC engineer can create functional blocks with known

electrical characteristics, such as propagation delay, capacitance

and inductance, which can also be represented in third party tools.

Standard cell design is the utilization of these functional blocks to

achieve very high gate density and good electrical performance.

Standard cell design falls between gate array and full custom

design in terms of both the non-recurring engineering and recurring

component cost.

The first Application Specific Integrated Circuits traditionally

addressed only logic functions. Now mixed signal ASIC designs

can incorporate both analogue (including RF) and logic functions.

These mixed signal ASICs are particularly useful in being able to

make a complete system on chip, SoC. Here a complete system or

product is integrated onto a chip and virtually no other components

are required. This makes a mixed signal ASIC design a very

attractive proposition for many applications.

VI. Differences Between FPGA and ASICS

The table no. 1 show the differences between the leading

semiconductor chips.

www.ijrect.com

47

Terms

FPGA

ASIC

Definition

Contains

programmable

logic components

called “logic

blocks”, and

programmable

interconnects

and these logic

blocks can be

programmed for

general purpose

applications

It is an integrated circuit

designed for a particular

use, rather than intended

for general-purpose use.

Speed

Less speed

compare to ASIC

As ASIC are designed

for a specific application

they can be optimized

to maximum, hence we

can have high speed in

ASIC designs.

Size

Big

Small

Power

More

Less

Time to

Market

FPGA designs will

take less time, as

the design cycle

is small when

compared to that of

ASIC designs.

In ASIC we have to

do floor planning and

also require advanced

verification, hence take

more time

Cost

More

Less but NRE cost will

be more

ReUsability

A single FPGA can

be used for various

applications, by

reprogramming it.

By definition ASIC are

application specific

cannot be reused.

VII. Latest Trends in ASICs

The ASIC Design has changed since 2006 to accommodate increase

in design costs, rise in design complexity and lengthening in design

cycle times, especially in the System on a Chip (SoC) market.

Semico Research Corp has looked at these impacts from the

point of view of the ASIC Design market and incorporated these

changes and trends in a new report called, ASIC Design Starts:

New Growth Ahead, SC102-12, February 2012. This report looks

at changes and trends in several end applications summarized in

the Consumer ,Computer, Communications, Transportation and

Industrial market categories.

The report tracks the design starts and unit shipments of nine

different types of ASIC products such as Analog, Mixed Signal,

Gate Array, Advanced Performance Value Multicore SoCs,

Multicore SoCs, , Basic SoCs, FPGAs, PLDs, and Structured

ASICs used in the profiled applications. The biggest change in the

ASIC design landscape is the evolution of the SoC market from

two traditional types of SoCs to now include three SoC types:

Performance SoCs become Advanced Performance Multicore

© All Rights Reserved, IJRECT 2014

International Journal of Research in Electronics

and Communication Technology (IJRECT 2014)

Vol. 1, Issue 3 July - Sept 2014

SoCs. Value SoCs become Multicore SoCs. These changes reflect

to the silicon designers who are crafting their silicon solutions

to meet changing market requirements and increasing design

costs.

The new definitions reflect the trends towards using multiple CPU

cores in the end silicon to increase performance and the extensive

use of on-chip Interconnects to tie these CPU cores together. The

new Basic SoC category is a reflection of the increasing use of

CPU cores from third Party Intellectual Property (IP) vendors on

Micro Controllers that had previously used proprietary CPUs to

increase performance and reduce design cycle times.

About Semico: It is a semiconductor marketing & consulting

research company located in Phoenix, Arizona.

Author’s Profile

Mr. Kiran V.Itagi is a lecturer at Department

of Electronics & Communication Engineering

at Shaikh College of Engineering &

Technology, Belgaum. He has completed

Bachelor of Engineering in Electronics &

Telecommunication at K.L.E Society’s Dr.

M. S. Sheshgiri College of Engineering

& Technology, Belgaum. He pursued his

Master’s in VLSI DES at VTU, Belgaum.

His area of interests includes VLSI, embedded systems, and Digital

Signal Processing. At present he is a life member of Indian Society

for Technical Education (MISTE).

VIII. Conclusion

ASIC designs can be tailored to meet the requirements of a product.

ASIC usage can mean that much of the overall design can be

contained in one integrated circuit and the number of additional

components can be drastically reduced. Hence they are extensively

used in large volumes products like smart phones or for business

products that are widely used.

If the ASIC design process is undertaken carefully, it is always

possible to reduce the unit cost, improve unit performance,

reduce unit size and volume and protect company knowledge and

ASICs provide an increase in performance and throughput when

compared to standard integrated circuits (ICs) or PLDs. However

if the errors occur constantly, the ASIC development costs can

increase because further ASIC design and development will be

constantly required. Care has to be taken to avoid such cases.

Ms. Rekha N. Guravvagol is lecturer at the

department of Electronics & Communication

Engineering at Shaikh college of Engineering

and Technology, Belgaum. She completed

Bachelor of Engineering in Maratha Mandal

Engineering college, Belgaum. She pursued

her Master’s in VLSI DES at VTU, Belgaum.

Her area of interest includes VLSI, embedded

system, and microcontrollers.

Ms. Salma M. Khan is a lecturer at the

Department of Electronics & Communication

Engineering at Shaikh College of

Engineering & Technology, Belgaum. She

completed Bachelor of Engineering in

Electronics and communication at Gogte

Institute of Technology, Belgaum. She

pursued her Master‟s in VLSI DES at K.L.E

Society‟s Dr. M. S. Sheshgiri College of

Engineering & Technology, Belgaum. Her

area of interests includes VLSI, embedded systems, control systems

and Fuzzy logic based applications. At present she is a life member

of Indian Society for Technical Education (MISTE).

References

[1]. “An application to developing application specific integrated

circuits” by Elaine Rhodes, 2005.

[2]. “Application specific processors” by Yousef Qasim,

Pradyumna Janga, Sharath Kumar, Hani Alesaimi.

[3]. “Application specific integrated circuits” by Michael John

Sebastian Smith.

[4]. “Application-Specific Integrated Circuits” by Addison

Wesley Longman, 1997

[5]. “An ASIC Design Implementation Perspective” by Golshan

K, 2007.

[6]. “Digital layout –Placement” by Andrew B.Kahng, Sherief

Reda, University of California San Diego, California.

[7]. “Global and Detailed routing” by Huang-Yu Chen, Yao-Wen

Chang, National Taiwan University, Taipei, Taiwan.

© 2014, IJRECT All Rights Reserved

ISSN : 2348 - 9065 (Online)

ISSN : 2349 - 3143 (Print)

48

www.ijrect.com