Chapter 4 Ex and problem solution

advertisement

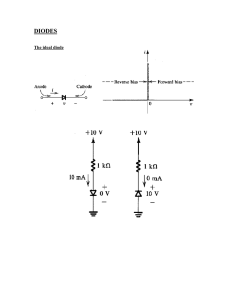

Exercise 4–1

Ex: 4.1 Refer to Fig. 4.3(a). For v I ≥ 0, the

diode conducts and presents a zero voltage drop.

Thus v O = v I . For v I < 0, the diode is cut off,

zero current flows through R, and v O = 0. The

result is the transfer characteristic in Fig. E4.1.

(c)

V5V

I0A

Ex: 4.2 See Fig. 4.3a and 4.3b. During the

positive half of the sinusoid, the diode is forward

biased, so it conducts resulting in v D = 0. During

the negative half cycle of the input signal v I , the

diode is reverse biased. The diode does not

conduct, resulting in no current flowing in the

circuit. So v O = 0 and v D = v I − v O = v I . This

results in the waveform shown in Fig. E4.2.

2.5 k

5 V

(d)

V0V

10 V

vˆI

=

= 10 mA

R

1 k

1

dc component of v O = vˆO

π

1

10

= vˆI =

π

π

= 3.18 V

05

2.5

2 mA

Ex: 4.3 îD =

I

2.5 k

5 V

(e)

I

3V

Ex: 4.4

0

V3V

2V

(a)

0

1V

5 V

I

2.5 k

50

2 mA

2.5

(f)

3

3 mA

1

I

1 k

5 V

V0V

1 k

0

3 V

(b)

0

2 V

5 V

1 V

2.5 k

I0A

V5V

51

1

4 mA

I

V1V

I

Ex: 4.5 Vavg =

10

π

10

10

k

50 + R = π =

1 mA

π

∴ R = 3.133 k

SEDRA-ISM: “E-CH04” — 2014/11/12 — 11:02 — PAGE 1 — #1

Exercise 4–2

R 10 k

Ex: 4.6 Equation (4.5)

I2

V2 − V1 = 2.3 V T log

I1

At room temperature VT = 25 mV

VCC 5 V

10

V2 − V1 = 2.3 × 25 × 10−3 × log

0.1

VD

I2

V2 − V1 = 2.3 × VT log

I1

I2

V2 = V1 + 2.3 × VT log

I1

= 115 mV

Ex: 4.7 i = IS ev /VT

(1)

First iteration

1 (mA) = IS e

(2)

V2 = 0.7 + 2.3 × 25 × 10−3 log

0.7/VT

Dividing (1) by (2), we obtain

i (mA) = e

ID

(v −0.7)/VT

⇒ v = 0.7 + 0.025 ln(i)

where i is in mA. Thus,

for i = 0.1 mA,

= 0.679 V

Second iteration

5 − 0.679

= 0.432 mA

I2 =

10 k

0.43

1

V2 = 0.7 + 2.3 × 25.3 × 10−3 log

v = 0.7 + 0.025 ln(0.1) = 0.64 V

= 0.679 V 0.68 V

and for i = 10 mA,

we get almost the same voltage.

v = 0.7 + 0.025 ln(10) = 0.76 V

0.432

1

ID = 0.43 mA, VD = 0.68 V

b. Use constant voltage drop model:

IS = 10−14 × 1.15T

VD = 0.7 V

= 1.17 × 10−8 A

ID =

1V

= 1 μA

1 M

∴ The iteration yields

Ex: 4.8 T = 125 − 25 = 100◦ C

Ex: 4.9 At 20◦ C I =

constant voltage drop

5 − 0.7

= 0.43 mA

10 k

Ex: 4.11

Since the reverse leakage current doubles for

every 10◦ C increase, at 40◦ C

10 V

I

R

I = 4 × 1 μA = 4 μA

⇒ V = 4 μA × 1 M = 4.0 V

@ 0◦ C

I=

1

μA

4

2.4 V

1

⇒ V = × 1 = 0.25 V

4

Ex: 4.10 a. Use iteration:

Diode has 0.7 V drop at 1 mA current.

Assume VD = 0.7 V

ID =

5 − 0.7

= 0.43 mA

10 k

Diodes have 0.7 V drop at 1 mA

∴ 1 mA = IS e0.7/VT

At a current I (mA),

I = IS eVD /VT

Use Eq. (4.5) and note that

Using (1) and (2), we obtain

V1 = 0.7 V,

I = e(VD −0.7)/VT

I1 = 1 mA

(1)

SEDRA-ISM: “E-CH04” — 2014/11/12 — 11:02 — PAGE 2 — #2

(2)

Exercise 4–3

For an output voltage of 2.4 V, the voltage drop

2.4

= 0.8 V

across each diode =

3

Now I, the current through each diode, is

(d)

V 0.7 V

I = e(0.8−0.7)/0.025

= 54.6 mA

10 − 2.4

R=

54.6 × 10−3

0.7 5

2.5

1.72 mA

I

2.5 k

= 139 5 V

(e)

Ex: 4.12

I

3V

(a)

0

5 V

V 3 0.7

2.3 V

2V

0

1V

2.5 k

5 0.7

I

1.72 mA

2.5

2.3

1

2.3 mA

I

V 0.7 V

1 k

(f)

5V

5 1.7

1

3.3 mA

I

(b)

5 V

3 V

2 V

I0A

2.5 k

1 V

1 k

V 1 0.7

0

1.7 V

0

I

V5V

(c)

Ex: 4.13 rd =

VT

ID

ID = 0.1 mA

rd =

25 × 10−3

= 250 0.1 × 10−3

ID = 1 mA

rd =

25 × 10−3

= 25 1 × 10−3

ID = 10 mA

rd =

25 × 10−3

= 2.5 10 × 10−3

V5V

Ex: 4.14 For small signal model,

iD = v D /rd

2.5 k

I0A

VT

where rd =

ID

For exponential model,

5 V

iD = IS eV /V T

SEDRA-ISM: “E-CH04” — 2014/11/12 — 11:02 — PAGE 3 — #3

(1)

Exercise 4–4

iD2

= e(V2 −V1 ) /V T = ev D /V T

iD1

iD = iD2 − iD1 = iD1 ev D /V T − iD1

= iD1 ev D /V T − 1

c. If iD = 5 − i L = 5 − 1 = 4 mA.

(2)

In this problem, iD1 = ID = 1 mA.

Using Eqs. (1) and (2) with VT = 25 mV, we

obtain

v D (mV)

a

b

c

d

− 10

−5

+5

+ 10

iD (mA)

small

signal

iD (mA)

exponential

model

− 0.4

− 0.2

+ 0.2

+ 0.4

− 0.33

− 0.18

+ 0.22

+ 0.49

Across each diode the voltage drop is

ID

VD = VT ln

IS

4 × 10−3

= 25 × 10−3 × ln

4.7 × 10−16

= 0.7443 V

Voltage drop across 4 diodes

= 4 × 0.7443 = 2.977 V

so change in VO = 3 − 2.977 = 23 mV.

Ex: 4.16 For a zener diode

VZ = VZ0 + IZ rZ

10 = VZ0 + 0.01 × 50

VZ0 = 9.5 V

Ex: 4.15

For IZ = 5 mA,

15 V

VZ = 9.5 + 0.005 × 50 = 9.75 V

For IZ = 20 mA,

R

IL

VO

VZ = 9.5 + 0.02 × 50 = 10.5 V

Ex: 4.17

15 V

R

I

5.6 V

VO

20 mV

a. In this problem,

=

= 20 .

iL

1 mA

∴ Total small-signal resistance of the four diodes

= 20 20

∴ For each diode, rd =

= 5 .

4

VT

25 mV

⇒5=

.

But rd =

ID

ID

∴ ID = 5 mA

15 − 3

= 2.4 k.

5 mA

b. For VO = 3 V, voltage drop across each diode

3

= = 0.75 V

4

and R =

iD = IS eV /VT

IS =

iD

eV /VT

=

5 × 10−3

= 4.7 × 10−16 A

e0.75/0.025

0 to 15 mA

The minimum zener current should be

5 × IZk = 5 × 1 = 5 mA

Since the load current can be as large as 15 mA,

we should select R so that with IL = 15 mA, a

zener current of 5 mA is available. Thus the

current should be 20 mA, leading to

R=

15 − 5.6

= 470 20 mA

Maximum power dissipated in the diode occurs

when IL = 0 is

Pmax = 20 × 10−3 × 5.6 = 112 mV

SEDRA-ISM: “E-CH04” — 2014/11/12 — 11:02 — PAGE 4 — #4

Exercise 4–5

a. The diode starts conduction at

Ex: 4.18

v S = VD = 0.7 V

15 V

√

v S = Vs sin ωt, here Vs = 12 2

I

200 15 5.1

49.5 mA

0.2 k

50 mA

At ωt = θ,

VZ

v S = Vs sin θ = VD = 0.7 V

√

12 2 sin θ = 0.7

0.7

θ = sin−1

2.4◦

√

12 2

Conduction starts at θ and stops at 180 − θ.

Thus, at no load VZ

5.1 V

∴ Total conduction angle = 180 − 2θ = 175.2◦

For line regulation:

b. v O,avg

vo

200 vi mV

vo

7

= 33.8

=

vi

200 + 7

V

200 VO

IL

rZ

V O

−IL (rZ 200 )

=

IL

IL mA

= −6.8

(Vs sin φ − VD ) d φ

θ

1

[−Vs cos φ − VD φ]φ=π−θ

φ−θ

2π

1

[Vs cos θ − Vs cos (π − θ) − VD (π − 2θ )]

=

2π

But cos θ 1, cos (π − θ) − 1, and

π − 2θ π

VD

2Vs

−

2π

2

VD

Vs

−

=

π

2

√

For Vs = 12 2 and VD = 0.7 V

√

12 2 0.7

v O,avg =

−

= 5.05 V

π

2

c. The peak diode current occurs at the peak

diode voltage.

√

12 2 − 0.7

V − VD

∴ îD = s

=

R

100

= 163 mA

√

PIV = +V S = 12 2

v O,avg =

For load regulation:

VZ0

(π−θ

)

=

7

Line regulation =

1

=

2π

17 V

mV

mA

Ex: 4.20

vS

input

Ex: 4.19

Vs

vS

Vs 12 2

VD

0

VD

0

u

u

2

t

output

( )

VS

a. As shown in the diagram, the output is zero

between (π − θ) to (π + θ)

= 2θ

SEDRA-ISM: “E-CH04” — 2014/11/12 — 11:02 — PAGE 5 — #5

t

Exercise 4–6

Here θ is the angle at which the input signal

reaches VD .

Vs

∴ Vs sin θ = VD

VD

θ = sin−1

Vs

VD

2θ = 2 sin−1

Vs

Vs

(a) VO,avg =

1

2π

(Vs sin φ − 2VD ) d φ

2

[−Vs cos φ − 2VD φ]π−θ

φ=θ

2π

1

= [Vs cos φ − Vs cos(π − θ) − 2VD (π − 2θ )]

π

But cos θ ≈ 1,

π

.

2

Peak current

Vs − VD

Vs sin (π /2) − VD

=

=

R

R

If v S is 12 V(rms),

√

√

then Vs = 2 × 12 = 12 2

√

12 2 − 0.7

Peak current =

163 mA

100

Nonzero output occurs for angle = 2 (π − 2θ)

The fraction of the cycle for which v O > 0 is

2 (π − 2θ)

× 100

2π

0.7

2 π − 2 sin−1

√

12 2

× 100

=

2π

=

cos (π − θ) ≈ − 1

π − 2θ ≈ π. Thus

⇒ VO,avg 2Vs

− 2VD

π

√

2 × 12 2

− 1.4 = 9.4 V

π

Peak voltage

(b) Peak diode current =

R

√

Vs − 2VD

12 2 − 1.4

=

=

R

100

= 156 mA

√

PIV = Vs − VD = 12 2 − 0.7 = 16.3 V

=

Ex: 4.22 Full-wave peak rectifier:

D1

vO

vS

vS

97.4 %

Average output voltage VO is

√

Vs

2 × 12 2

VO = 2 − VD =

− 0.7 = 10.1 V

π

π

Peak diode current îD is

√

12 2 − 0.7

Vs − VD

îD =

=

R

100

D

S

=

for θ small.

c. Peak current occurs when φ =

2VV sin–1

1

−θ

[−Vs cos φ − VD φ]πφ=θ

π

Vs

− VD ,

π

input

t

0

θ

2

output

2VD

b. Average value of the output signal is given by

⎡

⎤

(π

−θ)

1 ⎣

2×

VO =

(Vs sin φ − VD ) d φ ⎦

2π

=

Ex: 4.21

R

C

D2

Vp

t

Vr{

assume

ideal diodes

t

= 163 mA

PIV = Vs − VD + VS

√

√

= 12 2 − 0.7 + 12 2

= 33.2 V

T

2

The ripple voltage is the amount of voltage

reduction during capacitor discharge that occurs

SEDRA-ISM: “E-CH04” — 2014/11/12 — 11:02 — PAGE 6 — #6

Exercise 4–7

when the diodes are not conducting. The output

voltage is given by

If t = 0 is at the peak, the maximum diode current

occurs at the onset of conduction or at t = −ωt.

v O = Vp e−t/RC

During conduction, the diode current is given by

T /2

Vp − Vr = Vp e− RC

←

discharge is only half

T

the period. We also assumed t .

2

T /2

Vr = Vp 1 − e− RC

T /2

,

for CR T/2

RC

T /2

Thus Vr Vp 1 − 1 +

RC

T /2

e− RC 1 −

Vr =

Vp

2fRC

(a)

Q.E.D.

QSUPPLIED = QLOST

iCav t = CV r

SUB (a)

Vp

Vp

iD,av − IL t = C

=

2fRC

2fR

Vp π

ωR

iD,av =

Vp π

+ IL

ωtR

where ωt is the conduction angle.

Note that the conduction angle has the same

expression as for the half-wave rectifier and is

given by Eq. (4.30),

2Vr

∼

ωt =

(b)

Vp

Substituting for ωt, we get

⇒ iD,av = πVp

2Vr

·R

Vp

= IL 1 + π

d v S + iL

dt t=−ωt

assuming iL is const. iL Vp

= IL

R

d Vp cos ωt + IL

dt

= −C sin ω t × ωVp + IL

=C

= −C sin(−ωt) × ωVp + IL

For a small conduction angle

Vp

2Vr

⇒ iD,max = Cωt × ωVp + IL

Sub (b) to get

2V r

iD,max = C

ωVp + IL

Vp

Substituting ω = 2πf and using (a) together with

Vp /R IL results in

Vp

Q.E.D.

iDmax = IL 1 + 2π

2Vr

Ex: 4.23

D4

ac

line

voltage

D1

vO vS

R

D2

C

D3

+ IL

Since the output is approximately held at Vp ,

Vp

≈ IL · Thus

R

Vp

⇒ iD,av ∼

+ IL

= π IL

2Vr

iD,max = C

sin(−ωt) ≈ − ωt. Thus

To find the average diode current, note that the

charge supplied to C during conduction is equal

to the charge lost during discharge.

=

iD = iC + iL

Q.E.D.

The output voltage, v O , can be expressed as

v O = Vp − 2VD e−t/RC

At the end of the discharge interval

v O = Vp − 2VD − Vr

The discharge occurs almost over half of the time

period T /2.

For time constant RC T

2

SEDRA-ISM: “E-CH04” — 2014/11/12 — 11:02 — PAGE 7 — #7

Exercise 4–8

e−t/RC 1 −

1

T

×

2

RC

Ex: 4.24

T

1

∴ VP − 2VD − Vr = Vp − 2VD 1 − ×

2

RC

⇒ Vr = Vp − 2VD

i

vI

i

T

×

2RC

iD

vO

√

Here Vp = 12 2 and Vr = 1 V

iR

VD = 0.8 V

T=

1 k

1

1

=

s

f

60

√

1 = (12 2 − 2 × 0.8) ×

1

2 × 60 × 100 × C

√

(12 2 − 1.6)

C=

= 1281 μF

2 × 60 × 100

Without considering the ripple voltage, the dc

output voltage

√

= 12 2 − 2 × 0.8 = 15.4 V

If ripple voltage is included, the output voltage is

√

Vr

= 14.9 V

= 12 2 − 2 × 0.8 −

2

IL =

vA

vD

14.9

0.15 A

100 The conduction angle ωt can be obtained

using

√

Eq. (4.30) but substituting Vp = 12 2 − 2 × 0.8:

2Vr

2×1

ωt =

=

√

Vp

12 2 − 2 × 0.8

The average and peak diode currents can be

calculated using Eqs. (4.34) and (4.35):

Vp

14.9 V

iDav = IL 1 + π

, where IL =

,

2Vr

100 √

Vp = 12 2 − 2 × 0.8, and Vr = 1 V; thus

iDmax = I 1 + 2π

iD = IS ev D /VT

iD

= e(v D −0.7)/V T

1 mA

iD

+ 0.7 V

⇒ v D = VT ln

1 mA

For v I = 10 mV, v O = v I = 10 mV

It is an ideal op amp, so i+ = i− = 0.

10 mV

= 10 μA

1 k

10 μA

+ 0.7 = 0.58 V

v D = 25 × 10−3 ln

1 mA

∴ iD = iR =

v A = v D + 10 mV

= 0.58 + 0.01

= 0.59 V

For v I = 1 V

= 0.36 rad = 20.7◦

iDav = 1.45 A

The diode has 0.7 V drop at 1 mA current.

Vp

2Vr

vO = vI = 1 V

vO

1

=

= 1 mA

1 k

1 k

v D = 0.7 V

iD =

VA = 0.7 V + 1 k × 1 mA

= 1.7 V

For v I = −1 V, the diode is cut off.

∴ vO = 0 V

v A = −12 V

= 2.76 A

Ex: 4.25

PIV of the diodes

= VS − VDO

√

= 12 2 − 0.8 = 16.2 V

To provide a safety margin, select a diode capable

of a peak current of 3.5 to 4A and having a PIV

rating of 20 V.

vI

vO

R

SEDRA-ISM: “E-CH04” — 2014/11/12 — 11:02 — PAGE 8 — #8

IL

Exercise 4–9

v I > 0 ∼ diode is cut off, loop is open, and the

opamp is saturated:

vO = 0 V

v I < 0 ∼ diode conducts and closes the negative

feedback loop:

vO = vI

For v I ≤ −5 V, diode D1 conducts and

1

(+v I + 5)

2

vI V

= −2.5 +

2

For v I ≥ 5 V, diode D2 conducts and

v O = −5 +

1

(v I − 5)

2

vI V

= 2.5 +

2

v O = +5 +

Ex: 4.26

10 k

D2

D1

5V

vO

5V v

O

vI

Ex: 4.27 Reversing the diode results in the peak

output voltage being clamped at 0 V:

10 k

10 k

Both diodes are cut off

t

10 V

Here the dc component of v O = VO = −5 V

for −5V ≤ v I ≤ + 5V

and v O = v I

SEDRA-ISM: “E-CH04” — 2014/11/12 — 11:02 — PAGE 9 — #9

Chapter 4–1

4.3

4.1

1

(a)

I

1.5 V

VD

D1

1 V

(a)

Cutoff

D2

V2V

2 V

Conducting

1

I

2 k

I

1.5 V

VD

2 (3)

2 k

2.5 mA

3 V

(b)

(b)

3 V

(a) The diode is reverse biased, thus

I =0A

2 k

Conducting

VD = −1.5 V

3 (1)

2

1 mA

I

D1

1 V

V1V

(b) The diode is forward biased, thus

VD = 0 V

2 V

D2

1.5 V

= 1.5 A

I=

1

4.2 Refer to Fig. P4.2.

(a) Diode is conducting, thus

4.4

(a)

V = −3 V

I=

Cutoff

vO

+3 − (−3)

= 0.6 mA

10 k

5V

(b) Diode is reverse biased, thus

0

t

I =0

V = +3 V

V p+ = 5 V Vp− = 0 V f = 1 kHz

(c) Diode is conducting, thus

(b)

V = +3 V

I=

vO

+3 − (−3)

= 0.6 mA

10 k

(d) Diode is reverse biased, thus

I =0

V = −3 V

0

t

5 V

Vp+ = 0 V Vp− = −5 V f = 1 kHz

SEDRA-ISM: “P-CH04-001-013” — 2014/11/12 — 15:18 — PAGE 1 — #1

Chapter 4–2

(c)

vO 0 V

(h)

vO

t

0

t

v O = 0 V ∼ The output is always shorted to

ground as D1 conducts when v I > 0 and D2

conducts when v I < 0.

vO = 0 V

(i)

vO

Neither D1 nor D2 conducts, so there is no output.

5V

(d)

vO

t

2.5 V

5V

t

Vp+ = 5 V, Vp− = −2.5 V,

Vp+ = 5 V,

Vp− = 0 V,

f = 1 kHz

When v I > 0, D1 is cut off and v O follows v I .

f = 1 kHz

When v I < 0, D1 is conducting and the circuit

becomes a voltage divider where the negative

peak is

Both D1 and D2 conduct when v I > 0

(e)

vO

1 k

× −5 V = −2.5 V

1 k + 1 k

(j)

vO

5V

5 V

Vp+ = 5 V,

Vp− = −5 V,

t

5V

f = 1 kHz

D1 conducts when v I > 0 and D2 conducts when

v I < 0. Thus the output follows the input.

(f)

2.5 V

Vp+ = 5 V, Vp− = −2.5 V,

t

f = 1 kHz

When v I > 0, the output follows the input as D1

is conducting.

vO

5V

t

When v I < 0, D1 is cut off and the circuit

becomes a voltage divider.

(k)

vO

Vp+ = 5 V,

Vp− = 0 V,

f = 1 kHz

5V

D1 is cut off when v I < 0

1V

t

(g)

vO

5 V

4 V

t

5 V

Vp+ = 1 V, Vp− = −4 V, f = 1 kH3

When v I > 0, D1 is cut off and D2 is conducting.

The output becomes 1 V.

Vp+ = 0 V,

Vp− = −5 V,

f = 1 kHz

D1 shorts to ground when v I > 0 and is cut off

when v I < 0 whereby the output follows v I .

When v I < 0, D1 is conducting and D2 is cut off.

The output becomes:

vO = vI + 1 V

SEDRA-ISM: “P-CH04-001-013” — 2014/11/12 — 15:18 — PAGE 2 — #2

Chapter 4–3

X = AB, Y = A + B

4.5

X and Y are the same for

A=B

X and Y are opposite if A = B

4.7 The case for the highest current in a single

diode is when only one input is high:

VY = 5 V

VY

≤ 0.2 mA ⇒ R ≥ 25 k

R

From Fig. P4.5 we see that when v I < VB ; that is,

v I < 3 V, D1 will be conducting the current I and

iB will be zero. When v I exceeds the battery

voltage (3 V), D1 cuts off and D2 conducts, thus

steering I into the battery. Thus, iB will have the

waveform shown in the figure. Its peak value will

be 60 mA. To obtain the average value, we first

determine the conduction angle of D2 , (π − 2θ),

where

3

= 30◦

θ = sin−1

6

4.8 The maximum input current occurs when one

input is low and the other two are high.

5−0

≤ 0.2 mA

R

R ≥ 25 k

4.9

3 V

Thus

π − 2θ = 180◦ − 60 = 120◦

12 k

0.33 mA

The average value of iB will be

60 × 120◦

= 20 mA

360◦

If the peak value of v I is reduced by 10%, i.e.

from 6 V to 5.4 V, the peak value of iB does not

change. The conduction angle of D2 , however,

changes since θ now becomes

3

= 33.75◦

θ = sin−1

5.4

1 V

iB |av =

I0

D1

OFF

D2

ON

V 1 V

0.33

mA

6 k

and thus

3 V

(a)

π − 2θ = 112.5◦

Thus the average value of iB becomes

iB |av =

60 × 112.5◦

= 18.75 mA

360◦

4.6

A

B

X

Y

0

0

1

1

0

1

0

1

0

0

0

1

0

1

1

1

(a) If we assume that both D1 and D2 are

conducting, then V = 0 V and the current in D2

will be [0 − (−3)]/6 = 0.5 mA. The current in

the 12 k will be (3 − 0)/12 = 0.25 mA. A node

equation at the common anodes node yields a

negative current in D1 . It follows that our

assumption is wrong and D1 must be off. Now

making the assumption that D1 is off and D2 is on,

we obtain the results shown in Fig. (a):

I =0

V = −1 V

SEDRA-ISM: “P-CH04-001-013” — 2014/11/12 — 15:18 — PAGE 3 — #3

Chapter 4–4

3 V

4.12

D

RS

6 k

3 – 0 0.5 mA

6

vI

0V

D1

ON

0.25 mA

D2

ON

0 – (–3)

12

0.25 mA

vO R

vI 1 vI

R RS

2

iD V0

vI

R RS

D starts to conduct when v I > 0

12 k

vO

3 V

(b)

vI

0

(b) In (b), the two resistors are interchanged.

With some reasoning, we can see that the current

supplied through the 6-k resistor will exceed

that drawn through the 12-k resistor, leaving

sufficient current to keep D1 conducting.

Assuming that D1 and D2 are both conducting

gives the results shown in Fig. (b):

4.13 For v I > 0 V: D is on, v O = v I , iD = v I /R

For v I < 0 V: D is off , v O = 0, iD = 0

I = 0.25 mA

V =0V

4.10 The analysis is shown on the circuit

diagrams below.

√

120 2

≥ 4.2 k

40

The largest reverse voltage appearing across the

diode is equal to the peak input voltage:

√

120 2 = 169.7 V

4.11 R ≥

These figures belong to Problem 4.10.

reverse biased

10 10 5 k

5 k

5 k

V

I

10

10 10

2.5 V

5

20 k

I

2.5

0.1 mA

5 20

I0

2.5 V

V

1.5 V

V 1.5 2.5 1 V

(b)

V 0.1 20 2 V

(a)

SEDRA-ISM: “P-CH04-001-013” — 2014/11/12 — 15:18 — PAGE 4 — #4

Chapter 4–5

∴ Peak-to-peak sine wave voltage

4.14

= 2A = 34 V

Given the average diode current to be

1

2π

2π

A sin φ − 12

d φ = 100 mA

R

0

1

2π

−17 cos φ − 12φ

R

φ = 0.75π

= 0.1

φ = 0.25π

R = 8.3 A − 12

= 0.6 A

R

Peak reverse voltage = A + 12 = 29 V

Peak diode current =

For resistors specified to only one significant digit

and peak-to-peak voltage to the nearest volt,

choose A = 17 so the peak-to-peak sine wave

voltage = 34 V and R = 8 .

Conduction starts at v I = A sin θ = 12

17 sin θ = 12

π rad

θ=

4

Conduction stops at π − θ.

4.15

R

vI

∴ Fraction of cycle that current flows is

D

12 V

vI

A

12 V

Peak diode current

17 − 12

= 0.625 A

=

8

Peak reverse voltage =

A + 12 = 29 V

2

0 π − 2θ

× 100 = 25%

2π

Average diode current =

1 −17 cos φ − 12φ φ = 3π/4

= 103 mA

2π

8

φ = π/4

conduction occurs

v I = A sin θ = 12 ∼ conduction through D

occurs

For a conduction angle (π − 2θ ) that is 25% of a

cycle

1

π − 2θ

=

2π

4

π

θ=

4

A = 12/sin θ = 17 V

4.16

V

RED

3V

ON

0

OFF

–3 V OFF

4.17 VT =

GREEN

OFF

- D1 conducts

OFF

- No current flows

ON

- D2 conducts

kT

q

where

k = 1.38 × 10−23 J/K = 8.62 × 10−5 eV/K

T = 273 + x◦ C

q = 1.60 × 10−19 C

SEDRA-ISM: “P-CH04-014-030” — 2014/11/12 — 15:20 — PAGE 5 — #1

Chapter 4–6

Thus

I = 10−3 e(0.6 − 0.7)/0.025

VT = 8.62 × 10−5 × (273 × x◦ C), V

= 18.3 μA

x [◦ C]

VT [mV]

−55

0

+55

+125

18.8

23.5

28.3

34.3

To increase the current by a factor of 10, VD must

be increased by VD ,

10 = eVD /0.025

⇒ VD = 0.025 ln10 = 57.6 mV

4.21 IS can be found by using IS = ID · e−VD /VT .

for VT = 25 mV at 17◦ C

Let a decrease by a factor of 10 in ID result in a

decrease of VD by V:

ID = IS eVD /VT

4.18 i = I S ev /0.025

ID

= IS e(VD −V)/VT = IS eVD /VT · e−V /V T

10

∴ 10,000IS = IS ev /0.025

Taking the ratio of the above two equations, we

have

v = 0.230 V

At v = 0.7 V,

10 = eV /V T ⇒ V 60 mV

i = IS e0.7/0.025 = 1.45 × 1012 IS

Thus the result in each case is a decrease in the

diode voltage by 60 mV.

(a) VD = 0.700 V, ID = 1 A

⇒ IS = 6.91 × 10−13 A;

4.19 I1 = IS e0.7/VT = 10−3

i2 = IS e0.5/VT

10% of ID gives VD = 0.64 V

i2

i2

0.5 − 0.7

= −3 = e 0.025

i1

10

(b) VD = 0.650 V, ID = 1 mA

⇒ IS = 5.11 × 10−15 A;

i2 = 0.335 μA

10% of ID gives VD = 0.59 V

(c) VD = 0.650 V, ID = 10 μA

⇒ IS = 5.11 × 10−17 A;

4.20 I = IS eVD /VT

10−3 = IS e0.7/VT

(1)

10% of ID gives VD = 0.59 V

(2)

(d) VD = 0.700 V, ID = 100 mA

⇒ IS = 6.91 × 10−14 A;

For VD = 0.71 V,

I = IS e

0.71/VT

10% of ID gives VD = 0.64 V

Combining (1) and (2) gives

I = 10−3 e(0.71 − 0.7)/0.025

4.22 IS can be found by using IS = ID · e−VD /VT .

= 1.49 mA

For VD = 0.8 V,

(3)

I = IS e0.8/VT

Combining (1) and (3) gives

I = 10−3 × e(0.8 − 0.7)/0.025

= 54.6 mA

Similarly, for VD = 0.69 V we obtain

−3

I = 10

×e

Let an increase by a factor of 10 in ID result in an

increase of VD by V:

ID = IS eVD /VT

10I D = IS e(VD +V )/VT = IS eVD /VT · eV /V T

Taking the ratio of the above two equations, we

have

10 = eV /V T ⇒ V 60 mV

(0.69 − 0.7)/0.025

= 0.67 mA

Thus the result is an increase in the diode voltage

by 60 mV.

and for VD = 0.6 V we have

Similarly, at ID /10, VD is reduced by 60 mV.

SEDRA-ISM: “P-CH04-014-030” — 2014/11/12 — 15:20 — PAGE 6 — #2

Chapter 4–7

(a) VD = 0.70 V, ID = 10 mA

⇒ IS = 6.91 × 10−15 A;

4.25

I

ID × 10 gives V D = 0.76 V

ID /10 gives VD = 0.64 V

(b) VD = 0.70 V, ID = 1 mA

⇒ IS = 6.91 × 10−16 A;

ID1

ID2

D1

D2

VD

ID × 10 gives V D = 0.76 V

ID /10 gives VD = 0.64 V

(c) VD = 0.80 V, ID = 10 A

⇒ IS = 1.27 × 10−13 A;

ID × 10 gives V D = 0.86 V

ID /10 gives VD = 0.74 V

(d) VD = 0.70 V, ID = 1 mA

⇒ IS = 6.91 × 10−16 A;

ID × 10 gives V D = 0.76 V

ID1 = IS1 eVD /VT

(1)

VD /VT

(2)

ID2 = IS2 e

Summing (1) and (2) gives

ID1 + ID2 = (IS1 + IS2 )eVD /VT

But

ID1 + ID2 = I

Thus

ID /10 gives VD = 0.64 V

I = (IS1 + IS2 ) eVD /VT

(e) VD = 0.6 V, ID = 10 μA

⇒ IS = 3.78 × 10−16 A

From Eq. (3) we obtain

I

VD = VT ln

IS1 + IS2

ID × 10 gives V D = 0.66 V

ID /10 gives VD = 0.54 V

4.23 The voltage across three diodes in series is

2.0 V; thus the voltage across each diode must be

0.667 V. Using ID = IS eVD /VT , the required

current I is found to be 3.9 mA.

(3)

Also, Eq. (3) can be written as

IS2

I = IS1 eVD /VT 1 +

IS1

(4)

Now using (1) and (4) gives

ID1 =

I

IS1

=I

1 + (IS2 /IS1 )

IS1 + IS2

We similarly obtain

If 1 mA is drawn away from the circuit, ID will be

2.9 mA, which would give VD = 0.794 V, giving

an output voltage of 1.98 V. The change in output

voltage is −22 mV.

ID2 =

I

IS2

=I

1 + (IS1 /IS2 )

IS1 + IS2

4.26

4.24 Connecting an identical diode in parallel

would reduce the current in each diode by a factor

of 2. Writing expressions for the currents, we have

I

ID = IS eVD /VT

ID

= IS e(VD −V)/VT = IS eVD /VT · e−V /V T

2

Taking the ratio of the above two equations, we

have

2=e

V /V T

D1

D2

D3

I1

2I1

4I1

D4

8I1

⇒ V = 17.3 mV

Thus the result is a decrease in the diode voltage

by 17.3 mV.

I1 0.1 mA

SEDRA-ISM: “P-CH04-014-030” — 2014/11/12 — 15:20 — PAGE 7 — #3

Chapter 4–8

The junction areas of the four diodes must be

related by the same ratios as their currents, thus

A4 = 2A3 = 4A2 = 8 A1

With I1 = 0.1 mA,

I = 0.1 + 0.2 + 0.4 + 0.8 = 1.5 mA

4.27 We can write a node equation at the anodes:

ID2 = I1 − I2 = 7 mA

ID1 = I2 = 3 mA

We can write the following equation for the diode

voltages:

V = VD2 − VD1

Solving the above equation, we have

R = 42 4.29 For a diode conducting a constant current,

the diode voltage decreases by approximately 2

mV per increase of 1◦ C.

T = −20◦ C corresponds to a temperature

decrease of 40◦ C, which results in an increase of

the diode voltage by 80 mV. Thus VD = 770 mV.

T = + 85◦ C corresponds to a temperature

increase of 65◦ C, which results in a decrease of

the diode voltage by 130 mV. Thus VD = 560 mV.

10 V

4.30

If D2 has saturation current IS , then D1 , which is

10 times larger, has saturation current 10IS . Thus

we can write

I

R1

ID2 = IS eVD2 /VT

ID1 = 10I S eVD1 /VT

Taking the ratio of the two equations above, we

have

7

1 (VD2 −VD1 )/VT

ID2

1 V /V T

= =

e

e

=

ID1

3

10

10

70

= 78.7 mV

⇒ V = 0.025 ln

3

D1

V1

D2

V2

To instead achieve V = 60 mV, we need

At 20◦ C:

I1 − I2

1 0.06/0.025

ID2

e

=

=

= 1.1

ID1

I2

10

VR1 = V2 = 520 mV

Solving the above equation with I1 still at 10 mA,

we find I2 = 4.76 mA.

4.28 We can write the following node equation at

the diode anodes:

ID2 = 10 mA − V /R

ID1 = V /R

We can write the following equation for the diode

voltages:

V = VD2 − VD1

R1 = 520 k

520 mV

= 1 μA

520 k

Since the reverse current doubles for every 10◦ C

rise in temperature, at 40◦ C, I = 4 μA

I=

ID2

40°C

4 µA

40 mV

1 µA

480

We can write the following diode equations:

520 mV

ID2 = IS eVD2 /VT

V2 = 480 + 2.3 × 1 × 25 log 4

ID1 = IS eVD1 /VT

= 514.6 mV

Taking the ratio of the two equations above, we

have

10 mA − V /R

ID2

= e(VD2 −VD1 )/VT = eV /V T

=

ID1

V /R

To achieve V = 50 mV, we need

10 mA − 0.05/R

ID2

= e0.05/0.025 = 7.39

=

ID1

0.05/R

20°C

VR1 = 4 μA × 520 k = 2.08 V

1

μA

4

V2 = 560 − 2.3 × 1 × 25 log 4

At 0◦ C, I =

= 525.4 mV

1

VR1 = × 520 = 0.13 V

4

SEDRA-ISM: “P-CH04-014-030” — 2014/11/12 — 15:20 — PAGE 8 — #4

V2

Chapter 4–9

1.0

V = VT ln

= 57.6 mV

0.1

⇒ VD = 757.6 mV

4.31 For a diode conducting a constant current,

the diode voltage decreases by approximately

2 mV per increase of 1◦ C.

A decrease in VD by 100 mV corresponds to a

junction temperature increase of 50◦ C.

ID = 3 mA:

3

0.1

= 85 mV ⇒ VD = 785 mV

The power dissipation is given by

V = VT ln

PD = (10 A) (0.6 V) = 6 W

For the second diode, with

The thermal resistance is given by

ID = 1 A and VD = 700 mV, we have

50◦ C

T

= 8.33◦ C/W

=

PD

6W

4.32 Given two different voltage/current

measurements for a diode, we can write

ID = 1.0 mA:

0.001

= −173 mV

V = VT ln

1

⇒ VD = 527 mV

ID1 = IS eVD1 /VT

ID = 3 mA:

ID2 = IS eVD2 /VT

0.003

1

⇒ VD = 555 mV

= −145 mV

V = VT ln

Taking the ratio of the above two equations, we

have

ID1

= IS e(VD1 −VD2 )/VT ⇒ VD1 − VD2

ID2

ID1

= VT ln

ID2

For ID = 1 mA, we have

1 × 10−3 A

V = VT ln

= −230 mV

10 A

⇒ VD = 570 mV

For ID = 3 mA, we have

3 × 10−3 A

V = VT ln

= −202 mV

10 A

⇒ VD = 598 mV

Assuming VD changes by –2 mV per 1◦ C increase

in temperature, we have, for ±20◦ C changes:

For ID = 1 mA, 530 mV ≤ VD ≤ 610 mV

For ID = 3 mA, 558 mV ≤ VD ≤ 638 mV

Thus the overall range of VD is between 530 mV

and 638 mV.

For both ID = 1.0 mA and ID = 3 mA, the

difference between the two diode voltages is

approximately 230 mV. Since, for a fixed diode

current, the diode voltage changes with

temperature at a constant rate (–2 mV per ◦ C

temp. increase), this voltage difference will be

independent of temperature!

4.34

R 1 kΩ

VDD

i

1V

v

IS = 10−15 A = 10−12 mA

Calculate some points

v = 0.6 V ,

i = IS ev /V T

= 10−12 e0.6/0.025

4.33 Given two different voltage/current

measurements for a diode, we have

0.03 mA

ID1

= IS e(VD1 −VD2 )/VT ⇒ VD1 − VD2

ID2

ID1

= VT ln

ID2

v = 0.65 V,

i 0.2 mA

v = 0.7 V,

i 1.45 mA

For the first diode, with ID = 0.1 mA and

VD = 700 mV, we have

ID = 1 mA:

Make a sketch showing these points and load line

and determine the operating point. The points for

the load line are obtained using

ID =

VDD − VD

R

SEDRA-ISM: “P-CH04-031-053” — 2014/11/12 — 17:25 — PAGE 9 — #1

Chapter 4–10

i (mA)

4.35

R 1 k

2.0

Diode characteristic

1V

ID

VD

1.0

0.8

0.6

0.4

0.2

0

Load line

IS = 10−15 A = 10−12 mA

0.4

0.6

0.8

1.0

v (V)

Use the iterative analysis procedure:

1 − 0.7

= 0.3 mA

1K

ID

0.3

= 0.025 ln

2. VD = VT ln

−12

IS

10

1. VD = 0.7 V, ID =

From this sketch one can see that the operating

point must lie between v = 0.65 V to v = 0.7 V

i

For i = 0.3 mA, v = VT ln

IS

3

= 0.025 × ln

10−12

= 0.661 V

For i = 0.4 mA, v = 0.668 V

Now we can refine the diagram to obtain a better

estimate

0.4

i (mA)

= 0.6607 V

||

1 − 0.6607

= 0.3393 mA

1K

0.3393

= 0.6638 V

3. VD = 0.025 ln

10−12

ID =

1 − 0.6638

= 0.3362 mA

1K

0.3362

= 0.6635 V

4. VD = 0.025 ln

10−12

ID =

1 − 0.6635

= 0.3365 mA

1 k

Stop here as we are getting almost same value of

ID and VD

ID =

0.35

4.36

Load line

500 1V

0.30

0.660

0.664

0.67

v (V)

From this graph we get the operating point

i = 0.338 mA, v = 0.6635 V

Now we compare graphical results with the

exponential model.

At i = 0.338 mA

i

0.338

= 0.025 × ln

v = VT ln

IS

10−12

= 0.6637 V

i

v

1 − 0.7

= 0.6 mA

0.5 k

b) Diode has 0.7 V drop at 1 mA current. Use

Eq. (4.5):

i2

v 2 = v 1 + 2.3VT log

i1

a) ID =

1. v = 0.7 V

1 − 0.7

= 0.6 mA

1 i=

0.5 k

0.6

1

The difference between the exponential model

and graphical results is = 0.6637 − 0.6635

2. v = 0.7 + 2.3 × 0.025 log

= 0.0002 V

= 0.6872 V

1 − 0.6872

= 0.6255 mA

2 i=

0.5

= 0.2 mV

SEDRA-ISM: “P-CH04-031-053” — 2014/11/12 — 17:25 — PAGE 10 — #2

Chapter 4–11

0.6255

3. v = 0.7 + 2.3 × 0.025 log

1

N

= 0.6882 V

⫹

1 − 0.6882

= 0.6235 mA

3 i=

0.5 k

0.6235

4. v = 0.7 + 2.3 × 0.025 log

1

= 0.6882 V

4 i=

1 − 0.6882

= 0.6235 mA

0.5 k

Stop as we are getting the same result.

V

1 mA

⫺

The voltage drop across each pair of diodes is

1.3 V. ∴ Voltage drop across each diode

1.3

=

= 0.65 V. Using

2

I2 = I1 e(V2 −V1 )/VT

= 2e(0.65−0.7)/0.025

4.37 We first find the value of IS for the diode,

given by IS = ID e−VD /VT with ID = 1 mA and

VD = 0.75 V. This gives IS = 9.36 × 10−17 A.

In order to have 3.3 V across the 4

series-connected diodes, each diode drop must be

0.825 V. Applying this voltage to the diode gives

current ID = 20.1 mA. We can then find the

resistor value using

15 V − 3.3 V

R=

= 582 20.1 mA

4.38 Constant voltage drop model:

Using v D = 0.7 V, ⇒ iD1 =

V − 0.7

R

Using v D = 0.6 V, ⇒ iD2 =

V − 0.6

R

For the difference in currents to be only 1%,

⇒ iD2 = 1.01iD1

V − 0.6 = 1.01 (V − 0.7)

V = 10.7 V

= 0.2707 mA

Thus current through each branch is 0.2707 mA.

The 1 mA will split in =

1

= 3.69 branches.

0.2707

Choose N = 4.

There are 4 pairs of diodes in parallel.

∴ We need 8 diodes.

Current through each pair of diodes

1 mA

= 0.25 mA

=

4

∴ Voltage across each pair

0.25

= 2 0.7 + 0.025 ln

2

= 1.296 V

SPECIAL NOTE: There is another possible

design utilizing only 6 diodes and realizing a

voltage of 1.313 V. It consists of the series

connection of 4 parallel diodes and 2 parallel

diodes.

4.40 Refer to Example 4.2.

For V = 3 V and R = 1 k:

(a)

3 − 0.7

= 2.3 mA

=

1

At VD = 0.7 V,

iD1

At VD = 0.6 V,

iD2 =

3 − 0.6

= 2.4 mA

1

2.4

iD2

=

= 1.04

iD1

2.3

Thus the percentage difference is 4%.

10 V

5 I 1.861 10 k

0.86 mA

10 0

1 mA

10

V0V 3

1 0.7 V

4.39 Available diodes have 0.7 V drop at 2 mA

current since 2VD = 1.4 V is close to 1.3 V, use N

parallel pairs of diodes to split the 1 mA current

evenly, as shown in the figure next.

4

5 k

2 0.7 10

5

1.86 mA

10 V

SEDRA-ISM: “P-CH04-031-053” — 2014/11/12 — 17:25 — PAGE 11 — #3

Chapter 4–12

(b)

(c)

10 V

3 V

5 k

ID2

I0

V

0.7 V

Cutoff

I

V

10 k

ID2

10 k

3 V

10 V

V = 3 − 0.7 = 2.3 V

10 − (−10) − 0.7

= 1.29 mA

15

VD = −10 + 1.29 (10) + 0.7 = 3.6 V

ID2 =

I=

2.3 + 3

= 0.53 mA

10

(d)

3 V

4.41

(a)

I

Cutoff

3 V

V

10 k

V

3 V

I

I =0A

V = −3 V

3 V

V = −3 + 0.7 = −2.3 V

4.42

3 + 2.3

10

= 0.53 mA

(a)

I=

Cutoff

1 V

(b)

D1

3 V

2 V

10 k

V

D2

2 k

V

Cutoff

3 V

I

V = 2 − 0.7

3 V

I =0A

V = 3 − I (10) = 3 V

= 1.3 V

1.3 − (−3)

I=

2

= 2.15 mA

SEDRA-ISM: “P-CH04-031-053” — 2014/11/12 — 17:25 — PAGE 12 — #4

I

Chapter 4–13

(b) See analysis on Fig. (b).

(b)

3 V

I = 0.133 mA

V =0V

I

2 k

4.44

1 V

D1

2 V

10 10 5 k 0.7 V V

V

I

10

5

10 10

2.5 V

D2

Cutoff

20 k

V = 1 + 0.7 = 1.7 V

(a)

3 − 1.7

= 0.65 mA

I=

2

5 k

4.43

V 5 k

0 mA

+3V

ID2

12 k

(b)

I0

1.5 V

2.5 V

D1

ID2

Cutoff

(a) I =

2.5 − 0.7

= 0.072 mA

5 + 20

ON 0.7 V

D2

V

V = 0.072 × 20 = 1.44 V

6 k

I =0

(b) The diode will be cut off, thus

V = 1.5 − 2.5 = −1 V

(a)

3 V

4.45

3V

30.7

0.383 mA

6

vI R

6 k

0.7 V

I 0.383 0.25

0.133 mA

ON

iD

v I ,peak − 0.7

≤ 40 mA

R

√

120 2 − 0.7

R≥

= 4.23 k

40

√

Reverse voltage = 120 2 = 169.7 V.

iD,peak =

D2

D1

ON

0(3)

12

0.25 mA

V0V

12 k

3 V

The design is essentially the same since the

supply voltage 0.7 V

(b)

(a) ID2 =

3 − 0.7 − (−3)

= 0.294 mA

12 + 6

V = −3 + 0.294 × 6 = −1.23 V

Check that D1 is off: Voltage at the anode of

D1 = V + VD2 = −1.23 + 0.7 = −0.53 V which

keeps D1 off.

4.46 Use the exponential diode model to find the

percentage change in the current.

iD = IS ev /VT

iD2

= e(V2 −V1 )/VT = ev /VT

iD1

For +5 mV change we obtain

SEDRA-ISM: “P-CH04-031-053” — 2014/11/12 — 17:25 — PAGE 13 — #5

Chapter 4–14

iD2

= e5/25 = 1.221

iD1

For a parallel combination of 10 diodes,

equivalent resistance, Req , is

% change

1.221 − 1

iD2 − iD1

× 100 =

× 100

=

iD1

1

= 22.1%

For –5 mV change we obtain

iD2

= e−5/25 = 0.818

iD1

% change =

0.818 − 1

iD2 − iD1

× 100

× 100 =

iD1

1

= −18.1%

2.7

= 0.27 10

If there is a single diode conducting all the 0.1 A

current, the connection resistance needed for the

single diode will be = 0.27 − 0.25 = 0.02 .

Req =

4.48 The dc current I flows through the diode

VT

giving rise to the diode resistance rd =

and

I

the small-signal equivalent circuit is represented

by

Rs

Maximum allowable voltage signal change when

the current change is limited to ±10% is found as

follows:

The current varies from 0.9 to 1.1

iD2

= eV /VT

iD1

For 0.9, V = 25 ln (0.9) = −2.63 mV

For 1.1, V = 25 ln (1.1) = +2.38 mV

For ±10% current change the voltage signal

change is from –2.63 mV to +2.38 mV

4.47

0.1 A

rd

vs

vo

rd

VT /I

VT

= vs

= vs

VT

rd + RS

VT + IRS

+ RS

I

25 mV

Now, v o = 10 mV ×

25 mV + 103 I

vo = vs ×

I

vo

1 mA 0.24 mV

0.1 mA 2.0 mV

1 μA

9.6 mV

For v o =

Ten diode connected in parallel and fed with a

total current of 0.1 A. So the current through each

0.1

diode =

= 0.01 A

10

Small signal resistance of each diode

1

0.025

vs = vs ×

2

0.025 + 103 I

⇒ I = 25 μA

4.49 As shown in Problem 4.48,

25 mV

VT

= 2.5 =

=

iD

0.01 A

VT

0.025

vo

=

=

vi

VT + RS I

0.025 + 104 I

Equivalent resistance, Req , of 10 diodes connected

in parallel is given by

Here RS = 10 k

2.5

= 0.25 Req =

10

If there is one diode conducting 0.1 A current,

then the small signal resistance of this diode

(1)

The current changes are limited ±10%. Using

exponential model, we get

iD2

= ev /VT = 0.9 to 1.1

iD1

iD2

and here

v = 25 × 10−3 ln

iD1

25 mV

= 0.25 0.1 A

This value is the same as of 10 diodes connected

in parallel.

For 0.9, v = −2.63 mV

If 0.2 is the resistance for making connection,

the resistance in each branch

= rd + 0.2 = 2.5 + 0.2 = 2.7 The variation is –2.63 mV to 2.38 mV for ±10%

current variation. Thus the largest symmetrical

output signal allowed is 2.38 mV in amplitude. To

=

For 1.1, v = 2.38 mV

SEDRA-ISM: “P-CH04-031-053” — 2014/11/12 — 17:25 — PAGE 14 — #6

Chapter 4–15

obtain the corresponding input signal, we divide

this by (v o /v i ):

vˆs =

2.38 mV

v o /v i

(2)

Now for the given values of v o /v i calculate I

and v̂ S using Equations (1) and (2)

vo

vi

0.5

0.1

0.01

0.001

I = 500 μA,

I = 600 μA,

I = 900 μA,

I in mA v̂ s in mV

I = 990 μA,

0.0025

0.0225

0.2475

2.4975

I = 1 mA

4.76

23.8

238

2380

vo

vi

vo

vi

vo

vi

vo

vi

vo

vi

I = 100 μA,

= 1000 μA,

= 100 × 10−3 = 0.1 V/V

= 500 × 10−3 = 0.5 V/V

= 600 × 10−3 = 0.6 V/V

= 900 × 10−3 = 0.9 V/V

= 990 × 10−3 = 0.99 V/V

vo

= 1000 × 10−3 = 1 V/V

vi

4.51

4.50

I

1 mA C

2

vo

D1

C1

D1

D2

D3

vi

vo

I

vi

R

D2

When both D1 and D2 are conducting, the

small-signal model is

D4

I

rd1

vi

vo

rd2

a. The current through each diode is

where we have replaced the large capacitors C1

and C2 by short circuits:

VT

rd 2

I

vo

1

m

−I

=

=

=

VT

VT

vi

rd 1 + rd 2

1m

+

I

1m−I

Thus

vo

= I,

vi

R

R

vo

=

=

vi

R + (2rd 2rd )

R + rd

rd

where I is in mA

vo

=0

vi

vo

= 1 × 10−3 = 0.001 V/V

vi

vo

= 10 × 10−3 = 0.01 V/V

I = 10 μA,

vi

I = 1 μA,

2VT

VT

0.05

=

=

I

I

I

2

From the equivalent circuit

rd =

I

Now I = 0 μA,

I

:

2

0 μA

∞

1 μA 50 k

10 μA 5 k

100 μA 500 1 mA

50 10 mA

5

vo

vi

0

0.167

0.667

0.952

0.995

0.9995

SEDRA-ISM: “P-CH04-031-053” — 2014/11/12 — 17:25 — PAGE 15 — #7

10 k

Chapter 4–16

rd

rd

From the results of (a) above, for I = 1 mA,

v o /v i = 0.995; thus the maximum input signal

will be

vo

vI

rd

rd

R

10 k

Equivalent Circuit

b. For signal current to be limited to ±10% of I (I

is the biasing current), the change in diode

voltage can be obtained from the equation

v̂ i = v̂ o /0.995 = 1/0.995

= 1.005 V

The same result can be obtained from the figure

above where the signal across the two series

diodes is 5 mV, thus

v̂ i = v̂ o + 5 mV = 1 V + 5 mV = 1.005 V. See

also the figure below.

iD

= eVD /V T = 0.9 to 1.1

I

v D = −2.63 mV to +2.32 mV

±2.5 mV

so the signal voltage across each diode is limited

to 2.5 mV when the diode current remains within

10% of the dc bias current.

∴ v o = 10 − 2.5 − 2.5 = 5 mV

and i =

5 mV

= 0.5 μA

10 k

2.5

mV

2.5

mV

4.52

i

I

vo

10 mV R

2.5

mV

10 k

D1

2.5

mV

The current through each diode

vI

i2

0.5

μA = 0.25 μA

=

2

The signal current i is 0.5 μA, and this is 10% of

the dc biasing current.

D2

i1

i3

v1

v3 v

2

v4 D3

iO

vO

i4 R 10 k

D4

I

∴ DC biasing current I = 0.5 × 10 = 5 μA

c. Now I = 1 mA.

∴ ID = 0.5 mA

Maximum current derivation 10%.

0.5

= 0.05 mA

∴ id =

10

and i = 2id = 0.1 mA.

I = 1 mA

Each diode exhibits 0.7 V drop at 1 mA current.

Using diode exponential model we have

i2

v 2 − v 1 = VT ln

i1

= 0.1 × 10

and v 1 = 0.7 V, i1 = 1 mA

i

⇒ v = 0.7 + VT ln

1

=1V

= 700 + 25 ln(i)

∴ Maximum v o = i × 10 k

SEDRA-ISM: “P-CH04-031-053” — 2014/11/12 — 17:25 — PAGE 16 — #8

Chapter 4–17

Calculation for different values of v O :

v O = 0, iO = 0, and the current I = 1 mA divide

equally between the D3 , D4 side and the D1 , D2

side.

For I = 0.5 mA, the output will saturate at

0.5 mA ×10 k = 5 V.

vo (V )

I

= 0.5 mA

2

10

v = 700 + 25 ln(0.5) 683 mV

5

i1 = i2 = i3 = i4 =

v 1 = v 2 = v 3 = v 4 = 683 mV

5.68

10.7

v1 (V)

5

v I = −v 1 + v 3 + v O = −683 + 683 + 0 = 0 V

For v O = 1 V, iO =

I 0.5 mA

10.7 5.68

From the circuit, we have

I 1 mA

1

= 0.1 mA

10 k

Because of symmetry of the circuit, we obtain

i3 = i2 =

I

iO

+

= 0.5 + 0.05 = 0.55 mA and

2

2

4.53 Representing the diode by the small-signal

resistances, the circuit is

i4 = i1 = 0.45 mA

rd

i2

v 3 = v 2 = 700 + 25 ln

= 685 mV

1

i4

= 680 mV

v 4 = v 1 = 700 + 25 ln

1

vO

(V)

iO

i3 = i2 i4 = i1 v 3 = v 2 v 4 = v 1

(mA) (mA) (mA) (mV)

(mV)

vi

v I = −v 1 +

v 3 + v O (V)

0.5

0.5

683

683

0

+1

0.1

0.55

0.45

685

680

1.005

+2

0.2

0.6

0.4

∼ 687

677

2.010

+5

0.5

0.75

0.25

∼ 693

665

5.028

+9

0.9

0.95

0.05

∼ 699

∼ 625

9.074

0.995

0.005

∼ 700

568

10.09

9.99 0.999 0.9995 0.0005 ∼ 700

510

10.18

10

0

10.7

1

0

700

vo

VT

rd ID

0

1

C

0

+ 9.9 0.99

v I = −v 1 + v 2 + v O = −0.680

+0.685 + 1 = 1.005 V

Similarly, other values are calculated as shown in

the table. The largest values of v O on positive and

negative side are +10 V and −10 V, respectively.

This restriction is imposed by the current

I = 1 mA

A similar table can be generated for the negative

values. It is symmetrical.

For v I > +10.7, v O will be saturated at +10 V

and it is because I = 1 mA. Similarly, for

v I < −10.7 V, v O will be saturated at −10 V.

Vo

=

Vi

1

sC

1

rd +

sC

=

1

1 + sCrd

1

Vo

=

Vi

1 + jωCrd

Phase shift = −tan−1

ωCrd

1

VT

= −tan−1 ωC

I

For phase shift of −45◦ , we obtain

−45 = −tan−1 2π × 100 × 103 × 10

0.025

× 10−9 ×

I

⇒ I = 157 μA

Now I varies from

157

μA to 157 × 10 μA

10

Range is 15.7 μA to 1570 μA

Range of phase shift is −84.3◦ to −5.71◦

SEDRA-ISM: “P-CH04-031-053” — 2014/11/12 — 17:25 — PAGE 17 — #9

Chapter 4–18

4.55

4.54

V

V

R

IL

R

VO

VO

VO

IL

(a)

=

VO

rd

=

=

+

V

R + rd

VT /I

VT

R+

I

Small-signal model

VT

IR + VT

(a) From the small-signal model

V + − 0.7

V + − VO

=

.

For no load, I =

R

R

∴

rd

R

VO = −I L (rd R)

VO

= − (rd R)

IL

VT

VO

=

V +

VT + (V + − 0.7)

(b) At no load, ID =

R

rd =

V

rd

VO

VO

mr d

mVT

=

=

mr d + R

mVT + IR

V +

mVT

=

mVT + (V + − 0.7m)

(c) For m = 1

VO

VT

=

= 1.75 mV/V

V +

VT + V + − 0.7

For m = 4

=−

1

ID

ID

+

V + − 0.7 VT

=−

VT

×

ID

=−

V + − 0.7

VT

×

VT + V + − 0.7

ID

For

1

VT

+1

V + − 0.7

mV

VO

≤5

IL

mA

V + − 0.7

5 mV

VT

×

≤

ID

VT + V + − 0.7

mA

mV

15 − 0.7

25

≤5

×

ID

mA

0.025 + 15 − 0.7

i.e.,

ID ≥ 4.99 mA

ID 5 mA

R=

VO

mVT

=

= 8.13 mV/V

V +

mVT + 15 − m × 0.7

VT

ID

VO

1

= − (rd R) = −

1

1

IL

+

rd

R

Small-signal model

(b) If m diodes are in series, we obtain

V + − 0.7

R

15 − 0.7

V + − 0.7

=

ID

5 mA

R = 2.86 k

SEDRA-ISM: “P-CH04-054-069” — 2014/11/12 — 15:21 — PAGE 18 — #1

Chapter 4–19

Diode should be a 5-mA unit; that is, it conducts

5 mA at VD = 0.7 V, thus 5 × 10−3 = IS e0.7/0.025 .

⇒ IS = 3.46 × 10−15 A

(c) For m diodes connected in series we have

ID =

So now

=−

=−

=−

I = ID + IL = 7.39 mA + 1 mA

= 8.39 mA

∴R=

V + − 0.7m

R

and rd =

IL = 1.5/1.5 = 1 mA

5 − 1.5

= 417 8.39 mA

Use a small-signal model to find voltage VO

when the value of the load resistor, RL , changes:

VT

ID

VO

1

= −(R mrd ) = −

1

1

IL

+

R mrd

1

ID

ID

+

V + − 0.7m mVT

rd =

VT

0.025

= 3.4 =

ID

7.39

When load is disconnected, all the current I flows

through the diode. Thus

ID = 1 mA

VO = ID × 2rd

mV T

ID

mV T

+1

V + − 0.7m

= 1 × 2 × 3.4

V + − 0.7m

mVT

ID V + − 0.7m + mVT

= 6.8 mV

With RL = 1 k,

IL 4.56

1.5 V

= 1.5 mA

1

IL = 0.5 mA

5 V

ID = −0.5 mA

I

VO = −0.5 × 2 × 3.4

R

= −3.4 mV

IL

Vo

ID

With RL = 750 ,

IL RL

1.5

= 2 mA

0.75

IL = 1 mA

ID = −1 mA

VO = −1 × 2 × 3.4

Diode has 0.7 V drop at 1 mA current

VO = 1.5 V when RL = 1.5 k

= −6.8 mV

With RL = 500 ,

ID = IS eV /V T

1.5

= 3 mA

0.5

1 × 10−3 = IS e0.7/0.025

IL ⇒ IS = 6.91 × 10−16 A

IL = 2.0 mA

Voltage drop across each diode =

1.5

= 0.75 V.

2

ID = −2.0 mA

∴ ID = IS eV /V T = 6.91 × 10−16 × e0.75/0.025

VO = −2 × 2 × 3.4

= 7.38 mA

= −13.6 mV

SEDRA-ISM: “P-CH04-054-069” — 2014/11/12 — 15:21 — PAGE 19 — #2

Chapter 4–20

4.58

4.57

5 V

I

I

R 200 vO 1.5 V VO

IL

ID

D1

ID

D2

IL

RL 150 VO

IL varies from 2 to 7 mA

To supply a load current of 2 to 7 mA, the current

I must be greater than 7 mA. So I can be only

10 mA or 15 mA.

Now let us evaluate VO for both 10-mA and

15-mA sources. For the 10-mA source:

(a) Iteration #1:

VD = 0.7 V

VO = 2VD = 1.4 V

IL =

VO

1.4

= 9.33 mA

=

RL

0.15

Since IL varies from 2 to 7 mA, the current ID will

varry from 8 to 3 mA.

I=

Correspondingly, the voltage across each diode

changes by VD where

Iteration #2:

3

= eVD /VT

8

3

= −24.5 mV

⇒ VD = 25 ln

8

and the output voltage changes by

VO = 2 × VD = −49 mV

With I = 15 mA, the diodes current changes from

13 to 8 mA. Correspondingly, the voltage across

each diode changes by VD where

8

= eVD /VT

13

5 − 1.4

5 − VO

=

= 18 mA

R

0.2

ID = I − IL = 18 − 9.33 = 8.67 mA

8.67

= 0.696 V

VD = 0.7 + 0.025 ln

10

VO = 1.393 V

IL = 9.287 mA

5 − 1.393

= 18.04 mA

0.2

ID = 18.04 − 9.287 = 8.753 mA

I=

Iteration #3:

8.753

= 0.697

VD = 0.7 + 0.025 ln

10

VO = 1.393 V

IL = 9.287

8

⇒ VD = 25 ln

= −12.1 mV

13

I = 18.04 mA

and the output voltage changes by

No further iterations are necessary and

VO = 2 × VD = −24.2 mV

VO = 1.39 V

which is less than half that obtained with the

10-mA supply. Thus, from the point of view of

reducing the change in VO as IL changes, we

choose the 15-mA supply. Note, however, that the

price paid is increased power dissipation.

ID = 8.753

(b) With no load:

Iteration #1:

VD = 0.7 V

VO = 1.4 V

SEDRA-ISM: “P-CH04-054-069” — 2014/11/12 — 15:21 — PAGE 20 — #3

Chapter 4–21

5 − 1.4

= 18 mA

0.2

ID = I = 18 mA

I=

Iteration #2:

18

= 0.715 V

VD = 0.7 + 0.025 ln

10

VO = 1.429 V

ID = 17.18 mA

Iteration #3:

17.18

= 0.714 V

VD = 0.7 + 0.025 ln

10

VO = 1.428 V

No further iterations are needed and

I = 17.85 mA

ID = 17.85 mA

VO = 1.43 V

Iteration #3:

(e) From the above we see that as VSupply changes

from 5 V to 3.232 V (a change of −35.4%) the

output voltage changes from 1.39 V to 1.29 V (a

change of −7.19%).

17.85

= 0.714 V

VD = 0.7 + 0.025 ln

10

VO = 1.43 V

I = 17.86 mA

ID = 17.86 mA

No further iterations are warranted and

VO = 1.43 V

(c) VO = 1.39 − 0.1 = 1.29 V

1.29

= 8.6 mA

0.15

1.29

= 0.645 V

VD =

2

IL =

As VSupply changes from 5 V to 6.786 V (a change

of +35.4%) the output voltage changes from 1.39

V to 1.43 V (a change of +2.88%).

Thus the worst-case situation occurs when VSupply

is reduced, and

Percentage change in VO per 1% change in

7.19

= 0.2%

VSupply =

35.4

4.59 VZ = VZ0 + IZT rz

ID = 10 × e(0.645−0.7)/0.025

(a) 10 = 9.6 + 0.05 × rz

= 1.11 mA

⇒ rz = 8 I = IL + ID = 8.6 + 1.11 = 9.71 mA

For IZ = 2IZT = 100 mA,

VSupply = VO + IR = 1.29 + 9.71 × 0.2

VZ = 9.6 + 0.1 × 8 = 10.4 V

= 3.232 V

which is a reduction of 1.768 V or −35.4%.

(d) For VSupply = 5 + 1.786 = 6.786 V,

P = 10.4 × 0.1 = 1.04 W

(b) 9.1 = VZ0 + 0.01 × 30

Iteration #1:

⇒ VZ0 = 8.8 V

VD = 0.7 V

At IZ = 2IZT = 20 mA,

VO = 1.4 V

VZ = 8.8 + 0.02 × 30 = 9.4 V

IL = 9.33 mA

P = 9.4 × 20 = 188 mW

6.768 − 1.4

= 26.84

I=

0.2

ID = I − IL = 26.84 − 9.33 = 17.51 mA

Iteration #2:

(c) 6.8 = 6.6 + IZT × 2

⇒ IZT = 0.1 A

17.51

= 0.714 V

VD = 0.7 + 0.025 ln

10

At IZ = 2IZT = 0.2 A,

VO = 1.428 V

P = 7 × 0.2 = 1.4 W

IL = 9.52 mA

(d) 18 = 17.6 + 0.005 × rz

I = 26.70 mA

VZ = 6.6 + 0.2 × 2 = 7 V

⇒ rz = 80 SEDRA-ISM: “P-CH04-054-069” — 2014/11/12 — 15:21 — PAGE 21 — #4

Chapter 4–22

At IZ = 2IZT = 0.01 A,

4.63

VZ = 17.6 + 0.01 × 80 = 18.4 V

10 V

P = 18.4 × 0.01 = 0.184 W = 184 mW

(e) 7.5 = VZ0 + 0.2 × 1.5

I

⇒ VZ0 = 7.2 V

R

At IZ = 2IZT = 0.4 A,

VO VZ

VZ = 7.2 + 0.4 × 1.5 = 7.8 V

P = 7.8 × 0.4 = 3.12 W

IZ

IL

RL

4.60 (a) Three 6.8-V zeners provide 3 × 6.8 =

20.4 V with 3 ×10 = 30- resistance. Neglecting

R, we have

Load regulation = −30 mV/mA.

(a)

(b) For 5.1-V zeners we use 4 diodes to provide

20.4 V with 4 ×30 = 120- resistance.

Load regulation = −120 mV/mA

11 V

4.61

82 I

R

vS

VO VZ

8

vO

rZ

Small-signal model

VZ0

From the small-signal model we obtain

(b)

8

8

v O

=

=

v S

8 + 82

90

9 V

Now v S = 1.0 V.

8

8

v S =

× 1.0

∴ v O =

90

90

= 88.9 mV

I

R

4.62 VZ = VZ0 + IZT rZ

VO VZ

9.1 = VZ0 + 0.02 × 10

⇒ VZ0 = 8.9 V

At IZ = 10 mA,

0.5 mA

IL

RL

VZ = 8.9 + 0.01 × 10 = 9.0 V

At IZ = 50 mA,

VZ = 8.9 + 0.05 × 10 = 9.4 V

(c)

SEDRA-ISM: “P-CH04-054-069” — 2014/11/12 — 15:21 — PAGE 22 — #5

Chapter 4–23

To obtain VO = 7.5 V, we must arrange for

IZ = 10 mA (the current at which the zener is

specified).

4.64

9V±1V

Now,

R

VO

7.5

=

= 5 mA

RL

1.5

IL =

Thus

VO

I = IZ + IL = 10 + 5 = 15 mA

and

IZ

10 − 7.5

10 − VO

=

= 167 R=

I

15

When the supply undergoes a change VS , the

change in the output voltage, VO , can be

determined from

VO

(RL rz )

=

VS

(RL rz ) + R

1.5 0.03

= 0.15

=

(1.5 0.03) + 0.167

GIVEN PARAMETERS

VZ = 6.8V, rz = 5 IZ = 20 mA

For VS = +1 V (10% high), VO = +0.15 V

and VO = 7.65 V.

At knee,

For VS = −1 V (10% low), VO = −0.15 V

and VO = 7.35 V.

rz = 750 When the load is removed and VS = 11 V, we can

use the zener model to determine VO . Refer to

Fig. (b). To determine VZ0 , we use

VZ = VZ0 + IZT rz

7.5 = VZ0 + 0.01 × 30

⇒ VZ0 = 7.2 V

From Fig. (b) we have

I=

11 − 7.2

= 19.3 mA

0.167 + 0.03

Thus

IZK = 0.25 mA

FIRST DESIGN: 9-V supply can easily supply

current

Let IZ = 20 mA, well above knee.

∴ R=

9 − 6.8

= 110 20

Line regulation =

=

rZ

VO

=

VS

rZ + R

5

5 + 110

= 43.5

mV

V

VO = VZ0 + Irz

SECOND DESIGN: limited current from 9-V

supply

= 7.2 + 0.0193 × 30 = 7.78 V

IZ = 0.25 mA

To determine the smallest allowable value of RL

while VS = 9 V, refer to Fig. (c). Note that

IZ = 0.5 mA, thus

VZ = VZK VZO − calculate VZ0 from

VZ = VZ0 + rZ IZT

VZ = VZK VZ0 = 7.2 V

6.8 = VZ0 + 5 × 0.02

I=

9 − 7.2

= 10.69 mA

0.167

IL = I − IZ = 10.69 − 0.5 = 10.19 mA

RL =

VO

7.2

=

= 707 IL

10.19

VO = 7.2 V

VZ0 = 6.7 V

∴R=

8 − 6.7

= 5.2 k

0.25

LINE REGULATION =

= 126

750

VO

=

VS

750 + 5200

mV

V

SEDRA-ISM: “P-CH04-054-069” — 2014/11/12 — 15:21 — PAGE 23 — #6

Chapter 4–24

If IL is reduced by 50%, then

4.65

VS 15 V 10%

I

I=

R

IL

15 − VO

0.3

VO − 8.74

0.04

IZ =

VO VZ

IZ

1 9.15

×

= 4.6 mA

2

1

IL =

15 − VO

VO − 8.74

=

+ 4.6

0.3

0.04

RL

⇒ VO = 9.31 V

which is an increase of 0.16 V. When the supply

voltage is low,

VS = 13.5 V

VZ = VZ0 + IZT rz

⇒ VZ0 = 8.74 V

and RL is at its lowest value, to maintain

regulation, the zener current must be at least equal

to IZK , thus

For IZ = 10 mA,

IZ = 0.5 mA

VZ = 8.74 + 0.01 × 40 = 9.14 V

VZ = VZK VZ0 8.74

9.14

= 9.14 mA

IL =

1 k

I=

9.1 = VZ0 + 0.009 × 40

I = IZ + IL = 10 + 9.14 = 19.14 mA

IL = I − IZ = 15.87 − 0.5 = 15.37 mA

15 − 9.14

= 306 R=

19.4

RL =

Select R = 300 15 − VO

0.3

Line regulation =

(1)

IL =

VO

1

(2)

IZ =

VO − VZ0

VO − 8.74

=

rz

0.04

(3)

Since I = IZ + IL , we can use (1)–(3) to obtain

VO :

VO − 8.74

15 − VO

=

+ VO

0.3

0.04

⇒ VO = 9.15 V

VO = VS

= ±1.5 ×

rz RL

(rz RL ) + R

(0.04 1)

(0.04 1) + 0.3

= ±0.17 V

VZ

8.74

= 589 =

IL

15.37

The lowest value of output voltage = 8.74 V

Denoting the resulting output voltage VO , we

obtain

I=

13.5 − 8.74

= 15.87 mA

0.3

170 mV

1.5 V

= 113 mV/V

Load regulation = −(rz R)

= −(40 300) = −35 mV/mA

Or using the results obtained in this problem:

For a reduction in IL of 4.6 mA, VO = +0.16 V,

thus

Load regulation = −

160

= −35 mV/mA

4.6

4.66 (a) VZT = VZ0 + rz IZT

10 = VZ0 + 7 (0.025)

⇒ VZ0 = 9.825 V

SEDRA-ISM: “P-CH04-054-069” — 2014/11/12 — 15:21 — PAGE 24 — #7

Chapter 4–25

(b) The minimum zener current of 5 mA occurs

when IL = 20 mA and VS is at its minimum of

20(1 − 0.25) = 15 V. See the circuit below:

25 V

VS 15 V

207 VZ

R

IL 0

20 mA

VO

IZmin 5 mA

IZ

RL

25 − VZ

207

207VZ = 207 (9.825) + 7 (25) − 7VZ

= 9.825 + 7 ×

R≤

15 − VZ0

20 + 5

⇒ VZ = 10.32 V

where we have used the minimum value of VS , the

maximum value of load current, and the minimum

required value of zener diode current, and we

assumed that at this current VZ VZ0 . Thus,

15 − 9.825 + 7

R≤

25

25 − 10.32

= 70.9 mA

0.207

PZ = 10.32 × 70.9

IZmax =

= 732 mW

4.67

≤ 207 .

∴ use R = 207 7

mV

(c) Line regulation =

= 33

207 + 7

V

±25% change in v S ≡ ± 5 V

vS vO

R

VO changes by ±5 × 33 = ±0.165 mV

±0.165

× 100 = ±1.65%

corresponding to

10

(d) Load regulation = − (rZ R)

Using the constant voltage drop model:

= −(7 207) = −6.77 ideal

VD

0.7 V

or –6.77 V/A

VO = −6.77 × 20 mA = −135.4 mV

corresponding to −

0.1354

× 100 = −1.35%

10

R

1 k

vS (e) The maximum zener current occurs at no load

IL = 0 and the supply at its largest value of

20 +

1

(20) = 25 V.

4

VZ = VZ0 + rZ IZ

vO

(a) v O = v S + 0.7 V,

v O = 0,

For v S ≤ − 0.7 V

for v S ≥ −0.7 V

SEDRA-ISM: “P-CH04-054-069” — 2014/11/12 — 15:21 — PAGE 25 — #8

Chapter 4–26

iD = IS ev D /V T

vO

0.7 V

0

iD

= e[v D −v D (at 1 mA)]/V T

iD (1 mA)

iD

v D − v D (at 1 mA) = VT ln

1 mA

v O /R

v D = v D (at 1 mA) + VT ln

1

vS

slope 1

vO = vS − vD

(b)

= v S − v D (at 1 mA) − VT ln

O

R

where R is in k.

vS

10 V

v vO

4.69

t

0.7 V

0.7 V 10 V

0.7 V

vS R 1 k vO

u

(c) The diode conducts at an angle

0.7

= 4◦ and stops

θ = sin−1

10

vS (V)

2.5

1.8

at π − θ = 176◦

Thus the conduction angle is π − 2θ

0.7

0

= 172◦ or 3 rad.

v O,avg =

−1

2π

π −θ

t1

(10 sin φ − 0.7) d φ

T

4

t2 T

2

T

θ

2.5

−1

[−10 cos φ − 0.7φ]πθ −θ

=

2π

= −2.85 V

First find t1 and t2

(d) Peak current in diode is

0.7

2.5

=

T

t1

4

⇒ t1 = 0.07 T

10 − 0.7

= 9.3 mA

1

(e) PIV occurs when v S is at its the peak and

v O = 0.

t2 =

PIV= 10 V

T

− t1

2

T

− 0.07 T

2

t2 = 0.43 T

=

4.68

D

vD vS R

vO

1

× area of shaded triangle

T

T

× (2.5 − 0.7) ×

− t1

4

1

× 1.8 × T

− 0.07

4

v O (ave.) =

=

1

T

=

1

T

= 0.324 V

SEDRA-ISM: “P-CH04-054-069” — 2014/11/12 — 15:21 — PAGE 26 — #9

t

Chapter 4–27

√

vˆO = 10 2 − VD = 13.44 V

4.70

Conduction starts at θ = sin−1

ideal 0.7 V

12 : 1

vS

10 Vrms

1 k vO

120 Vrms

60 Hz

√

vˆO = 10 2 − 0.7 = 13.44 V

2.84◦ = 0.05 rad

and ends at π − θ. Conduction angle =

π − 2θ = 3.04 rad in each half cycle. Thus the

fraction of a cycle for which one of the two

2(3.04)

diodes conduct =

× 100 = 96.8%

2π

Note that during 96.8% of the cycle there will be

conduction. However, each of the two diodes

conducts for only half the time, i.e., for 48.4% of

the cycle.

v O,avg =

Conduction begins at

√

10 2 sin θ = 0.7

0.7

θ = sin−1

= 2.84◦

√

10 2

1

π

iL,avg =

Conduction ends at π − θ .

4.72

12 : 1

D4

The diode conducts for

3.04

× 100 = 48.4% of the cycle

2π

1

2π

θ

8.3

= 8.3 mA

1 k

∴ Conduction angle = π − 2θ = 3.04 rad

v O,avg =

π−θ √

(10 2sinφ − 0.7)d φ

= 8.3 V

= 0.0495 rad

π −θ

0.7

√ =

10 2

10 Vrms

vs

120 Vrms

√

(10 2sinφ − 0.7) d φ

D1

R

1 k

D3

D2

VD 0.7 V

θ

√

Peak voltage across R = 10 2 − 2VD

√

= 10 2 − 1.4

= 4.15 V

v O,avg

iD,avg =

= 4.15 mA

R

= 12.74 V

4.71

vS

D1

6:1

10 2 V

1 k

vo

10 Vrms

120 Vrms

60 Hz

1.4 V

t

10 Vrms D2

θ = sin−1

1.4

√ = 5.68◦ = 0.1 rad

10 2

Fraction of cycle that D1 & D2 conduct is

vS , vO (V)

vs

vo

10 V

0.7 V

0 t

π − 2θ

× 100 = 46.8%

2π

Note that D3 & D4 conduct in the other half cycle

so that there is 2 (46.8) = 93.6% conduction

interval.

v O,avg =

2

2π

π−θ

√

(10 2sinφ − 2V D ) d φ

θ

SEDRA-ISM: “P-CH04-070-085” — 2014/11/12 — 11:17 — PAGE 27 — #1

Chapter 4–28

=

√

√

4.75 120 2 ± 10%: 20 2 ± 10%

4.73

⇒ Turns ratio = 6:1

√

20 2

vS =

± 10%

2

PIV= 2Vs − VD

√

20 2

× 1.1 − 0.7

=2×

2

= 30.4 V

π −θ

√

1

−12 2 cos φ − 1.4φ

θ

π

√

2(12 2 cos θ ) 1.4 (π − 2θ)

−

=

π

π

= 7.65 V

v O,avg

7.65

=

= 7.65 mA

iR,avg =

R

1

vS

vS

120 Vrms

R

vO

Using a factor of 1.5 for safety, we select a diode

having a PIV rating of approximately 45 V.

4.76 The circuit is a full-wave rectifier with

center tapped secondary winding. The circuit can

−

be analyzed by looking at v +

O and v O separately.

Refer to Fig. 4.24.

vS

vS

For VD Vs , conduction angle π, and

2

2

v O,avg = Vs − VD = Vs − 0.7

π

π

(a) For v O,avg = 10 V

π

× 10.7 = 16.8 V

2

√

120 2

Turns ratio =

= 10.1 to 1

16.8

(b) For v O,avg = 100 V

D1

D3

Vs =

vO

vS

vS

π

× 100.7 = 158.2 V

2

√

120 2

Turns ratio =

= 1.072 to 1

158.2

Vs =

D4

R

D2

4.74 Refer to Fig. 4.25

For 2VD Vs

2

2

Vs − 2VD = Vs − 1.4

π

π

(a) For VO,avg = 10 V

VO,avg =

2

· Vs − 1.4

π

π ∴ V̂s = 11.4

= 17.9 V

2

√

120 2

Turns ratio =

= 9.5 to 1

17.9

(b) For VO,avg = 100 V

10 V =

2

· Vs − 1.4

π

π = 159 V

⇒ Vs = 101.4

2

√

120 2

Turns ratio =

= 1.07 to 1

159

100 V =

v O, avg =

1

2π

(VS sinφ − 0.7) d φ = 12

2Vs

− 0.7 = 12

π

where we have assumed Vs 0.7 V and thus the

conduction angle (in each half cycle) is almost π .

=

Vs =

12 + 0.7

π = 19.95 V

2

SEDRA-ISM: “P-CH04-070-085” — 2014/11/12 — 11:17 — PAGE 28 — #2

Chapter 4–29

= 2VS − 0.7

(b) (i) Using Eq (4.30), we have the conduction

angle =

ωt ∼

= 2Vr / Vp − VD

2 × 0.1 Vp − 0.7

=

Vp − 0.7

√

= 0.2

= 39.2 V

= 0.447 rad

If choosing a diode, allow a safety margin by

moving a factor of 1.5, thus

∴ Fraction of cycle for

Thus voltage across secondary winding

= 2VS 40 V

Looking at D4 ,

PIV= VS − VO−

= VS + (VS − 0.7)

conduction =

PIV 60 V

= 7.1%

4.77

0.447

× 100

2π

(ii) ωt 2 × 0.01

R

12 : 1

120 Vrms

10 Vrms VS

R

1 k

C vO

Vp

Vr

VpVD

Vp − 0.7

= 0.141 rad

Vp − 0.7

0.141

× 100 = 2.24%

2π

(c) (i) Use Eq (4.31):

⎛

⎞

2 Vp − VD

⎠

iD,avg = IL ⎝1 + π

Vr

Fraction of cycle =

2 Vp − VD

v O,avg

1+π

=

R

0.1 Vp − VD

2

12.77

1

+

π

=

0.1

103

= 192 mA

√

13.37 1 + π 200

3

10

T

(i) Vr ∼

[Eq. (4.28)]

= Vp − VD

CR

T

0.1 Vp − VD = Vp − VD

CR

1

= 166.7 μF

C=

0.1 × 60 × 103

(ii) iD,avg =

(ii) For

2

12.77

1 + 2π

=

0.1

103

Vp − VD T

Vr = 0.01 Vp − VD =

CR

C = 1667 μF

1

(a) (i) v O, avg = Vp − VD − VΓ

2

√

√

1

= 10 2 − 0.7 −