Hspice Training Davan Tech

advertisement

IDEC Star-HSPICE

â

âyy

Welcome To

Star-HSPICE Training

DAVAN TECH Co.

1

Contents

θ

Day 1

Session 1 : Overview

Session 2 : Fundamentals

Session 3 : Analysis Types

θ

Day 2

Session 1 : Controls & Options

Session 2 : Simulation Controls & Convergence

Session 3 : Advanced Input File Elements

Session 4 : Introduction to Statistical Simulation

2

Page 1

1

Day 1 : Session 1

3

SPICE ? ! !

SPICE :== Simulation Program with Integrated Circuit Emphasis

A Powerful, general-purpose circuit analysis program

ν Developed By U.C. Berkeley in the Late 1960’s

ν Originally Christened CANCER by Lawrence Nagel (Ph.D. thesis)

Was limited to C, R, L, Bipolar diodes and transistors.

100 node maximum

ν SPICE 1, 1971

Added MOS, JFET’s, Gummel-Poon, subcircuits

ν SPICE 2, 1975

17,000 lines of FORTRAN coded

Added “E” and “G” elements

Improved both speed and accuracy of transient analysis

Released as version G.6 in 1983

ν SPICE 3

A superset of 2G.6, re-written in C to include:

Multiple netlists, poly. caps and inductors, inline resistor TC‘s,

Temp sweep analysis, topology checking, more.

4

Page 2

2

History of Star-HSPICE

1981 Introduced

1984 Capable of 50,000 node analysis

1985 Labs established

1987 Optimization added

1988 Speed increased by 10 -100 X

capacity increased to 100,000 transistors

1989 Inroduced mixed signal analysis

P.C. version marketed

1990 Included lossy transmission line analysis

1992 Major improvements in speed, accuracy and convergence

1993 Several improvements, including auto-memory allocation

1995 Improvements in speed and versatility

1996 FlexLM, CD install, better speed and convergence,

major fixes in lossy transmission Line models,

BSIM3v3 and Mos9 MOS models added

1997 Multiconductor lossy frequency-dependent transmission

line model(W element) added

5

SPICE Capabilities

ν General purpose circuit simulator which performs many kind of analysis of a circuit

ν

Nonlinear DC analysis : determines the DC operating point of the circuit

ν

Nonlinear transient : determines the response as a function of time over a specified time interval

ν

Linear AC analysis : calculates the frequency response of the circuit

ν

Small signal DC transfer function analysis of a circuit from a specified input to a specified o/p

ν

ETC : DC small signal sensitivity, distortion, Noise, fourier, temperature, statistical analysis etc.

ν Contains built-in models

ν

Passive elements : resistors,capacitors,inductors, transmission lines, mutual inductor etc

ν

Active elements : Diode, BJT, JFET, MESFET,MOSFET,SOI, etc

ν

Independent Sources, dependent Sources (VCVS:E,VCCS:G,CCVS:H,CCCS:F), etc

6

Page 3

3

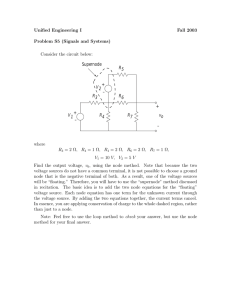

Design Process Tool Suite

Edit Layout(Apollo,LTL)

Edit Spice

input files (vi, emacs)

Extract spice netlist

from layout(Star-RC)

Level1,2,3,

BSIM1,2,3,

Level28,MOS9,

VBIC,etc

Process

Model

Edit Schematic

(COMPASS)

Mixed

A/D

Circuit Verification

Star-sim Star-Hspice

Process model Creation

Avanlab(SUPREME,Raphael)

Extract spice netlist

from schematic

Logic Verification

Polaris,COMPASS

Synthesis

Verilog,

Synthesis

Synopsys,

Libs

viewlogic,

vital, etc

Logic

Libs

Display & Analysis

(Avanwave/Hsplot)

Logic Library creation

Star-MTB

7

Avant! Provides ...

Power

Function

Star-TIME

Delay & Power

Models

Star-SIM

Table Models

Star-HSPICE

XO

Transistor

Models

Star-MTB

TCAD to ECAD

Schematic to netlist

Timing

Pre-Layout to Post Layout

Apollo

Polaris

Layout to netlist

Milkyway

Device &

Interconnect

Measurement

Star-RC

or GDS II

Star-POWER

Physical Device

& Interconnect

Modeling

Silicon Blueprint

TCAD Products

8

Page 4

4

Avant! Simulation Technology Roadmap

Increasing Speed

Star-TIME

Event

Driven

Multirate

Timestep

Global Timestep

w/ Partitioning

Spice

Algorithm

ED

AED

Star-SIM

SimLink

MR (logic)

HspiceLink

Star-Hspice

Equation

Model

ACS

ACS_EXP

ACS_Analog

Hspice XO

Analog

Table Model

Digital

Table Model

Switch

Model

Decreasing

Accuracy

9

Day 1 : Session 2

10

Page 5

5

Fundamentals

θ

NOTE: Volume # and Page # to right of important points

throughout presentation.

How to Use

Files & Suffixes

Netlist Structure

Naming Conventions

Units & Scale Factors

Components

9 Passive

9 Active

Sources

9 Independent

9 Dependent

11

Star-HSPICE fits into your production design flow

OUTPUT OPTIONS

SPICE

voltage

source

statements

Stimulus

Star-HSPICE

Netlist

Star-HSPICE

Third-party

tools

Voltage &

Current

Display Avanwaves

XP

Display Tool

Output

Listing

file

Circuit

Models

HSPICE

models

12

Page 6

6

How to Use : User Setup

θ

UNIX commands shown in BOLD Italic

UNIX

Add at END of your local .cshrc file:

source <installpath>/97/bin/cshrc.meta

another e.g.

source /usr/bin/97.4/bin/cshrc.meta

Edit your local .cshrc file

9 cshrc.meta is provided.

θ

à

Sets up environment variables: $installdir & $LM_LICENSE_FILE & $META_FLEX

/usr/meta/97)

à

Also points to man pages for hspice®, hsplot, and gsi.

PC

(e.g.

HSPICE® environments need to be set

before the MS Windows setup in the

autoexec.bat file

autoexec.bat

9 Installation automatically adds

à

set INSTALLDIR= c:\meta\97\ and METAHOME=c:\path\97\

à

set LM_LICENSE_FILE=c:\meta\97\license.dat

à

Adjusts path. (Places METAHOME at beginning of search path).

Config.sys

See PC Release Note.

9 FILES & BUFFERS settings

13

How to Use : Invocation(1) - unix

UNIX commands shown in BOLD Italic

θ

Hspice input file editing using editor ( vi editor, emacs, .. )

θ

The command (a script), HSPICE®, will determine the architecture and select the

correct executable.

hspice script

Vol. 1, p. 2-8

9 DO NOT make a local copy of the hspice script. (Make sure the hspice being executed is in the

$installdir/bin directory of the latest release).

à

The unix command, “which hspice”, should return: /<path>/<releasename>/bin/hspice

• e.g. /usr/meta/97/bin/hspice

θ

Hspice simulation on Command line

hspice <infile> > & <outfile.lis>

9 hspice demo.sp > demo.lis

9 hspice -i demo.sp -o /tmp/demo.lis

à

For use when input file and output files are in different directories.

14

Page 7

7

How to Use : Invocation(2) - unix

θ

UNIX commands shown in BOLD Italic

Hspice simulation on Prompt mode

hspice {return}

9 Enter input file name:

9 Enter output file name [demo.lis]:

To kill a job...

9 HSPICE versions are:

ps to determine unix PID

à

1 ==> /usr/meta/97

à

2 ==> /usr/meta/97.2

kill -9 <PID>

9 Which HSPICE version to run (Enter # [1 default]):

9 How much memory needed for this run?

9 Run HSPICE job at a lower priority? (y,n) [n]

θ

Ignored from H93a onward.

Viewing Hspice results

To review the result, use vi editor

9 vi demo.lis

To review the graphic results

9 awaves demo.sp

15

How to Use : Environment issues - unix

θ

Environment Limits

Large designs are affected by system limits.

On Sun, enter “limit”

cputime

filesize

datasize

stacksize

coredumpsize

memoryuse

descriptors

unlimited

unlimited

unlimited

8192 kbytes

unlimited

unlimited

64

For designs with a large number of output files..

increase this number.

enter: limit descriptors 128

θ

Configuration Files:

Meta.cfg - Defines terminal type (for gsi and hsplot) and printer types.

9 $installdir/meta.cfg

9 Searches first in home directory, then $installdir.

<design>.cfg - Remembers setups for last gsi session.

16

Page 8

8

How to Use : License Types - unix

θ

Multi-Job Node Locked

9 Single or multiple tokens locked to a single hostid.

9 One job per token.

9 FLEXlm license file requred, license.dat.

θ

Floating

9 Single or multiple tokens “float” to any workstation within the machine class.

9 One job per token.

9 Requires license server (FLEXlm license).

17

How to Use : Common Installation Issues

θ

Not using the latest hspice script. (which hspice)

“command not recognized” (improper installation!)

User .cshrc files not pointing to the latest release.

Tokens not being granted.

θ

Examine: .lis file as well as $installdir/FLEX.log

Insufficient system resources (examine .lis file):

θ

θ

θ

Increase /tmp directory

Increase swap space

9 (swap must be all on ONE single disk partition).

θ

θ

Increase “limit” (limit datasize unlimited)

Out of date permit file.

Trying to run a product on a machine that is not authorized.

Examine $installdir/license.dat or run install

Review Manual

Vol. 1, Ch 1.

18

Page 9

9

HSPICE Input/Output Files & Suffixes

HSPICE Input

θ

hspice design > design.lis

design configuration

.cfg

or...

initialization

hspice.ini

hspice design.ckt > design.out

Vol 1, p. 3-2

Run time status

run status

.st0

output listing

.lis

initial condition

.ic

.print & .plot

measure output

.m*# (e.g. .mt0,mt1,.)

.op (operating point)

Analysis data, transient

.tr# (e.g. .tr0,tr1,.)

Analysis data, dc

.sw# (e.g. .sw0,sw1,.)

.lis file contains results of:

Analysis data, ac

.ac# (e.g. .ac0,ac1,.)

Plot file

.gr# (e.g. .gr0, gr1,..)

AvanWaves/HSPLOT Input

θ

Typical Invocations:

.sp

HSPICE Output

θ

Vol. 1, p. 2-11

input netlist

.options (results)

Depends on .Option Post

Note: # is either a sweep or a hardcopy file number.

all Analysis data files

19

Files & Suffixes The .ST0 file

**** H S P I C E -- 95x1 (940924) 20:09:20 94/10/17 pc

Input File: lab1c.sp

lic: Attempting to get license from local permit file

lic: local license file path: C:\META\H93A\permit.hsp

lic: Evaluation expires 941231

lic: License for hspice granted from local permit file C:\META\H93A\permit.hsp

init: begin read circuit files, cpu clock= 1.43E+00

option list

option node

option post

init: end read circuit files, cpu clock= 1.48E+00 memory= 14 kb

init: begin check errors, cpu clock= 1.48E+00

init: end check errors, cpu clock= 1.54E+00 memory= 13 kb

init: begin setup matrix, pivot= 10 cpu clock= 1.54E+00

establish matrix -- done, cpu clock= 1.54E+00 memory= 16 kb

re-order matrix -- done, cpu clock= 1.54E+00 memory= 16 kb

init: end setup matrix, cpu clock= 1.54E+00 memory= 23 kb

dcop: begin dcop, cpu clock= 1.54E+00

dcop: end dcop, cpu clock= 1.59E+00 memory= 23 kb tot_iter=

3

sweep: tran tran0 begin, stop_t= 2.00E-06 #sweeps= 201 cpu clock= 1.59E+00

tran: time= 2.27333E-07 tot_iter= 22 conv_iter= 11

tran: time= 4.27333E-07 tot_iter= 32 conv_iter= 16

tran: time= 1.81438E-06 tot_iter= 136 conv_iter= 68

tran: time= 2.00000E-06 tot_iter= 150 conv_iter= 75

sweep: tran tran0 end, cpu clock= 3.13E+00 memory= 23 kb

>info:

***** hspice job concluded

Several timesteps

removed to fit on page

20

Page 10

10

Netlist Structure : Common Rules

θ

Free Format type

θ

First line must be a title and the netlist must be ended with .END card

θ

One main program and 1 or more optional submodules (.alter)

θ

+ in the first column is line continuation character

θ

Control commands are started with .(period)

θ

High level call statements can restructure netlist file modules

.INCLUDE

.LIB

θ

Can do macro modeling using

.SUBCKT

.MACRO

θ

Calls to external data files

θ

Last definition wins for parameters and options

21

Netlist Structure: Topology Rules

1. Every node must have a DC path to ground.

+

V

+

2. No dangling nodes.

V

+

3. No voltage loops.

+

V

-

V

-

+

V

4. No ideal Voltage source in closed inductor loop.

-

+

I

-

5. No Stacked Current Sources.

+

I

-

6. No ideal Current source in closed capacitor loop.

+

I

-

22

Page 11

11

Netlist Structure: Common Structure

θ

TITLE

First line becomes netlist title, so do not define any circuit element here

θ

* or $

Comments

θ

.OPTIONS

Set conditions for Simulation, Scaling (SCALE,SCALM)

θ

ANALYSIS Commands and TEMPERATURE

.dc, .op, .tf, .sense, .pz

.ac, .disto, .noise, .net

.tran, .four, .fft

.temp

23

Netlist Structure: Common Structure

θ

.PRINT/PLOT/Analysis

Set print, plot, and Analysis variables

.print, .plot, .graph, .probe

θ

.INITIAL CONDITIONS / Input Control

Input state : .ic, .nodeset, .include, .param

θ

SOURCES

Stimulus : vdd, vss, ac, dc, tran sources (pulse, pwl, sin, am, sffm, exp, etc )

θ

NETLIST

Circuit Description : node connection of elements

Passive elements(R,C,L,H,.), active elements(D,Q,M,J,W,X,U,.. )

θ

SUCKT Definition

.SUBCKT, .MACRO with .ENDS

24

Page 12

12

Netlist Structure: Common Structure

θ

.MODEL libraries

.MODEL

θ

+

In first column is continuation character

θ

ALTERing

.ALTER

.DEL LIB

θ

.END

Terminates the simulation

25

Netlist Structure : Recommended format

Title

Controls

Sources

Components

Models & Subckts

This is a better netlist

.options post acct opts node

.tran .1 5

$ needs 5 seconds to settle

.print v(6) i(r16)

.plot v(4) v(14) v(data)

*

Voltage sources

v4 4 0 dc 0 ac 0 0 pulse 0 1 0 .15 .15 .4 2

vdata data 0 sin(1.0 1.0 1.0 0.0 1.0)

v6 6 0 exp(1 0 .1 .02 .6 .2)

*

Components

L6 6 16 .05

c6 16 0 .05

r16 16 0 40

c4 4 14 .1

L5 data 15 1

c5 15 0 .2

.model ...

.end

26

Page 13

13

Node Naming Conventions

θ

Node and Element Identification

Vol. 1, p. 2-20

Either Names or Numbers (e.g. n1, 33, in1, 100)

Numbers: 1 to 99999999 (99 million)

Nodes with number followed by letter are all the same (e.g. 1a=1b)

0 is ALWAYS ground

Global vs Local

θ

Allowable Characters & Conventions (DON’T USE)

Begin with letter or “/”

Max of 1024 characters (after 1024 ignored)

May contain: + - * / : ; $ # . [ ] ! < > _ %

May NOT contain: ( ) , = ‘ <space>

Ground may be either 0, GND, or !GND

θ

Every node must have at least 2 connections (not Tline or MOS substrate)

27

Node Naming: Globals

θ

.GLOBAL

Vol. 1, p. 2-17

Syntax

9 .GLOBAL node1 node1 node3 ...

9 .GLOBAL VBIAS VCC

Don’t specify power pins in subcircuit calls.

Use .GLOBAL VCC

Usage

9 When subcircuits are included in the data file.

9 Assigns common node name to subcircuit nodes.

9 Power supply connection of all subcircuits often done this way

à

.GLOBAL VCC

à

Connects all nodes named VCC, inc. subcircuits with the internal node named VCC.

à

When a .GLOBAL is used, the node name is NOT concatenated with the circuit number for output variable

reference. Only assigned the global name. (This allows the exclusion of the power node name in the

subcircuit or macro call).

28

Page 14

14

Units & Scale Factors

θ

Units

R - ohm

C - Farad

L - Henry

θ

Technology Scaling (Scale = 1u, also SCALM)

ALL lengths and widths are in METERS

θ

Vol. 2, p. 15-7

Scale Factors

Vol. 1, p. 3-36

F = 1e-15

K = 1e3

P = 1e-12

MEG = X = 1e6

MIL(S) = 25.4e-6

N = 1e-9

G = 1e9

FT = .305 (METERS)

U = 1e-6

T = 1e12

DB = 20log10

M = 1e-3

29

Components: Passive Devices

θ

Components - Passive Devices

R - Resistors

Vol. 2, p 11-4

9 Rxxx n1 n2 Rval <options>

Same format. Just change the first letter.

9 R1 1 0 100

9 Element params: Temp, Scaling, etc.

L - Inductors

9 LSHUNT 23 51 10U

Vol. 2, p 11-14

C - Capacitors

9 C1 1 2 100p

Vol. 2, p 11-10

Can additionally specify a .MODEL for

R&C

30

Page 15

15

Components: Active Devices

D - Diodes

Vol.2, Chp 12

M - MOS Transistors

Vol.2, Chp 15

Q - BJTs

Vol. 2, Chp 13

Í active device model1 1IU

Subcircuits & Macros

Vol. 3, Chp 21

31

Components: Diodes

θ

D - Diodes

Vol. 2, Chp 12

Dxxx nplus nminus mname <options>

9 D1 3 0 DMOD IC=0.2v

à

Voltage of 0.2v at time 0. Diode model params contained in a model statement, DMOD.

à

IC condition .TRAN UIC option

-

1 Eí1 ª½¹ îa .MODEL mname D <LEVEL=val> <keyname=val>...

à

3 types of models: geometric, non-geometric, Fowler-Nordheim

9 .MODEL DMOD D

Related Controlling .OPTIONS

Vol. 2, p 12-2

9 DCAP, DCCAP

9 GMIN, GMINDC

9 SCALE, SCALM

32

Page 16

16

Components: MOSFET

θ

MOSFET defined by:

Vol. 2, p. 15-1

MOSFET Element Statement & MOSFET MODEL

2 submodels

9 CAPOP specifies the model for the gate capacitances (recommend =4)

9 ACM, Area Calculation Method, selects the type of diode used for the MOSFET bulk diodes.

(0=SPICE 2G6, 1=ASPEC, 2=META, 3=ACM2 extension)

θ

θ

Models either P channel or N channel.

Classified according to Level

Vol. 2, p. 15-2

Available: 1,2,3,4,5,6,7,8,13,27,28,38,39,42, 43, 47,49,50 proprietary.

Level = 1,Suare-law IV model

Level = 2,Analytical Model

Level = 3, Semi-empirical model

Level=50, Philips MOS9 Model

33

Components: MOSFET

θ

BSIM(Berkeley Short channel IGFET Model)

- ÙÙ E small deviceéi rEÍ uÍ, ÑÅî)I ± inputÿ1

1ÑeÑ.

BSIME parameter empirically-basedÿa­I SPICEI EÙõ simple device model

E I±i æâU

BSIM- 1=î BI yI simulation1 ííU

BSIM

Level=13, BSIM1

Level=28, BSIM 1 derivative; Avan proprietary - excellent model

Level=39, BSIM2

Level=49, BSIM3v3; Level=47, BSIM3v2; Level=42, BSIM3v1

34

Page 17

17

Components: MOS: MOS Element description

θ

Syntax

Vol. 2, p. 15-8

Mxxx nd ng ns <nb> mname <L=val> <W=val> <options...>

Mxxx nd ng ns <nb> mname lval wval ...

θ

Examples

Mxxx DRAIN GATE SOURCE BULK

M1 3 4 5 0 nch 5u 10u

M31 2 17 6 10 MODM l=5u w=2u

Mabc 2 9 3 0 mymod l=10u w=5u ad=100p as=100p pd=40u ps=40u

θ

SCALING (See Controls & Options Session)

Units are controlled by .OPTION SCALE and MODEL param SCALM.

Default L and W: METERS!!!

.OPTION SCALE=1e-6

M1 10 20 30 0 modnam l=5u w=10u

M1 10 20 30 0 modnam l=5 w=10

equivalent

35

Components: MOS: MODEL

θ

Syntax

Vol. 2, p. 15-18

.MODEL mname NMOS (<level=val> <keyname1=val1>...)

.MODEL mname PMOS (<level=val> <keyname1=val1>...)

θ

Examples

.MODEL MODP PMOS (level=3 vto=-3.25 gamma=1.0)

.MODEL MODN NMOS (level=2 vto=1.85 tox=735e-10)

.MODEL nchan.1 nmos level=2 vto=2.0 uo=800 tox=500

+ nsub=1e15 rd=10 rs=10 capop=5

* comments

36

Page 18

18

Components: MOS: CAPOP & ACM

θ

Capacitance Options: CAPOP

Vol. 2, p. 15-41

Different models for gate-drain, gate-source, gate-bulk capacitance.

Substantial effect on Transient Analysis

CAPOP=4 selects recommended charge-conserving model for the given DC model.

H96.1 has a new CAPOP=14 model, improved upon CAPOP=13, for correcting chargeconserving behavior near threshold voltage region, and other improvements ...

θ

ACM (Area Calculation Method)

Vol. 2, p. 15-19

Modelling of bulk-source, bulk-drain diodes. Recommend ACM=3

37

Components: JFET/MESFET Element Syntax

θ

Element Syntax

θ

Examples

Vol. 2, p. 14-4

Jxxx nd ng ns <nb> mname <W=val> <L=val> <options>

Jxxx DRAIN GATE SOURCE BULK

J1 7 2 3 JM1

jmes xload gdrive common jmodel

θ

SCALING (See Controls & Options Session)

Units are controlled by .OPTION SCALE and MODEL param SCALM.

Controlled by element parameters: M and AREA

Default L and W: METERS!!!

38

Page 19

19

Components: JFET MODEL

θ

Syntax

Vol. 2, p. 14-9

.MODEL mname NJF (<level=val> <pname1=val1>...)

.MODEL mname PJF (<level=val> <pname1=val1>...)

θ

Example

.MODEL nj_acmo njf level=3 capop=1 sat=3 acm=0

+ is=1e-14 cgs=1e-15 cgd=.3e-15

+ rs=100 rd=100 rg=5 nd=1

39

Components: BJT

vol. 2, p. 13-1 to 13-42

θ

Requires a BJT element and a .MODEL statement

θ

BJT Syntax

Vol. 2, p. 13-2

Qxxx nc nb ne <ns> mname <aval> <OFF> <IC=vbeval,vceval> <M=val>

+<DTEMP=val>

Qxxx Collector Base Emitter <Substrate>

Qxxx nc nb ne mname

Q23 10 24 13 QMOD IC=0.6,5.0

θ

MODEL Syntax

Vol. 2, p. 13-10

.MODEL mname NPN <pname1=val1>...

.MODEL mname PNP <pname1=val1>...

9 .MODEL QMOD NPN ISS = 0 XTF=1 NS=1.0 CJS=0...

θ

Element Controlling Options: Area, Initialization, Temp

θ

.OPTION controls (dcap, dccap, gmin, gmindc)

40

Page 20

20

Sources: Independent

θ

Independent Sources, Voltage or Current

Vol. 1, pp. 4-1+

DC

AC

Transient (Time Varying)

9 Pulse

9 SIN

9 PWL

à

Data Driven (Imported as time/value pairs)

9 AM, SFFM

9 EXP

Mixed (Composite)

41

Sources: Independent: DC, AC

θ

Syntax

Vxxx n+ n- <<DC=> dcval> <tranfun> <AC=acmag, acphase>

or

Iyyy n+ n- <<DC=> dcval> <tranfun> <AC=acmag, acphase> <M=val>

θ

DC Sources

+

V

V1 1 0 DC=5V (def. = 0v)

V1 1 0 5V

I1 1 0 DC=5ma

-

+

DC sweep range is specified in the .DC analysis statment.

θ

I

-

AC Sources

impulse functions used for an AC analysis

AC (freq. Domain analysis provides the impulse response of the circuit

V1 1 0 AC=10v,90 (def. ACMAG=1v, ACPHASE=0 degree)

AC frequency sweep range is specified in the .AC analysis statment.

42

Page 21

21

Independent Transient Sources: Pulse

θ

Time Varying (Transient)

Vol. 1, p. 4-3

PULSE v1 v2 <td <tr <tf <pw <per>>>>

V1,v2 must be defined

PULSE (v1 v2 <options> )

td

delay from beginning of tran

interval to 1st rise ramp. Def: 0.

Examples

tr

rise time (default: TSTEP)

9 VIN 3 0 PULSE (-1 1 2ns 2ns 2ns 50ns 100ns)

tf

fall time (default: TSTEP)

9 V1 99 0 PU 1v hiv tdlay tris tfall tpw tper

pw

pulse width (def: TSTEP)

per

pulse period (def: TSTEP)

à

Pulse Value parameters defined in the .PARAM statement.

à

PU (PULSE - ASPEC)

per

5

pw

V1 1 0 pulse 0 5v 5ns

5ns 5ns 10ns 30ns

tr

+

0

tf

td

5

10

15

20

25

30

35

43

Independent Transient Sources: PWL

θ

Piece-Wise Linear

Vol. 1, p. 4-8

PWL t1 v1 <t2 v2 t3 v3...> <R <=repeat>> <TD=delay>

time-voltage or time-current pairs

PWL (t1 v1 <options>)

Repeat time must be a time point

within the function. Default: 0.

PWL t1 I1 <t2 I2...> <options>

9 Value of source at intermediate values is determined by linear interpolation.

9 PL (ASPEC style) reverses order to voltage-time pairs.

Examples

9 V1 1 0 PWL 60n 0v, 120n 0v, 130n 5v, 170n 5v, 180 0v, R

5

VIN VGate 0 PWL (0 0v 5n 0v +10n

5v 13n 5v 15n 2.5v 22n 2.5v +25n 0 30n

0 R)

0

5

10

15

20

25

30

35

44

Page 22

22

Independent Transient Sources: SIN, Mixed

θ

SIN

Vol. 1, p. 4-5

SIN vo va <freq <td <damping <phasedelay>>>>

Vo va - must specify

SIN (vo va <options> )

td - delay in sec. def: 0

damping - def: 0

Examples:

phasedelay - degrees, def: 0

9 VIN 3 0 SIN ( 0 1 100MEG 1ns 1e10)

à

θ

vo,va - volts or amps

Damped sinusoidal source connected between nodes 3 and 0. 0v offset, Peak of 1v, freq of 100 MHz, time

delay of 1ns. Damping factor of 1e10. Phase delay (defaulted to 0) of 0 degrees.

Composite (Mixed)

Specify source values for more than 1 type of analysis.

Examples

9 VH 3 6 DC=2 AC=1,90

9 VCC 10 0 VCC PWL 0 0 10n VCC 15n VCC 20n 0

9 VIN 13 2 0.001 AC 1 SIN (0 1 1Meg)

45

Sources: Dependent

θ

Dependent Sources (Controlled Elements)

Vol. 1, Chp. 4

High Level of Abstraction

Used to Simplify Circuit

Descriptions.

9 Used for behavioral modelling

9 Faster Execution Time

Based on an arbitrary algebraic equation as the transfer function for a voltage or current

source.

Common method used to create function libs of subcircuits containing behavioral

elements.

θ

Types

G

Voltage Controlled Current Source (I=g(transconductance) * v )

E

Voltage Controlled Voltage Source (V=e(voltage gain) * v )

H Current Controlled Voltage Source

F

θ

Current Controlled Current Source

Voltage Controlled Resistor and Capacitor

Several Forms:

Linear

Polynomial

PWL

Multi-Input Gates

Delay Element

Still supported, but

OBSOLETE

46

Page 23

23

Sources: Dependent

θ

What you can do with Dependent Sources

AND, NAND, OR, NOR gates

MOS, Bipolar Transistors

OP Amps, Summers, Comparators

Switched Capacitor Circuits, etc.

Switches ( using VCR)

θ

Syntax

Linear

9 Exxx n+ n- <VCVS> in+ in- gain <options>

n+,n-

Controlled nodes

in+,in-

Controlling nodes

9 Egain 3 0 Vp Vn 1E3

47

.SUBCKT Syntax

.SUBCKT subnam n1 <n2 n3 ...> <parnam=val ...>

Vol 3, p. 21-5

9 n1... Node numbers for EXTERNAL reference. Any element nodes appearing in the subcircuit,

but not included in this list, ARE STRICTLY LOCAL.

à Except: GROUND NODE (0)

à Except: Nodes assigned using BULK( MOSFET) or SUBSTRATE (BJT)

à Except: Nodes assigned using the .GLOBAL statement.

9 parnam=val A parameter name set to a value. For use ONLY in the subcircuit.

à OVERRIDDEN by an assignment in the subcircuit call or by a value set in a .PARAM statement.which is

EXTERNAL to the subcircuit

9 subnam - Reference name for the subcircuit model call

Alternate: .MACRO subnam n1 <n2...> <parnam=bal>

48

Page 24

24

.SUBCKT Components: Subcircuit Calls

θ

X Element Syntax

Xyyy n1 <n2 n3 ...> subnam <parnam=val ...> <M=val>

Vol. 3, p. 21-7

9 Xnand1 in1_1 in2_1 clk out_1 nand3 wn=10 ln=1

à Calls subckt named “nand3”. Assigns params WN=10 and LN=1 (parameters WN and LN within the

.SUBCKT)

9 Xnand2 in1_2 out_1 in3_2 out_2 nand3 wn=8 ln=.8

à Calls subckt named “nand3”. Assigns params WN=8 and LN=.8 (parameters WN and LN within the

.SUBCKT)

à ALL subcircuit names begin with an “X”

49

.SUBCKT Components: Example

θ

Inverter Example

VCC VCC 0 VCC

.PARAM VCC=5V

.GLOBAL VCC

X1

Global Reference to VCC

Node 0 not mentioned in CALL

1

2

invsub

Mult=3

...

.SUBCKT invsub IN OUT MULT=1

M1 VCC IN OUT 0 P M=mult

Node 99 is LOCAL

.PARAM substitution

NOT positional

M2 OUT IN 0

M gets 3 from Call

0 N M=mult

C1 OUT 99 10pf

R1 99 0 10

Output Variables:

.ENDS

.PRINT I(X1.M1)

.PRINT V(X1.99)

.PRINT P(X1) $ Power dissipation in subcircuit X1 ( 96.1 onward )

.PRINT Tran IPIN(X1.1) $ Probing subcircuit pin current of pin X1.1 (96.1 onward)

.PRINT V(1) $ Since IN and OUT have been REPLACED by Nodes 1 and 2, respectively!!!

50

Page 25

25

Day 1 : Session 3

51

Analysis Types

θ

Analysis Types

θ

Output & Formatting

output variables

.print/.plot

52

Page 26

26

Analysis Types: Types and Order

θ

Types and Order of Execution

DC Operating Point (Bias Point) is first

calculated for ALL analysis types.

DC Operating(Bias) Point

9 First and most important job is to determine the DC steady state response (called the DC operating

point)

DC Bias Point & DC Sweep Analysis

9 .DC, .OP, .TF, .SENS

AC Bias Point & AC Frequency Sweep Analysis

9 .AC, .NET, .Noise, .Distortion

Transient Bias Point & Transient Sweep Analysis

9 .Trans, .Fourier, .OP <time>

Temperature Analysis

9 .Temp

θ

Advanced Modifiers: Monte Carlo, Optimization

53

Analysis Types: Operating Point Calculation

θ

θ

Æ~ý,quiescent point)i YE pa í þ

a

- transient initial]a1 E transienta

ñ½, DC

a

ñ½ åÍ 1 devicei ñI A small signal model1 E

a

ñ½ ÉÉ ÑvÑ.

DC Operating Point(

DC Operating Point

,

AC

Caps OPEN, Inductors SHORT

Initialized by .IC, .NODESET, and Voltage Sources (time zero values)

θ

Disable with .TRAN UIC option (Use Initial Conditions)

θ

.OP <format> <time> <format> <time>

Input deck

Vol. 1, p. 5-4 (transient only)

½ .OPí ÙUa SPICEI EÙõ ­ Éñ½E OPi YEyÑ.

Prints

9 Node voltages, Source Currents

9 Power Dissipation at the Operating Point

9 Semiconductor device currents, conductances, capacitances

54

Page 27

27

Analysis Types: DC Analysis

θ

5 DC Analysis & Operating Point Analysis Statements Vol. 1, p.7-1

9 .DC

9 .OP

ái

9 .PZ

Sweeps for power supply, temp, param, transfer curves

Specify time(s) at which operating point is to be calculated, bias point

report

Pole/Zero Analysis

9 .SENS

DC small-signal sensitivities.

9 .TF

DC small-signal transfer function

a

-

±1

1\EÙYU

circuit parameter½ íI ¦ ­E

ñÙUÞ1

θ

bias point

DC

small signal sensitivity,

θ

.DC Statement Sweeps:

½ íI BI

Any parameters, any source value, Temperature

DC Monte Carlo (random sweep)

DC Circuit Optimization

DC Model Characterization

55

Analysis Types: DC Analysis: Syntax

.DC var1 start1 stop1 incr1 <var2 start2 stop2 incr2>

Vol. 1, p.7-2

.DC var1 start1 stop1 incr1 <SWEEP var2 type np start2 stop2>

θ

Examples

.DC VIN 0.25 5.0 0.25

Sweep VIN from .25 to 5v by .25v increments

.DC VDS 0 10 .5 VGS 0 5 1

Sweep VDS from 0 to 10v by .5 incr at VGS values of 0, 1, 2, 3, 4, & 5v.

.DC TEMP -55 125 10

Sweep TEMP from -55C to 125C in 10 degree C increments

.DC xval 1k 10k .5k SWEEP TEMP LIN 5 25 125

DC analysis performed at each temperature value. Linear TEMP sweep from 25 to 125 (5 points)

while sweeping a resistor value called ‘xval’ from 1K to 10K in .5K.

.DC DcSrc START=0 STOP=srcval STEP=‘srcval/100’

H93a.02 onward. Parameterize start/stop/incr values

H93a.02 Rel. Note, p. 5

56

Page 28

28

Analysis Types: DC Analysis: .TF, .SENS

θ

.TF Outvar INSRC

Small-signal DC gain, input resistance, output resistance

±

Examples

9.DC V(4) V(1)

θ

à

DC Gain : V(4) / V(1)

à

Input resistance : node 1

à

Ouput resistance : node 4

é node 0aE íZ

- node 0 aE íZ

.SENS OV1 <OV2 … >

Í circuit parameter½ ía ¦ ­E DC small signal sensitivityi

­í »- ª ± ~E data Ê

Example

9.SENS V(9) V(4,3) V(17) I(VCC)

57

Analysis Types: AC Analysis

θ

θ

θ

θ

θ

θ

顱 éù ñ ¡½ éù >â1 YU

yI¡½

1ai

elementí u)a yIa

ñ½ elementE small signal

¹jmodel

1 EÙ

yI a

½

DC OP±1 vI ±, Í nonlinear device½ íEÙ OPi þÙ)I small

signal model1 IÑ.

Resistor, semiconductor device½ EI white noise ±

Flicker noise ± (device modelE KF, AF )

AC Analysis Statements

Vol. 1, p. 8-1

.AC

Compute output variables as a function of frequency

9 requires an A.C. source (v2 n1 n2 5 ac 1...)

9 set to 1 volt for normalized db plot

θ

.NOISE

Noise Analysis

.DISTO

Distortion Analysis

.NET

Network analysis

.SAMPLE Sampling Noise

.AC Sweep Statements:

Frequency, Element Value,Temperature, Model parameter Value

Random Sweep (Monte Carlo), Optimization and AC Design Analysis

58

Page 29

29

Analysis Types: AC Analysis: Syntax

θ

.AC type np fstart fstop

Vol. 1, p. 8-3

θ

.AC type np fstart fstop <SWEEP var start stop incr>

θ

Examples

.AC DEC 10 1K 100MEG

9Freq sweep 10 points per decade for 1KHz to 100MHz

éù ñí

a­I log(100M/1K) = 5 Decades aÍ, decadeæ 10 pointa­I =

½ ACa

U

9OCT : Octave = Decade / Log 2 , OCT,DEC éù ñí 1 9

1k~100M

9

10 * 5 + 1 = 51 point frequence

.AC LIN 100 1 100hz

9Linear Sweep 100 points from 1hz to 100Hz,

9LIN

- éù ñí n1 9

Ñ 1Hz µÑ ACa

.AC DEC 10 1 10K SWEEP cload LIN 20 1pf 10pf

NOTE:

‘cload’ is a variable,

NOT a capacitor

9AC analysis for each value of cload, with a linear sweep of cload between 1pf and 10pf (20 points).

Sweeping frequency 10 points per decade from 1Hz to 10KHz. (41point freq.)

59

Analysis Types: AC Analysis: .NOISE

θ

θ

θ

θ

θ

semiconductor device éù rzE noise Ê, ai a

U

a

- .ACa

é Au¡

ACa

É î éù½ %I î yE noisei ±EÍ ¦ output node½

ía î iE î yE noiseE RMSÿ1 VEÙ ±

SPICE src½ Þí input noisei ±Ué Æɽ ¦±u ­ output½

Þí output noisei ±

Resistor

.NOISE

.NOISE ovv srcnam inter

.NOISE V(5) VIN 10

½ input noise (VIN), output noise (v(5)) ±

9 interí 0 a]

E­ 7)a no summary printout

9inter í 1 aa uå éù½E a

éi printout

9 10 point frequency

.PRINT NOISE ONOISE INOISE

60

Page 30

30

Analysis Types: Transient Analysis

θ

Transient Analysis Statements

Vol. 1, p. 6-1

Compute circuit solution as a function of time over a time range

θ

.TRAN Statement Can be Used for:

Transient Operating Point (eg. .OP 20n)

Transient Temperature Sweep

Transient Monte Carlo Analysis (random sweep)

Transient Parameter Sweep

Transient Optimization

61

Analysis Types: Transient Analysis: Syntax

θ

.TRAN tincr1 tstop1 <tincr2 tstop2...><START=val> <UIC> <SWEEP ..>

Vol. 1, p. 6-3

θ

DC bias point

TINCR1 known as the “PRINT INTERVAL”

θ

Examples

(NOT the timestep interval).

i õ ÿ)I U.

TMAX = MIN(TINCR,(TSTOP-TINCR)/50)

.TRAN 1ns 100ns

9Transient analysis is made and printed every 1ns for 100ns.

.TRAN .1ns 25ns 1ns 40ns START=10ns

9Calculation is made every .1ns for the first 25ns, and then every 1ns until 40ns. The printing and

plotting begin at 10ns.

.TRAN 10ns 1us SWEEP cload POI 3 1pf 5pf 10pf

9Calculation is made every 10ns for 1us at three cload. (POI - Points of Interests)

62

Page 31

31

Analysis Types: Capacitance Options

θ

.OPTION DCCAP

Vol. 1, p. 5-8, Vol. 2, p. 12-2

Forces the voltage variable capacitors to be evaluated during a DC sweep.

Generate C-V plots (mos devices)

Print out capacitance values of a circuit during a DC analysis.

Default = 0

C-V plots often generated using a DC sweep of the capacitor.

θ

See the demonstration file mosivcv.sp. $installdir/demo/hspice/mos

Vol. 3, p. 11-6 to 11-10 for a template.

θ

.OPTION CAPTAB

Vol. 1, p. 5-8

Print a table of single plate nodal capacitance for diodes, BJTs, MOS, JFETs, and passive

capacitors at each operating point.

63

Output & Formatting: Output

θ

Output Commands

Vol. 1, Chp. 3

.PRINT, .PLOT, .GRAPH, .PROBE, and .MEASURE

Each statement specifies:

9 output variable

9 simulation result to be displayed

9 .GRAPH sends hardcopy to printer automatically

9 .GRAPH is not implemented on P.C.

9 .PROBE can limit .TR# file size ( requires .options probe)

9 .MEASURE has several special forms

64

Page 32

32

Output & Formatting: .PLOT, .PROBE

θ

.PLOT syntax

Vol.1, p. 3-38

.PLOT antype ov1 <ov2...> <plo1,phi1...plo32,phi32>

9 Same syntax as .PRINT

9 Add <plo1,phi1> to set lower and upper plot limits.

θ

.PROBE syntax (Only works when .OPTIONS PROBE is used)

.PROBE antype ov1 <ov2...ov32>

θ

Using with Subcircuits (Xnnn)

Vol. 1, p. 3-37

Specify nodes ‘local’ to a subcircuit. (Nodes on ‘calling’ line replace local nodes).

Concatenate circuit pathname with the node name through the ‘.’

9 X1.XBIAS.M5

or...

Based on unique number automatically assigned to each subcircuit (.OPTION LIST)

9 56:M5 (in this case Hspice assigned 56 to X1.XBIAS)

65

Output & Formatting: .GRAPH, AvanWaves

θ

.GRAPH

Non interactive

Placed in netlist to automatically generate a printout when HSPICE is run

Not supported on PC

θ

AvanWaves

Interactive

For display and analyzing Hspice simulation results

Opening a design file, e.g. .sp file, will automatically open all the output files under the

same design filename

On-line help

66

Page 33

33

Output & Formatting: .PRINT

θ

.PRINT syntax

Vol. 1, p. 3-34

.PRINT antype ov1 <ov2...ov32>

9 .PRINT tran v(4) i(vin) par(‘v(out)/v(in)’)

à

Print results of transient analysis for nodal voltage named 4, current through voltage source named vin, and the

ratio of the nodal voltage at node ‘out’ and ‘in’.

9 .PRINT AC VM(4,2) VR(7) VP(8,3) Ii(R1)

à

Print AC magnitude of the voltage difference between nodes 4 and 2. Real part of the AC voltage between

nodes 7 and ground. VP is phase difference between nodes 8 and 3. Ii is the imaginary part of the current

through element R1.

Vol. 1, p. 3-32

9 .PRINT LX8(m1)

à

Print the drain-source conductance of element m1.

9 SWEEPS

à

Appear as multiple, concatenated runs.

67

Output & Formatting: Analysis Data Format

θ

Graph nodal voltages, element currents, circuit response, algebraic expressions from

Transient Analysis, DC Sweeps, AC analysis...

θ

Specifying Analysis Data Format

Vol. 1, p. 2-35

.OPTION POST (Creates BINARY file; same as POST=1)

.OPTION POST=2 (Creates ASCII file)

9 Platform independent

θ

Limiting the size of the Analysis Data file

.OPTION PROBE (HSPICE plots ALL nodes by default)

9 Limit data in Analysis Data file to that specified in .PRINT, .PROBE, .GRAPH...

.OPTION INTERP

9 Limit the number of points stored. Pre-interpolates the output to the interval specified on the

.TRAN statement.

θ

.PROBE

Write directly to the Analysis Data File (without writing to .lis file)

68

Page 34

34

Output & Formatting: Output Variables

θ

5 Groups of Output Variables

DC and transient analysis

Vol. 1, p. 3-4+

9 display individual nodal voltages, branch currents, element power dissipation

AC analysis

9 display imaginary & real components of nodal voltage, branch current. Also phase, impedance

parameters..

Element templates

9 display element specific nodal voltages, branch currents, element parameters, and the derivatives of

element voltage, current, or charge.

.MEASURE

9 display user-defined variables as specified in the .MEASURE statement.

Parametric Statements - par(‘algebraic expression‘)

9 display mathematically, user-defined expressions operating on nodal voltages, etc.

69

Output & Formatting : Output Variable Examples

Vol. 1, p. 3-7

D.C. & Transient

Standard form is .print V(node) or I(element) OR .plot OR .graph OR .probe

9 v(1) = voltage at node 1

9 i(Rin) = current through Rin (direction of I is n1 to n2)

9 v(1,2) = voltage between node 1 and node 2 (differential)

Sweep or transient extended - .PRINT...

Vol. 1, p. 3-11

9 p(rload) = power dissipated in rload at point of analysis

9 p(m1) = power dissipated in transistor m1 at point of analysis

9 p(xfull.xff1) = power dissipated in subcircuit xfull.xff1 ( 96.1 onward )

9 power = total power dissipation output at point of analysis

9 v(x3.5) = voltage at INTERNAL node 5 of subckt x3

9 par(’p(x1.m1)+p(x2.m2)’)= sum of power in m1 of x1 and m2 of x2

9 i3(2:q2) = emitter current of q2 in second subckt called

70

Page 35

35

Output & Formatting : Output Variable Examples

A.C. analysis output examples

A.C.

Vol. 1, p. 3-10

.PRINT...

9 vi(2) = Imaginary voltage component at node 2

9 ip1(q4) = The phase of the collector current in q4

9 vdb(2,8) = The voltage ratio beteen node 2 and 8 in decibels

9 vp(4,6) = The arctangent [vi(4,6)/vr(4,6)]

Vol. 1, p. 8-9

A.C. Network

9 Standard form is Xij (z)

z = variable type

9 .plot s11(db) zin yout(p) s12(m)

DB = Decibels

I = Imaginary

M = Magnitude

P = Phase

R = Real

T = Group delay

71

Output & Formatting : Output Variable Examples

θ

Element Templates

Vol. 1 p. 3-25 to 34

Display element specific nodal voltages, branch currents, element parameters and the

derivatives of element voltage, current and charge

9 .plot tran q(c34) - will print the charge stored on c34

9 .print tran lv16(m3) - will print the effective drain conductance (1/rdeff)

9 .probe tran lx5(x23.m55) - will print the DC source-bulk diode current (CBSO)

Check manual of used version of HSPICE to assure proper label

H96.1 has improved naming convention for element template

9 VTH(m1) vs. LV9(m1)

9 GMO(m1) vs. LX7(m1)

9 GDSO(m1) vs. LX8(m1)

Test before using

72

Page 36

36

Output & Formatting : Output Variable Examples

θ

The .MEASURE statement

Vol 1. p. 3-13

Prints user-defined electrical specifications of a circuit

Used extensively in optimization

Has 7 fundamental measurement modes, each with its’ own form

9 Rise, fall, and delay

9 Average, RMS, min, max, and p-p

9 Find - when (e.g. find vin when vout = 2.5)

9 Equation evaluation

9 Derivative evaluation

9 Integral evaluation

9 Relative error ( used mostly for optimization)

73

Output & Formatting : Output Variable Examples

θ

Parameterized Output Variables

Vol. 1, p. 9-5

.print|probe|graph DC|AC|Tran out_variable=PAR(‘algebraic expression’)

or

.print|probe|graph DC|AC|Tran PAR(‘algebraic expression’)

The continuation character for quoted parameter strings is a double backslash, “\\”, as

described in algebraic expression rules.

Examples:

9 .print tran gain=PAR(‘v(3)/v(2)’)

9 .print DC PAR(‘v(3)/v(2)’)

9 .print tran mygain=PAR(‘v(3,1)’)

9 .print tran conductance=PAR(‘i(m1)/v(22)’)

74

Page 37

37

HSPICE elements,commands, and key letters

θ

Key letters are used to identify components

θ

The dot, “.”, is used to identify control statements

Passive

Passive elements

elements

R

R :: Resistor

Resistor

C

C :: Capacitor

Capacitor

L

L :: Inductor

Inductor

K

Inductor

K :: Coupled

Coupled Inductor

Sources

Sources

V

V :: Independent

Independent Voltage

Voltage source

source

II :: Independent

Current source

source

Independent Current

E

Controlled Voltage

Voltage source

source

E :: Voltage

Voltage Controlled

G

Controlled Current

Current source

source

G :: Voltage

Voltage Controlled

Signal

Signal Generators,Transient

Generators,Transient analysis

analysis

PULSE

pulse of

of pulse

pulse train

train

PULSE :: pulse

SIN

sin

SIN :: sin

sin or

or damped

damped sin

EXP

tapered

EXP :: exponentially

exponentially tapered

PWL

piece wise

wise linear

linear

PWL :: piece

Semiconductors

Semiconductors

D

D :: diode

diode

Q

Q :: bipolar

bipolar

JJ :: jfet,

jfet, mesfet

mesfet

M

M :: mosfet

mosfet

Subcircuits

Subcircuits and

and Models

Models

X

X :: Subcircuit

Subcircuit Calls

Calls

.SUBCKT

:

subcircuit

.SUBCKT : subcircuit descripton

descripton

.ENDS

.ENDS :: end

end of

of subcircuit

subcircuit

.MODEL

.MODEL :: model

model description

description

DC

DC analysis

analysis control

control

.DC

.DC :: DC

DC analysis

analysis

.TF

.TF :: Transfer

Transfer function

function

.SENS

.SENS :: sensitivity

sensitivity

Transient

Transient analysis

analysis control

control

.TRAN

.TRAN :: transient

transient analysis

analysis

.IC

.IC :: initial

initial condition

condition

.FOUR

.FOUR :: fourier

fourier analysis

analysis

AC

AC analysis

analysis control

control

.AC

.AC :: AC

AC analysis

analysis

.NOISE

.NOISE :: noise

noise analysis

analysis

.DISTO

.DISTO :: distortion

distortion analysis

analysis

Miscellaneous

Miscellaneous

.PRINT

.PRINT :: table

table of

of values

values

.PLOT

printer plots

plots

.PLOT :: line

line printer

.OPTIONS

.OPTIONS :: change

change defaults

defaults

.TEMP

temperature

.TEMP :: assign

assign temperature

.END

.END :: end

end of

of circuit

circuit definition

definition

TITLE

TITLE :: first

first line

line in

in netlist

netlist

** :: comment

comment line

line

++ :: continuation

continuation line

line

75

LAB 1A

åõ åîe Æy}e íZ)I aÕ¡± yIE Æ~ý1 YE

õq.

Create a netlist nemed “lab1a.sp” which describes the circuit shown at figure.

Use LIST, POST, NODE as options, and Request an operating point be calculated.

1

R1

1k ohm

2

V1

10volt

+

R2

V

1k ohm

-

0

Run HSPICE, eg. Hspice lab1a.sp >! Lab1a.lis

Review the output file ( vi lab1a.lis ) and Search for “operating”

76

Page 38

38

LAB 1B

åõ åîe Æy}e íZé ÑÉI aÕ¡± yIE Æ~ýé

éù ¦1 YE õq.

Create a netlist nemed “lab1b.sp” which describes the circuit shown at figure. Use LIST

, POST, NODE as options, and request an operating point be calculated.

And request an ac sweep 10 points per decade from 1kHz to 1MHz, and a print the AC

voltage at nodes 1 and 1, and the AC current through r2 and c1.

1

R1

1k

2

V1

10v DC

1v AC

+

V

-

R2

C1

1k

0.001uF

0

Run HSPICE, eg. Hspice lab1b.sp >! Lab1b.lis

Review the output file ( vi lab1b.lis ) and search for “ac analysis”.

After then, run awaves and call up lab1b.sp. Display the voltage at node 2.

Change the X axis to log.

77

LAB 1C

åõ åîe Æy}e íZé ÑÉI aÕ¡± yI½

i eíEÙ

a

1 E õq

pulse train

source

transient

.

Create a netlist nemed “lab1c.sp” which describes the circuit shown at figure. Add a

pulse input to the voltage source as follows

(starting voltage = 0v, pulse voltage = 5v, delay = 10ns, rise time = fall time = 20ns,

pulse width = 500ns, pulse repetition time = 2us)

Use LIST , POST, NODE as options, and request an operating point be calculated.

And request an transient analysis util 2usec with 10nsec time step.

1

R1

1k

2

V1

pulse

+

V

-

R2

C1

1k

0.001uF

0

Run HSPICE, eg. Hspice lab1c.sp >! Lab1c.lis

Review the output file ( vi lab1c.lis ) and search for “transient analysis”.

After then, run awaves and call up lab1c.sp. Display the voltage at node1 and node 2.

And display the currents through r2 and c1.

78

Page 39

39

LAB 1D

åõ åîe 4 butterworth low-pass filterE éù ¦é ÉñîÚ½

E ¦1 íE õq.

Create a netlist named “lab1d.sp” which describes the circuit shown at figure.

PWL voltage source, 0V at time 0sec, 0V at 1us, 1v at 20us, 0v at 20.1ns

AC voltage source, magnitude = 1v phase = 0 degrees

AC analysis, 20 points per decade from 100 to 100MegaHz

Transient analysis, 2us steps for 40us.

View the result of wave form of DB/Phase of voltage at node 3 and transient result of

voltage at node 3.

V1

PWL/AC

L1

1.5772U

L2

0.38268U

R1

1

1

5

2

3

C2

1.0824N

+

V

C1

1.5307N

-

0

79

LAB 1E

åõ åîe Æy}e DiodeE device modelE rs í yIE DC ¦½

åE î1 DC analysisi ¢EÙ íE õq

Create a netlist nemed “lab1e.sp” which describes the circuit shown at figure.

Set V1’s voltage to a variable, dv, and sweep dv from 800mV to 1V in 5mV steps.

And use following diode model.

( .model df d is = 2.6615e-16 rs = 0.0 )

Use LIST , POST, NODE as options, put in a print control for v(1) I(d1)

1

+

V

V1

D1

-

df

0

Run HSPICE, eg. Hspice lab1e.sp >! Lab1e.lis

Review the output file ( vi lab1e.lis ) and search for “dc transfer”.

After then, run awaves and call up lab1c.sp. Display I(d1) with dv as the x-axis. You can

see the unrealistic current spikes due to 0 ohm rs.

Change the rs of the diode to 0.01ohms in the model and do the same as above.

80

Page 40

40

LAB 1F

åõ åîe Peak DetectorE ¦1 íE õq.

Create a netlist named “lab1f.sp” which describes the circuit shown at figure.

V1 is a SIN wave source, 0volt offset, 1volt peak amplitude, frequency of 1KHz

V2 is a 500mV DC source.

Use DN4148 model, print out V(2) and V(1) vs, TIME

Transient anlysis, 10us steps for 3ms.

Diode model ( .MODEL DN4148 D (CJO=5PF VJ=0.6 M=0.45 RS=0.8 IS=7e-9

+

N=2 TT=6e-9 BV=100)

)

D1

DN4148

1

2

R1

1

V1

SIN

+

+

V

V V2

0.5V

-

0

81

LAB 1G

åõ MOSFETE IV ¦1 YE õq.

Create a netlist named “lab1g.sp” which describes the circuit shown at figure.

VDS and VGS are DC sources swept by DC analysis.

Sweep VDS from 0V to 10V in 500mV increments while sweeping VGS from 0V to 5V

in 1V increments. Print out I(VDS) and I(VGS) vs. VDS

Use the MOSFET MOD1 model

(.MODEL MOD1 NMOS level = 13 )

1

7

+

+

V

VGS

V

-

VDS

0

82

Page 41

41

LAB 1H

åõ MOSFET InverterE ¦1 íE õq.

Create a netlist named “lab1h.sp” which describes the circuit shown at figure.

The length for both MOS device is 1u, and the width is 20u. The pulse is

(vlow=0.2, vhigh=4.8, tdly=2n, tf=fr=1n, pw=5n, trep=20n)

The tran is 20n in 200p steps, and use the MOSFET model

( .MODEL nch NMOS level = 13

.MODEL pch PMOS level = 13)

Sweep VIN from 0V to 5V in 500mV increments. Print out V(out) and V(in).

vdd

Mp1

out

in

Mn1

+

VIN

PULSE

C1

0.75pF

+

V

V

-

-

VDD

5V

0

83

84

Page 42

42