NCS2006 Report

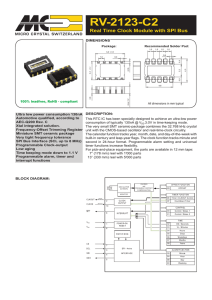

advertisement

NCS2006 SPICE Model Report

NCS2006 SPICE Model Report

1.0 Scope ...............................................................................................................................2 2.0 Op-amp Performance Features Included in this SPICE Model ......................................2 3.0 Functional Description ....................................................................................................3 4.0 Model Packaging Pin Connections .................................................................................3 5.0 Model Verification Testing .............................................................................................4 5.1.1 AC Gain/ Phase ..................................................................................4 5.1.2 Common Mode Impedance AC Analysis ..........................................5 5.1.3 Differential Mode Input Impedance AC Analysis .............................6 5.1.4 Input Bias Current vs. Temperature ...................................................7 5.1.5 CMRR vs. Frequency.........................................................................8 5.1.6 Common Mode Input Range DC .......................................................9 5.1.7 PSRR Plus Supply ...........................................................................10 5.1.8 PSRR Minus Supply ........................................................................11 5.1.9 Output Impedance ............................................................................12 5.1.10 Short Circuit Current Sinking ..........................................................13 5.1.11 Short Circuit Current Sourcing ........................................................14 5.1.12 VSat Plus Supply .............................................................................15 5.1.13 VSat Minus Supply ..........................................................................16 5.1.14 Output Voltage Swing......................................................................17 5.1.15 Slew Rate Vdd +/-2.75V ..................................................................18 5.1.16 Small Signal Non-Inverting Pulse Response ...................................19 5.1.17 Small Signal Inverting Pulse Response ...........................................20 5.1.18 Large Signal Non-Inverting Pulse Response ...................................21 5.1.19 Large Signal Inverting Pulse Response ...........................................22 5.1.20 Quiescent Current vs. Temperature .................................................23 5.1.21 AC Analysis with Noise...................................................................24 5.1.22 VOS vs. Temperature.......................................................................25 5.1.23 Single Ended Pulse Response ..........................................................26 6.0 Model Verification Comments .....................................................................................27 09/08/2015

Confidential and Proprietary

to AEi Systems

Page 1 of 28

NCS2006 SPICE Model Report

1.0

Scope

This report compares the simulated performance of the NCS2006 Rail-to-Rail Input and

Output, 3MHz opamp to the specifications and data provided by ON Semiconductor.

2.0

Op-amp Performance Features Included in this SPICE Model

Effects we are going to be modeling (All tests are at specific supply voltage, temperature and load

current, unless otherwise noted)

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

AC Gain/Phase vs. Frequency

Input Common Mode Impedance vs. Frequency

Input Differential Mode Impedance vs. Frequency

Input Bias / Input Offset Bias Currents vs. Temperature

AC Common Mode Rejection Ratio (CMRR) vs. Frequency

DC Common Mode Input Range

AC Power Supply Rejection Ratio Plus (PSRR) vs. Frequency

AC Power Supply Rejection Ratio Minus (PSRR) vs. Frequency

Closed Loop Output Impedance vs. Frequency

Output Short Circuit (Sinking) Current vs. Power Supply Voltage

Output Short Circuit (Sourcing) Current vs. Power Supply Voltage

Output Voltage Saturation Plus (VDD - VOH)) vs. Output Current

Output Voltage Saturation Minus (VOL - VSS)) vs. Output Current

DC Saturation

Slew Rate vs. Temperature at VDD Max (Configured as a Comparator)

Slew Rate vs. Temperature at VDD Min (Configured as a Comparator)

Small Signal Pulse Response (Inverting)

Small Signal Pulse Response (Non-Inverting)

Large Signal Pulse Response (Non-Inverting)

Large Signal Pulse Response (Inverting)

Quiescent Current vs. Power Supply Voltage

Input Noise Voltage Density vs. Frequency

Offset Voltage Drift with temperature at 25C, offset voltage set to 0 volts

Single Ended Large Signal (Non-Inverting)

Effects we are NOT going to be modeling

•

•

•

•

•

•

•

•

•

•

•

•

•

09/08/2015

Input Bias Current vs. Common Mode Input Voltage

Input Noise Voltage Density vs. Common Mode Input Voltage

CMRR vs. Temperature

PSRR vs. Temperature

Input Offset Voltage vs. Common Mode Input Voltage

Input Offset Voltage vs. Output Voltage

Input Offset Voltage vs. Power Supply Voltage

Quiescent Current vs. Common Mode Input Voltage

DC Open Loop Gain vs. Temperature

GBWP, Phase Margin vs. Temperature

Output Voltage Swing vs. Frequency

Output Voltage Headroom vs. Temperature

Measured Input Current vs. Input Voltage

Confidential and Proprietary

to AEi Systems

Page 2 of 28

NCS2006 SPICE Model Report

3.0

Functional Description

The NCS2006 series operational amplifiers provide rail−to−rail input and output operation, 3

MHz bandwidth, and are available in single, dual, and quad configurations. Rail−to−rail

operation gives designers use of the entire supply voltage range while taking advantage of the

3 MHz bandwidth. The NCS2006 can operate on supply voltages from 1.8 to 5.5 V over a

temperature range from −40 to 125°C. At a 1.8 V supply, this device has a slew rate of 1.2

V/us while consuming only 125uA of quiescent current per channel. Since this is a CMOS

device, high input impedance and low bias currents make it ideal for interfacing to a wide

variety of signal sensors. The NCS2006 devices are available in a variety of compact

packages.

Features

•

•

•

•

•

•

•

•

•

Rail−to−rail Input and Output

Wide Supply Range: 1.8V to 5.5V

Wide Bandwidth: 3MHz

High Slew Rate: 1.2 V/µs at Vs=1.8V

Low Quiescent Current: 125uA per Channel at Vs = 1.8V

Low Input Bias Current: 1pA Typical

Wide Temperature Range: −40 to 125°C

NCV Prefix for Automotive and Other Applications Requiring Unique Site and

Control Change Requirements; AEC−Q100 Qualified and PPAP Capable

These Devices are Pb−free, Halogen Free/BFR Free and are RoHS Compliant

Typical Applications

•

•

•

•

Unity Gain Buffer

Battery Powered / Low Quiescent Current Applications

Low Cost Current Sensing

Automotive

4.0

Model Packaging Pin Connections

.SUBCKT NCS2006 1 2 3 4 5

*

| | | | |

*

| | | | Output

*

| | | Negative Supply

*

| | Positive Supply

*

| Inverting Input

*

Non-inverting Input

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 3 of 28

NCS2006 SPICE Model Report

5.0

Model Verification Testing

5.1.1

AC Gain/ Phase

1_AC_G2_MARGIN-ACGAIN

VDD

AC LOOP

AC ANALYSIS

DB(V(OUT)/V(IN))

P(V(OUT)/V(IN))

RP

VDD

{VDD}

V2

1m

1Vac

0.000500Vdc

INP

RN

IN

1m

0

VSS

{VDD}

1

U1

V+

+

3

OUT

INM 2

-

NCS2006 V-

5

OUT

VDB

4

RL

{RL}

V1

-1Vac

VEE

C1

{CL}

0Vdc

0

0

0

PARAMETERS:

VDD = 2.75

RL = 10k

CL = 15p

RF = 1

Figure 5-1 AC Gain/ Phase Test Circuit

1

140

2

180d

OPEN LOOP GAIN

100

135d

OPEN LOOP PHASE

90d

50

45d

0

>>

0d

10Hz

1

100Hz

1.0KHz

DB(V(OUT)/(V(INP)-V(INM)))

10KHz

100KHz

1.0MHz

2

P(-V(OUT)/(V(INP)-V(INM)))

Frequency

10MHz

100MHz

Figure 5-2 AC Gain/ Phase Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 4 of 28

NCS2006 SPICE Model Report

5.1.2

Common Mode Impedance AC Analysis

2_COM_MODE_INPUT_Z

COMMON MODE IMPEDANCE

AC ANALYSIS

R=-V(IN)/I(RP) at low F

C=I(RP)/(2*PI*F*V(IN)) high F

RP

IN

VDD

1k

VIN

1Vac

0Vdc

VDD

{VDD}

INP

1

U1

V+

+

3

OUT

INM 2

0

-

NCS2006 V-

5

OUT

4

VEE

VSS

{VDD}

RG

RF

10T

{RF}

RL

{RL}

0

11

C1

{CL}

0

PARAMETERS:

VDD = 2.75

0

RL = 2k

CL = 100p

RF = 1

Figure 5-3 Common Mode Impedance AC Analysis Test Circuit

100G

1.0G

SEL>>

1.0M

V(IN)/I(RP)

100u

10n

1.0p

1.0uHz

10uHz

100uHz

1.0mHz

I(RP)/(6.283*Frequency*V(IN))

10mHz

100mHz

1.0Hz

10Hz

100Hz

1.0KHz

10KHz

Frequency

Figure 5-4 Common Mode Impedance AC Analysis Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 5 of 28

NCS2006 SPICE Model Report

5.1.3

Differential Mode Input Impedance AC Analysis

3_DIFF_MODE_INPUTZ

DIFFERENTIAL MODE IMPEDANCE

AC ANALYSIS

R=-V(IN)/I(RP) at low F

C=I(RP)/(2*PI*F*V(IN)) high F

VDD

VDD

{VDD}

1

INP

V1

U1

V+

+

1

OUT

INM 2

500uVdc

0

0

VSS

{VDD}

3

-

NCS2006 V-

5

OUT

4

VEE

V2

RL

{RL}

0

0Vdc

RG

RF

0

11

1000T

0

{RF}

C1

{CL}

0

PARAMETERS:

VDD = 2.75

0

RL = 10k

CL = 100p

RF = 1000T

Figure 5-5 Differential Mode Impedance Test Circuit

10G

100K

100

1/I(v2)

10u

100p

SEL>>

100f

1.0uHz

100uHz

10mHz

1.0Hz

I(V2)/(6.2835*V(INP,INM)*Frequency)

100Hz

10KHz

1.0MHz

100MHz

10GHz

Frequency

Figure 5-6 Differential Mode Impedance Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 6 of 28

NCS2006 SPICE Model Report

5.1.4

Input Bias Current vs. Temperature

4_IB_VS_T

IB VS. T

DC ANALYSIS, SWEEP T from -40 to 125C

PLOT I(RP) and I(RD) + some

small offset on log scale

RP

VDD

{RG}

1

INM

2

U1

V+

INP

3

VDD

{VDD}

+

OUT

0

-

NCS2006

4

5

OUT

VVEE

VSS

{VDD}

RL

{RL}

RD

1

RG

RF

{RG}

{RF}

0

C1

{CL}

0

PARAMETERS:

VDD = 2.75

RL = 10k

CL = 100p

RF = 1Meg

RG = 1Meg

Figure 5-7 Input Bias Current vs. Temperature Test Circuit

600pA

500pA

400pA

300pA

INPUT OFFSET BIAS CURRENT

200pA

100pA

0A

INPUT OFFSET CURRENT

-100pA

-40

-20

I(RP)- I(RD)

0

20

(I(RP)+I(RD))/2

40

60

80

100

120

140

TEMP

Figure 5-8 Input Bias Current vs. Temperature Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 7 of 28

NCS2006 SPICE Model Report

5.1.5

CMRR vs. Frequency

5_AC_CMRR

COMMON MODE REJECTION RATIO

AC ANALYSIS

PLOT DB(V(OUT))/(V(INP))

VDD

RP

IN

{RG}

VDD

{VDD}

VIN

1Vac

0Vdc

INP

1

INM

2

U1

V+

+

3

OUT

0

-

NCS2006 V-

5

OUT

VDB

4

VDB

VEE

VSS

{VDD}

VDB

RL

{RL}

V1

C1

{CL}

0.0005Vdc

RG

0

{RG}

0

PARAMETERS:

VDD = 2.75

RL = 10K

CL = 100p

RF = 10k

RG = 1m

Figure 5-9 CMRR vs. Frequency Test Circuit

120

80

40

CMRR

0

10Hz

-db(v(out))

100Hz

1.0KHz

10KHz

100KHz

1.0MHz

Frequency

Figure 5-10 CMRR vs. Frequency Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 8 of 28

NCS2006 SPICE Model Report

5.1.6

Common Mode Input Range DC

6_COM_MODE_INP_RANGE

COMMON MODE INPUT RANGE

DC ANALYSIS

PLOT D(V(1))/D(V(5))

RP

IN

VDD

{RG}

RD

INP

1

U1

3

VIN

0

V+

VDD

{VDD}

+

{RF}

OUT

INM

0

2

-

4

NCS2006

5

OUT

VVEE

VSS

{VDD}

RG

RF

{RG}

{RF}

RL

{RL}

C1

{CL}

0

0

PARAMETERS:

VDD = 2.75

RL = 2k

CL = 100p

RF = 5k

RG = 5k

Figure 5-11 Common Mode Input Range DC Analysis Test Circuit

20

0

-20

d(v(out))/d(v(inp))

4.0V

2.0V

0V

SEL>>

-2.0V

-8V

-6V

-4V

-2V

0V

2V

4V

6V

8V

10V

v(out)

V(inp)

Figure 5-12 Common Mode Input Range DC Analysis Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 9 of 28

NCS2006 SPICE Model Report

5.1.7

PSRR Plus Supply

7_AC_PSRR_PLUS-7_ PSRR_PLUS

VDD

RP

IN

TEST PSRR PLUS

AC ANALYSIS

DB(V(VDD)/V(OUT))

1m

INP

+

2

OUT

1m

-

NCS2006

VSS

{VDD}

RZ

5

4

INM

1m

U1

OUT

RP1

0

1

V+

V10.00050Vdc

3

VP

0

V-

VDD

1Vac

{VDD}

VEE

R1

{RL}

C1

{CL}

0

0

PARAMETERS:

VDD = 2.75

RL = 10K

CL = 100p

Figure 5-13 PSRR Plus Test Circuit

100

90

80

70

60

50

40

30

20

10

0

10Hz

-db(v(out))

100Hz

1.0KHz

10KHz

100KHz

1.0MHz

Frequency

Figure 5-14 PSRR Plus Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 10 of 28

NCS2006 SPICE Model Report

5.1.8

PSRR Minus Supply

8_AC_PSRR_MINUS

VDD

RP

IN

TEST PSRR MINUS

AC ANALYSIS

DB(V(VSS)/V(OUT))

1m

INP

INM

1m

U1

+

OUT

RP1

0

1

3

V10.00050Vdc

V+

VP

VDD 0

{VDD}

2

RZ

5

OUT

1m

-

4

V-

NCS2006

VEE

R1

{RL}

VSS

1Vac

{VDD}

C1

{CL}

0

0

PARAMETERS:

VDD = 2.75

RL = 600

CL = 100p

RSS

1m

Figure 5-15 PSRR Minus Test Circuit

100

90

80

70

60

50

40

30

20

10

0

10Hz

100Hz

db(v(vee)/v(out))

1.0KHz

10KHz

100KHz

1.0MHz

Frequency

Figure 5-16 PSRR Minus Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 11 of 28

NCS2006 SPICE Model Report

5.1.9

Output Impedance

9_ROUT

AC ROUT

AC ANALYSIS

V(OUT)/I(VTST)

VDD

RP

IN

1

VP

VDD 0

{VDD}

INP

1

U1 3

V+

+

OUT

INM

0VN

2

I2

RP1

5

OUT

0.05

-

4

0Adc

1Aac

V-

NCS2006

VEE

VSS 0

{VDD}

RG

RF

{RG}

1k

RL

100k

0

INN

CL

30p

0

0

PARAMETERS:

VDD = 2.75

RG = 1G

Figure 5-17 Output Impedance Test Circuit

10K

IMPEDANCE VS FREQUENCY

1.0K

100

10

AV = 100

AV = 1

1.0

AV = 10

100m

10m

10Hz

100Hz

V(OUT)/I(rp1)

1.0KHz

10KHz

100KHz

Frequency

Figure 5-18 Output Impedance Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 12 of 28

1.0MHz

NCS2006 SPICE Model Report

5.1.10 Short Circuit Current Sinking

10A_SHORTCKT_SINKING

V

SHORT CIRCUIT CURRENT SINKING

DC ANALYSIS

I(VL)

VDD

RP

INPP

2.5k

VDD

{VDD}

-10

VP

INP

1

U1 3

V+

+

OUT

INM

0

VSS

{VDD}

VN

0

2

-

4

NCS2006

5

OUT

V

RL

1m

VVEE

I

RG

RF

50k

1MEG

VL

0

INN

PARAMETERS:

VDD

VDD = 2.75

V

Figure 3-19 Short Circuit Current Sinking Test Circuit

0A

SHORT CIRCUIT CURRENT SINKING

-20mA

-40mA

NO TEMPERATURE DATA GIVEN

-50mA

0V

1.0V

2.0V

3.0V

4.0V

5.0V

5.5V

I(VL)

VDD*2

Figure 3-20 Short Circuit Current Sinking Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 13 of 28

NCS2006 SPICE Model Report

5.1.11 Short Circuit Current Sourcing

10B_SHORTCKT_SOURCING

SHORT CIRCUIT CURRENT SOURCING

DC ANALYSIS

I(VL)

VDD

RP

INPP

2.5K

VP

VDD

{VDD}

10

INP

1

U1 3

V+

+

OUT

INM

0VN

2

-

4

5

OUT

RL

1m

V-

NCS2006

VEE

VSS 0

{VDD}

RG

RF

50k

50k

VL

0

INN

PARAMETERS:

VEE

VDD = 2.75

Figure 3-21 Short Circuit Current Sourcing Test Circuit

40mA

SHORT CIRCUIT CURRENT SOURCING

30mA

20mA

10mA

NO TEMPERATURE DATA GIVEN

0A

0V

1.0V

2.0V

3.0V

4.0V

5.0V

5.5V

I(VL)

VDD*2

Figure 3-22 Short Circuit Current Sourcing Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 14 of 28

NCS2006 SPICE Model Report

5.1.12 VSat Plus Supply

11_VSAT_PLUS

VSAT PLUS

DC SWEEP IMIN to IMAX

V1(VDD)-V(OUT)

RP

INPP

VDD

10k

INP

VDD

{VDD}

VP

20

1

U1 3

V+

+

OUT

INM

2

-

4

NCS2006

0 VN

5

RZ

OUT

1m

V-

RL

1MEG

IL

VEE

VSS 0

{VDD}

1pA

25

RG

RF

10MEG

10MEG

VL

0

INN

PARAMETERS:

VDD = 2.75

0

Figure 3-23 VSat Plus Test Circuit (Vs = 5.5V)

300mV

200mV

100mV

0V

0A

2mA

v(vdd)-v(out)

4mA

6mA

8mA

10mA

12mA

14mA

I_IL

Figure 3-24 VSat Plus Test Results (Vs = 5.5V)

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 15 of 28

NCS2006 SPICE Model Report

5.1.13 VSat Minus Supply

12_VSAT_MINUS

VSAT MINUS

DC SWEEP IMIN to IMAX

V(OUT)-V(VEE)

RP

INPP

VDD

10k

VDD

{VDD}

VP

-20

INP

1

U1 3

V+

+

OUT

INM

0 VN

2

RZ

5

OUT

1m

-

4

NCS2006

RL

1MEG

VVEE

VSS 0

{VDD}

RG

RF

10MEG

10MEG

1pA

IL

VL

0

INN

PARAMETERS:

VDD = 2.75

0

Figure 3-25 VSat Minus Test Circuit (Vs = 5.5V)

500mV

400mV

300mV

200mV

100mV

0V

0A

5mA

10mA

15mA

20mA

v(out)-v(vee)

I_IL

Figure 3-26 VSat Minus Test Results (Vs = 5.5V)

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 16 of 28

NCS2006 SPICE Model Report

5.1.14 Output Voltage Swing

13_DCSAT-DCSAT

Output Voltage Swing

Sweep VP from -1 to +1

Plot V(OUT), V(VDD)-V(OUT) and V(OUT)-V(VSS)

V

VDD

RP

INPP

VDD

{VDD}

VP

0

2.5k

V

V+

V+

U1 3

1

INP

V+

+

OUT

VSS

{VDD}

VN

0

OUT

1m

2

INM

0

RO

5

-

NCS2006

4

V-

RL

{RL}

V

CL

4p

VEE

V-

RG

INN

VL

0

RF

V-

1MEG

10MEG

PARAMETERS:

V

0

VDD = 2.75

RL = 10k

Figure 3-27 Output Voltage Swing Sweep Test Circuit

4.0V

0V

+/-2.75V

-4.0V

V(out)

8.0V

5.0V

VSAT @ +2.75V

VSAT @ -2.75V

0V

SEL>>

-2.75V

-2.00V

V(VDD)-V(OUT)

-1.00V

V(Out)-V(VEE)

-0.00V

1.00V

2.00V

2.75V

V_VP

Figure 3-28 Output Voltage Swing Sweep Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 17 of 28

NCS2006 SPICE Model Report

5.1.15 Slew Rate Vdd +/-2.75V

14_SLEW_RATE-14_SLEW_RATE

SLEW RATE

TRANSIENT ANALYSIS

D(V(5))

SWEEP TEMP -40C to 125C

VDD +/-2.75V

VDD

RP

IN

1

V1 = -200m

V2 = 200m

TD = 2u

TR = 1n

TF = 1n

PW = 15u

PER = 1m

VIN

VDD

{VDD}

V

INP

1

INM

2

U1

V+

+

3

OUT

0

-

NCS2006 V-

5

OUT

V

4

VEE

VSS

{VDD}

RG

RL

{RL}

RF

0

V

10k

CL

{CL}

{RF}

0

PARAMETERS:

VDD = 2.75

0

RL = 10k

CL = 100p

RF = 90k

Figure 3-29 Slew Rate (Vdd=+/-2.75v) Test Circuit

2.0M

RISING EDGE

1.0M

FALLING EDGE

0

-40°

-20°

0°

20°

Max_XRange(d(v(out)),2.8u,2.9u)

1

2.0V

2

40°

60°

80°

100°

-Min_XRange(d(v(out)),18.5u,18.6u)

Temperature

120°

140°

2.0M

1.0M

0V

0

-1.0M

-2.0V

SEL>>

-2.0M

0s

1

5us

v(out)

10us

2

15us

20us

d(v(out))

Time

25us

30us

35us

Figure 3-30 Slew Rate (Vdd=+/-2.75v) Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 18 of 28

NCS2006 SPICE Model Report

5.1.16 Small Signal Non-Inverting Pulse Response

15_SSPULSE

VDD

SMALL SIGNAL PULSE RESPONSE

TRANSIENT ANALYSIS

V(OUT)

RP

IN

1

V1 = -40m

V2 = 40m

TD = 4u

TR = 1n

TF = 1n

PW = 3.4u

PER = 1m

VIN

VDD

{VDD}

INP

1

U1

V+

+

3

OUT

INM

0

2

RZ

5

OUT

1m

-

NCS2006 V-

4

VEE

VSS

{VDD}

RG

RF

1G

{RF}

RL

{RL}

CL

{CL}

0

0

PARAMETERS:

VDD = .9

0

RL = 10k

CL = .01p

RF = 1m

Figure 3-33 Small Signal Non-Inverting Test Circuit

100mV

0V

SEL>>

-100mV

v(in)

100mV

0V

-100mV

0s

2us

4us

6us

8us

10us

12us

v(out)

Time

Figure 3-34 Small Signal Non-Inverting Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 19 of 28

NCS2006 SPICE Model Report

5.1.17 Small Signal Inverting Pulse Response

15_SSPULSE_INVERTING

VDD

SMALL SIGNAL INVERTING PULSE RESPONSE

TRANSIENT ANALYSIS

V(OUT)

RP

IN

100

1

INP

U1

V+

VIN

VDD

{VDD}

3

0

V1 = -40m

V2 = 40m

TD = 4u

TR = 10n

TF = 10n

PW = 3.4u

PER = 1m

+

OUT

2

INM

0

RZ

5

OUT

1m

-

NCS2006 V-

4

VEE

VSS

{VDD}

RG

RF

{RF}

{RF}

RL

{RL}

0

CL

{CL}

0

PARAMETERS:

VDD = 2.75

RL = 10k

CL = 0.01p

RF = 10k

Figure 3-35 Small Signal Inverting Test Circuit

100mV

0V

-100mV

V(IN)

50mV

0V

SEL>>

-80mV

0s

2us

4us

6us

8us

10us

12us

V(out)

Time

Figure 3-36 Small Signal Inverting Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 20 of 28

NCS2006 SPICE Model Report

5.1.18 Large Signal Non-Inverting Pulse Response

16_LSPULSE

LARGE SIGNAL PULSE RESPONSE

TRANSIENT ANALYSIS

V(OUT)

RP

IN

VDD

1k

V1 = -0.5

V2 = 0.5

TD = 4u

TR = 1p

TF = 1p

PW = 3.2u

PER = 1m

VIN

VDD

{VDD}

INP

1

U1

V+

+

3

OUT

INM

0

2

RZ

5

OUT

1m

-

NCS2006 V-

4

VEE

VSS

{VDD}

RG

RF

10MEG

{RF}

RL

{RL}

CL

{CL}

0

0

PARAMETERS:

VDD = 0.9

0

RL = 10k

CL = 0.01p

RF = 1k

Figure 3-37 Large Signal Non-Inverting Test Circuit

1.0V

0V

SEL>>

-1.0V

V(IN)

1.0V

0V

-1.0V

0s

2us

4us

6us

8us

10us

12us

v(out)

Time

Figure 3-38 Large Signal Non-Inverting Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 21 of 28

NCS2006 SPICE Model Report

5.1.19 Large Signal Inverting Pulse Response

16B_LSPULSE_INVERTING

LARGE SIGNAL PULSE INVERTING RESPONSE

TRANSIENT ANALYSIS

V(OUT)

RP

0

V1 = -1

V2 = 1

TD = 4u

TR = 1p

TF = 1p

PW = 3.2u

PER = 1m

VIN

VDD

{VDD}

VDD

100

IN

1

INP

U1

V+

+

3

OUT

2

INM

0

RZ

5

OUT

1m

-

NCS2006 V-

4

VEE

VSS

{VDD}

RG

RF

{RF}

{RF}

RL

{RL}

0

CL

{CL}

0

PARAMETERS:

VDD = 2.75

RL = 10k

CL = 0.01p

RF = 10k

Figure 3-39 Large Signal Inverting Test Circuit

2.0V

0V

SEL>>

-2.0V

V(IN)

2.0V

0V

-2.0V

0s

2us

4us

6us

8us

10us

12us

V(OUT)

Time

Figure 3-40 Large Signal Inverting Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 22 of 28

NCS2006 SPICE Model Report

5.1.20 Quiescent Current vs. Temperature

17_IQUIESCENT

IQUIESCENT VS. T

DC ANALYSIS, SWEEP VDD from 0 to +5.5

REPEAT T at -40 25 125C

PLOT I(VDD) and -I(VEE)

VDD

RP

{RG}

INP

1

U1

V+

RD

3

VDD

{VDD}

+

{RF}

OUT

INM

0

2

-

4

NCS2006

5

OUT

VVEE

VSS

{VDD}

RG

RF

{RG}

{RF}

RL

{RL}

0

C1

{CL}

0

PARAMETERS:

VDD = 2.75

RL = 2k

CL = 100p

RF = 10MEG

RG = 10MEG

Figure 3-41 Quiescent Current vs. Temperature Test Circuit

180uA

160uA

25C

125C

120uA

-40C

QUIESCENT CURRENT

SINGLE CHANNEL

80uA

1.5V

2.0V

-I(vdd)

2.5V

3.0V

3.5V

4.0V

4.5V

5.0V

VDD*2

Figure 3-42 Quiescent Current vs. Temperature Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 23 of 28

5.5V

NCS2006 SPICE Model Report

5.1.21 AC Analysis with Noise

18_VNOISE

VNOISE

AC ANALYSIS WITH NOISE

nbi = sqrt(V(ONOISE))

since G=1

10k no noise

RP

G

VDD

{VDD} VP

1Vac

0

+

-

VDD

1

U1

V+

INP

3

GAIN = 100u

+

OUT

2

-

OUT

4

INM

0

5

V-

NCS2006

VSS

{VDD}

VEE

R1

{RL}

CF

C1

{CL}

0.5p

RG

0

RF

G

PARAMETERS:

+

-

1T

0

0

VDD = 2.75

RL = 2k

GAIN = 1

1 ohm no noise

CL = 100p

Figure 3-43 AC Analysis with Noise Test Circuit

600nV

500nV

400nV

125C

300nV

25C

200nV

100nV

-40C

0V

1.0Hz

10Hz

100Hz

1.0KHz

10KHz

100KHz

V(ONOISE)

Frequency

Figure 3-44 AC Analysis with Noise Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 24 of 28

NCS2006 SPICE Model Report

5.1.22 VOS vs. Temperature

20_VOS_VS_T

VOS VS TEEMPERATURE TEST

TRANSIENT ANALYSIS

V(OUT)

RP

IN

VDD

INP

U1

1

V+

V1 = 0

V2 = 0

TD = 100m

TR = 20u

TF = 20u

PW = 5

PER = 10

VIN

VDD

{VDD}

3

10k

+

OUT

INM

0

RZ

5

OUT

1m

2

-

NCS2006

4

VVEE

VSS

{VDD}

RG

RF

10k

{RF}

RL

{RL}

0

CL

{CL}

0

PARAMETERS:

VDD = 2.75

0

RL = 1MEG

CL = 100p

RF = 10k

Figure 3-45 VOS vs. Temperature Test Circuit

600uV

400uV

200uV

0V

-40

-20

v(inp)-v(inm)

0

20

40

60

80

100

120

140

TEMP

Figure 3-46 VOS vs. Temperature Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 25 of 28

NCS2006 SPICE Model Report

5.1.23 Single Ended Pulse Response

21_SINGLE_ENDED_TEST

SINGLE ENDED TEST

TRANSIENT ANALYSIS

V(OUT)

RP

IN

VDD

1k

V1 = 0

V2 = 5.5

TD = 2u

TR = 1p

TF = 1p

PW = 20u

PER = 1m

VIN

VDD

{VDD}

1

INP

U1

V+

+

3

OUT

2

INM

0

RZ

5

OUT

1m

-

NCS2006 V-

4

VEE

VSS

RL

{RL}

0

RG

RF

10MEG

{RF}

0

CL

{CL}

0

PARAMETERS:

VDD = 5.5

0

RL = 10k

CL = 100p

RF = 1k

Figure 3-47 Single Ended Pulse Response Test Circuit

6.0V

4.0V

2.0V

0V

V(IN)

6.0V

4.0V

2.0V

SEL>>

0V

0s

5us

10us

15us

20us

25us

30us

35us

V(OUT)

Time

Figure 3-48 Single Ended Pulse Response Test Results

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 26 of 28

40us

NCS2006 SPICE Model Report

6.0

Model Verification Comments

Overall the results of the model verification testing shows good correlation to the results

printed in the manufacturer’s datasheet.

The model release includes both the NCS2006.LIB (SPICE netlist in PSpice format/syntax)

and corresponding NCS2006.OLB (OrCAD Capture Symbol) file.

It should be noted that the model uses PSpice syntax and will NOT run in other SPICE

programs. Error messages will result if the model is not properly translated.

The model uses various PSpice syntax extensions to model the opamp’s behavior including

math equations, LIMIT function, Resistor tempco, and TABLE models. These items will

need to be translated into other syntaxes by AEi Systems, if customers request support for

any other simulator (LTSpice, SIMPLIS, Microcap, Multisim, etc.).

Translation of the model is not permitted by anyone other than AEi Systems.

The CMRR is only valid to approximately 50kHz due to model topology limitations.

The input bias and input offset currents are shown to linearly increase with temperature as

per the provided curves. Due to model limitations the input bias and offset currents increase

exponentially in the model. The simulated currents at 125°C are in good agreement with

the values in the curves.

The model does not emulate the output impedance variation due to the supply voltage

changes. Output impedance curves are provided for Vs = 1.8V and Vs = 5.5V. A

compromise is made by modeling the average of the two curves.

The gain bandwidth product (GBP) in the datasheet is stated to be 3MHz while the curve of

the AC Gain/Phase provided shows a 4MHz GBP. The opamp model is set to match the

4MHz GBP shown in the curve. There's a compromise made between the phase margin and

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 27 of 28

NCS2006 SPICE Model Report

gain margin with a simulated phase margin of 55 degrees and a simulated gain margin of

13.5dB vs. the datasheet specifying 60 degrees of phase margin and 10dB of gain margin

The offset voltage of the opamp is set to 500uV with an offset voltage drift of 1uV/°C as

per the datasheet parameters. The offset voltage is not modeled based on the offset voltage

vs. temperature curves provided in the datasheet.

09/08/2015

Confidential and Proprietary

to AEi Systems

Page 28 of 28