GOMACTech 05 Program

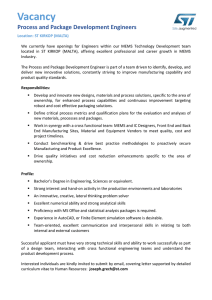

advertisement