Design and analysis of a dual mode CMOS field programmable

advertisement

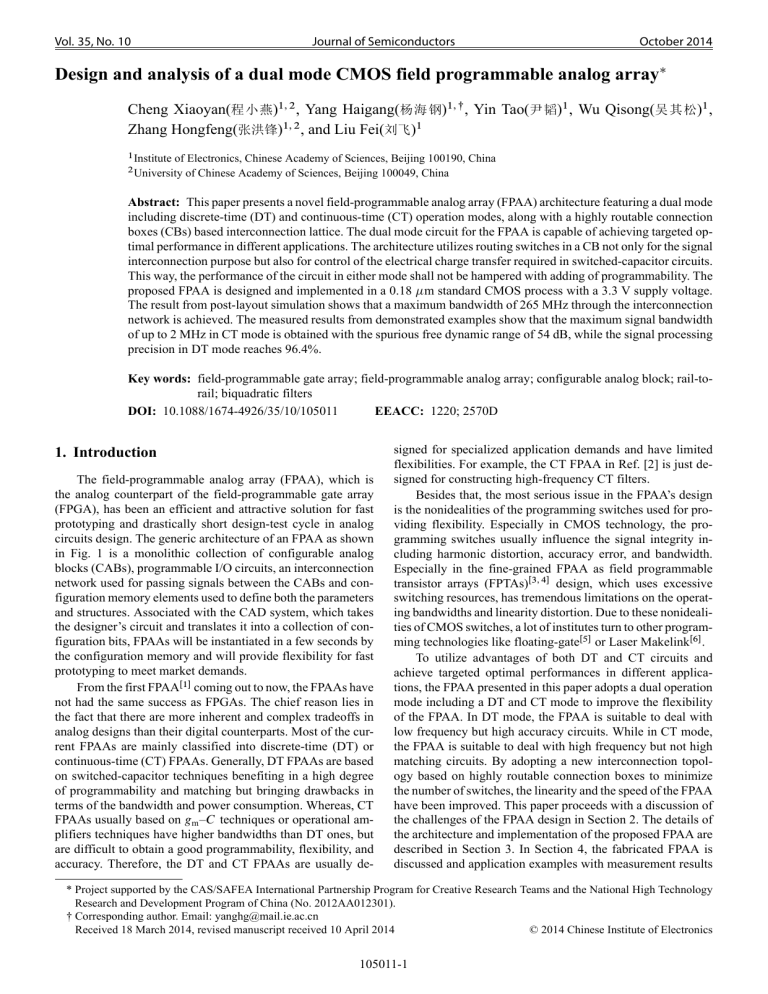

Vol. 35, No. 10 Journal of Semiconductors October 2014 Design and analysis of a dual mode CMOS field programmable analog array Cheng Xiaoyan(程小燕)1; 2 , Yang Haigang(杨海钢)1; , Yin Tao(尹韬)1 , Wu Qisong(吴其松)1 , Zhang Hongfeng(张洪锋)1; 2 , and Liu Fei(刘飞)1 1 Institute of Electronics, Chinese Academy of Sciences, Beijing 100190, China of Chinese Academy of Sciences, Beijing 100049, China 2 University Abstract: This paper presents a novel field-programmable analog array (FPAA) architecture featuring a dual mode including discrete-time (DT) and continuous-time (CT) operation modes, along with a highly routable connection boxes (CBs) based interconnection lattice. The dual mode circuit for the FPAA is capable of achieving targeted optimal performance in different applications. The architecture utilizes routing switches in a CB not only for the signal interconnection purpose but also for control of the electrical charge transfer required in switched-capacitor circuits. This way, the performance of the circuit in either mode shall not be hampered with adding of programmability. The proposed FPAA is designed and implemented in a 0.18 m standard CMOS process with a 3.3 V supply voltage. The result from post-layout simulation shows that a maximum bandwidth of 265 MHz through the interconnection network is achieved. The measured results from demonstrated examples show that the maximum signal bandwidth of up to 2 MHz in CT mode is obtained with the spurious free dynamic range of 54 dB, while the signal processing precision in DT mode reaches 96.4%. Key words: field-programmable gate array; field-programmable analog array; configurable analog block; rail-torail; biquadratic filters DOI: 10.1088/1674-4926/35/10/105011 EEACC: 1220; 2570D 1. Introduction The field-programmable analog array (FPAA), which is the analog counterpart of the field-programmable gate array (FPGA), has been an efficient and attractive solution for fast prototyping and drastically short design-test cycle in analog circuits design. The generic architecture of an FPAA as shown in Fig. 1 is a monolithic collection of configurable analog blocks (CABs), programmable I/O circuits, an interconnection network used for passing signals between the CABs and configuration memory elements used to define both the parameters and structures. Associated with the CAD system, which takes the designer’s circuit and translates it into a collection of configuration bits, FPAAs will be instantiated in a few seconds by the configuration memory and will provide flexibility for fast prototyping to meet market demands. From the first FPAAŒ1 coming out to now, the FPAAs have not had the same success as FPGAs. The chief reason lies in the fact that there are more inherent and complex tradeoffs in analog designs than their digital counterparts. Most of the current FPAAs are mainly classified into discrete-time (DT) or continuous-time (CT) FPAAs. Generally, DT FPAAs are based on switched-capacitor techniques benefiting in a high degree of programmability and matching but bringing drawbacks in terms of the bandwidth and power consumption. Whereas, CT FPAAs usually based on gm –C techniques or operational amplifiers techniques have higher bandwidths than DT ones, but are difficult to obtain a good programmability, flexibility, and accuracy. Therefore, the DT and CT FPAAs are usually de- signed for specialized application demands and have limited flexibilities. For example, the CT FPAA in Ref. [2] is just designed for constructing high-frequency CT filters. Besides that, the most serious issue in the FPAA’s design is the nonidealities of the programming switches used for providing flexibility. Especially in CMOS technology, the programming switches usually influence the signal integrity including harmonic distortion, accuracy error, and bandwidth. Especially in the fine-grained FPAA as field programmable transistor arrays (FPTAs)Œ3; 4 design, which uses excessive switching resources, has tremendous limitations on the operating bandwidths and linearity distortion. Due to these nonidealities of CMOS switches, a lot of institutes turn to other programming technologies like floating-gateŒ5 or Laser MakelinkŒ6 . To utilize advantages of both DT and CT circuits and achieve targeted optimal performances in different applications, the FPAA presented in this paper adopts a dual operation mode including a DT and CT mode to improve the flexibility of the FPAA. In DT mode, the FPAA is suitable to deal with low frequency but high accuracy circuits. While in CT mode, the FPAA is suitable to deal with high frequency but not high matching circuits. By adopting a new interconnection topology based on highly routable connection boxes to minimize the number of switches, the linearity and the speed of the FPAA have been improved. This paper proceeds with a discussion of the challenges of the FPAA design in Section 2. The details of the architecture and implementation of the proposed FPAA are described in Section 3. In Section 4, the fabricated FPAA is discussed and application examples with measurement results * Project supported by the CAS/SAFEA International Partnership Program for Creative Research Teams and the National High Technology Research and Development Program of China (No. 2012AA012301). † Corresponding author. Email: yanghg@mail.ie.ac.cn Received 18 March 2014, revised manuscript received 10 April 2014 © 2014 Chinese Institute of Electronics 105011-1 J. Semicond. 2014, 35(10) Cheng Xiaoyan et al. Fig. 1. Conceptual block diagram of FPAA. tor. However, there are still a lot of nonidealities. Firstly, the CMOS transistor switch is not like the ideal switch, which has a zero on-resistance (Ron / when ON and has an infinite off-resistance Roff when OFF. Besides the resistance effect, parasitic capacitors (Cps / exist at the input and output ports of the whole complementary CMOS switch. The bandwidth of the signal path is often limited by the resistance– capacitor effect of the switches in a signal path. Except the parasitic resistance and capacitor effects, the most challenging problem may be the nonlinearity of CMOS switches. To simplify the analysis, all CMOS switches in Fig. 2(a) take the same size. The W=L of PMOS is 27 m/0.3 m and the W=L of NMOS is 7 m /0.35 m in the 0.18 m CMOS process. The variation of Ron and Cp of one CMOS switch reaches ˙34% (˙75 absolutely) and ˙38% (˙16 fF absolutely) respectively as the input voltage varies from 0–3.3 V, shown in Fig. 2(b). Figure 2(a) shows a representative example that illustrates a simple PGA plus buffer circuits mapping in a traditional FPAA, which adopt a switch matrix as the routing fabric in interconnection network design like most FPAAsŒ5 7 . Each dot in the switch matrix in Fig. 2(a) represents a CMOS switch for interconnection and the solid ones represent that the switches are turned on and the hollow ones are turned off. The circuit shown in Fig. 2(a) implemented by FPAA is illustrated in Fig. 3(a) with switch modeling in the circuits. All parasitic effects of switches are shown in Fig. 3(a). The actual gain of the PGA circuit is expressed as Fig. 2. (a) An analog circuit and its mapping in the target traditional FPAA architecture and (b) the variation of on-resistance Ron and parasitic capacitance Cp of a CMOS switch with Vin sweeping from 0 to 3.3 V. are demonstrated. In Section 5, the conclusions are drawn. 2. Nonidealities of programming switches Programmable analog circuits often take complementary MOS transistor pairs as programming switches for large voltage swing and high linearity rather than a single MOS transis- Gainactual D Rout C 2Ron ; Rin C 2Ron (1) which is affected by the resistance value of switches. To reduce the gain error, the Ron of the CMOS switch must be small enough compared with Rin and Rout . This needs to enlarge the size of switches, which will cost a large chip area and add more parasitic capacitance connected to the interconnection wire. As the switch matrix with a size of “m” rows and “n” columns shown in Fig. 3(a), the bandwidth of the test line in the switch matrix according to the Elmore RC delay formula is about 1 ; (2) BW 2Ron .m C 2n/Cpoff 105011-2 J. Semicond. 2014, 35(10) Cheng Xiaoyan et al. tance of CMOS switches, the THD of FPAA chips will also be affected by programming switches. The (i C1)th harmonic distortion of a MOS switch is expressed asŒ9 HDj D !0 0 jhi jAi ; (3) where !0 is the angular frequency of the input signal, 0 is the RC time constant of the switch without considering nonlinearity, hi is the ith harmonic coefficient, and A is the amplitude of the input signal. The expression shows that the harmonic distortion of the signal through a MOS switch depends on the frequency and amplitude of the input signal and also depends on the time constant defined by the on-resistance and parasitic capacitors of the switch. To improve the linearity, the RC time constant of a switch needs to be as small as possible. The THD of the circuit implemented by a traditional FPAA with 5 columns and 10 rows interconnected network is nearly 25 dB higher than the ASIC implementation methods with a 20 kHz input sine signal as shown in Fig. 3(c). The THD will be worse if enlarging the size of the interconnect network. The accuracy, bandwidth and linearity of circuits mapped in FPAA will significantly be limited if using a large amount of switches in the signal path like in switch matrix interconnect networks. This paper investigates a novel FPAA interconnect topology to avoid the above routing fabric performance deteriorating without losing flexibility in interconnection networks. 3. The architecture of the proposed FPAA 3.1. Design of interconnection network and CABs Fig. 3. (a) Actual circuit mapping in the FPAA with parasitic RC modeling of CMOS switches. (b) Routing delay of a path line in CMOS switch matrix interconnection network. (c) The THD comparison of FPAA versus ASIC. where Cpoff is the parasitic capacitor of a CMOS switch connected to the interconnection wire when OFF, which is smaller than the parasitic capacitor of a CMOS switch when ON. Take an actual example, the parasitic capacitances associated with the routing lines in Ref. [5], which takes floating-gate CMOS technology, reach 1.6 pF for the global vertical line and 1.5 pF for the global horizontal. The bandwidth of a signal passing through two switches and one nearest neighbor vertical line and one local vertical line has been found to be 57 MHz without considering the worst condition that includes long global lines. The test line in Fig. 3(a) just contains two switches in the path. If transferring signals through numbers of switches in a signal path, such as Fig. 3(b) the rooting delay of a line in a CMOS switch matrix interconnection network will increase quadratically with the distanceŒ8 . The typical solution for long lines is to use active devices to break up the lineŒ2 such as inserting inverters as buffers in the digital circuits. This way will burn more static power in the analog circuits. Due to the nonlinearity of Ron and the parasitic capaci- Figure 4(a) shows the proposed topology of the FPAA, which contains 2 2 homogenous CABs for example and the scale of CABs can be enlarged by cascading more stages. The interconnection lattice of CABs is composed of a square grid. The interconnection of a CAB with its adjacent CABs is complemented by connection boxes from four paths. The four connection paths to each CAB can meet demands of most analog circuits. The detailed structure of a CAB and a connection box (CB) are shown in Fig. 4(b). The CAB is composed of a railto-rail input and output op-amp (OPA) and a feedback switch (SW), as shown in the grey circle. The SW is controlled by the selected global clock signal or static configured by the shift registers. The dashed circle line in a CAB is the input node of the CAB and the real circle line represents the output node of the CAB. The CB as shown in the ashen quadrate box is composed of versatile passive elements including a programmable resistor array (PRA), a programmable capacitor array (PCA), two switches connected to the reference voltage and four input and output interconnection switches to connect with adjacent CABs. Most SC circuitsŒ10; 11 require an average 2–3.5 PCAs per OPA. Therefore, the ratio of PCAs to OPAs in this FPAA is 2, which meets the average value and achieves high area utilization without extra PCAs. As illustrated in Fig. 4(b), the grey words IN1–IN4 and OUT1–OUT4 represent the input nodes and output nodes of the adjacent four CABs respectively. The output ports a and c of a CB as shown in Fig. 4(b) are connected with the CAB’s input node (IN0) and the adjacent right CAB’s input node (IN1) respectively. The input ports b and c of the CB are connected with the CAB’s output node (OUT0) and the adjacent right 105011-3 J. Semicond. 2014, 35(10) Cheng Xiaoyan et al. Fig. 4. (a) The high-level architecture of FPAA. (b) Structure of a CAB and zoomed view for a connection box (CB). CAB’s output node (OUT1). So the CBs can be configured as the self feedback CB element in a CAB or in the adjacent CAB, or can also be the interconnection CB element between a CAB and the adjacent CAB. This design of the CB architecture extremely utilizes the PCA/PRA resources and saves the area of the chip. The six switches in the CB are controlled by a global clock signal or are static configured by shift registers. The PCA with four programmable switches can work as a switchedcapacitor (SC) element at four modes by programming, “on”, “off”, “positive resistor” and “negative resistor” respectively, as shown in Fig. 5. In this chip, the clock signal is generated by a conventional loop oscillator and then divided by D-registers to create 2 MHz, 1 MHz, 500 kHz and 250 kHz clock signals for DT circuit implementations. The CB when configured as a capacitor can be used for the frequency compensation in the transimpedance amplifier configuration. To extend the programming range, the capacitor value in a PCA can be chosen between 1–25 unit capacitors. The unit capacitor value is defined by the desired signal-to noise ratio (SNR) and power dissipation for these elements. For higher area utilization, each CB in one row is shared Fig. 5. Four configurations of a SCB. (a) Off configuration. (b) Capacitor configuration. (c) Positive resistor configuration. (d) Negative resistor configuration. with the other two adjacent rows as shown in Fig. 6. CB1 is originally connected with CAB11 and CAB12. For higher area utilization, the CB1 is also connecting with CAB21 and CAB22, CAB01 and CAB02. So each two CABs can implement three connection feedbacks by adjacent CBs to maximize utilization of CBs and improve application flexibility. Then the input node of one CAB connects 12 switches totally and the 105011-4 J. Semicond. 2014, 35(10) Cheng Xiaoyan et al. plement adder/subtractor, integrator/differentiator and SC programmable filters in DT mode. This version of FPAA did not design specific I/O blocks. Signals from outside are directly input to CBs and output signals directly from OPAs in the CABs around the chip. 3.2. Detailed schematic of the rail to rail operational amplifier Fig. 6. The proposed architecture of FPAA for highly routable CB utilization in single column. extracted capacitance of the input node of one CAB is about 150–320 fF changing with the states of switches connected to the node. The main characteristic of the proposed interconnection network is that the number of switches for making a connection between the input/output of an OPA and a capacitor is reduced to only one switch. Due to the utilization of the connection switches as the switches required in a normal SC circuit, the settling time is approximately the same as a normal SC circuit. The clock frequency of SC circuits in this FPAA can reach the range of MHz or a higher frequency. The maximum bandwidth of a signal passing through two switches and one input node and one output node has been found to be 265 MHz. Comparing with hexagonal lattice composed OTA connection pathsŒ2 , which can implement all orders of feedback in the interconnect network, the proposed CAB can provide more complex analog functions with high flexibility in functions by the abundant passive resources in CBs. The PRA in a CB is mainly for CT applications and combining the PCA resources, the FPAA can both operate at CT and DT operational modes to support high flexibility for different application demands. In CT mode, a single CAB can implement a transimpedance amplifier, programmable gain amplifier, buffer and CT filters. In DT mode, a CAB can be flexibly configured as a single biquadratic circuit by PCA resources. This particular biquadratic configuration allows any two-pole, two-zero system to be synthesized simply by controlling the size of the capacitors and the frequency of switches in the CBs. Within a single CAB of this FPAA, it can im- To widen the processing signal range and obtain an acceptable dynamic range in different applications, a rail to rail input and output amplifier is adopted as the core amplifier. For a rail to rail input, utilize a complementary input stage with both NMOS and PMOS differential pairs in parallel in this FPAA. However, the transconductance (gm / of the complementary input stage varies by the square root of two over the input common-mode voltage range (Vicm / sweeping from the negative (Gnd) to the positive (Vdd / supply voltage. The large variations of transconductance of the input stage will lead to drawbacks such as no optimal amplifier frequency compensation. The detailed schematic of the constant-gm control circuit shown in Fig. 7 is the same as in Ref. [12] but giving a new operation principle. The control circuit consists of two seriesconnected transistors (MP6–MP5 and MN6–MN5) and two current mirrors (MP3–MP4 and MN3–MN4) as shown in grey area in Fig. 7. To keep a constant gm , the current of NMOS differential input pair when the Vicm closest to Vdd should be about four times comparing the transition region. The transistor MP5 series-connected with MP6 turns on only when the Vgs voltage of MP5 is higher than its threshold voltage, which means the voltage of the VP node will be a threshold voltage higher than the IPP node, which is biased by the gate voltage of MP7. The current mirror consisting of MP7 and MP6 series-connected with MP5 begins working and PMOS input differential pairs are off. If the size of MP5 is the same as MP6 and the ratio of MP6 to MP7 also is 1 : 1, then the current proportion of MP7 to MP6 series-connected with MP5 becomes as Eq. (4). ˇ ˇ 1 IMP7 ˇˇ IMP7 ˇˇ ; (4) D IMP6 ˇVicm D Vdd 2 IMP6 ˇtransition region ˇ ˇ IMN7 ˇˇ 1 IMN7 ˇˇ : (5) D IMN6 ˇVicm D Gnd 2 IMN6 ˇtransition region The ratio of 1/2 comes from the W=L value of MP5 seriesconnected with MP6 is 1/2 of MP7. To support 3 times extra current to NMOS input differential pairs, the size proportion of MN3 and MN4 should be 6 : 1. Then the total tail current of NMOS input differential pairs is four times when Vicm is in the transition region. This process is identically repeated when the Vicm closes to Gnd. As Equation (5) shows, the size proportion of MN3 and MN4 should also be 6 : 1. Figure 7 shows the whole schematic of the OPA in a CAB which employs the class-AB single output stage for a large output voltage swing and strong driving capability. Figure 8 shows the total input stage gm versus Vicm from 0–3.3 V. The variation of gm in the total input stage is kept within ˙7.9% over the entire Vicm voltage range, which is comparable with prior worksŒ12 14 . Table 1 shows the performance of OPA used in 105011-5 J. Semicond. 2014, 35(10) Cheng Xiaoyan et al. Fig. 7. The schematic of rail to rail low power class-AB amplifier. cuit diagram of the reconstruction filter of the FPAA is shown in Fig. 9(a). The –3 dB bandwidth of the reconstruction filter is programmable according to the sample clock frequency. Each resistor and capacitor in the reconstruction filter is programmable for the different sampling clocks. Configuration register in this FPAA shown in Fig. 9(b) is built by shift registers. The configuration bit string is stored in a shift register to configure the connectivity of the local interconnection network and to program the functionality of the CABs. The configuration registers have been inserted in each CAB for better connectivity. 4. Prototype measurements 4.1. Layout and configuration software interface Fig. 8. Input stage gm versus Vicm of proposed OPA. Table 1. Performances of rail to rail amplifier in unity-gain inverting configuration with 32 pF || 800 Ω load. (Technology: 0.18 m CMOS, VDD D 3.3 V) Parameter Value Bias current (A) 20 DC gain (dB) 128 GBW(MHz) 23 ı Phase margin 74 p( ) Noise (nV/ Hz) @ 10 kHz 80 THD (dB) @ fin D 10 kHz 81 (VDD 0.2; VSS C 0.2) Power consumption (mA) 1.6 this FPAA. This constant-gm control circuit needs no extra biasing circuit and no extra static power consumption when Vicm in the large middle range of supply voltage comparing the traditional methods like the three times current mirrorŒ13 . This version of FPAA was implemented in 0.18-m standard CMOS technology with a 3.3 V power supply and contains two CABs with the proposed interconnection network to characterize the large-scale FPAA architecture explored in this paper. In this version of FPAA, there are about 128 switches for two CABs. As shown in Fig. 10, the core chip size is 2.4 1 mm2 including the reconstruction filter, reference source, configuration registers and non_overlapping clock generator modules. To easily configure the FPAA for users and direct programming from a PC, simple Matlab graphical user interface (GUI) configuration software has been developed for the FPAA. The configuration flow is shown in Fig. 11. A custom library of analog signal processing blocks for the FPAA is built and users just implement the circuits by Matlab GUI without knowing the details of the FPAA design. Configuration data generated by the Matlab procedure is downloaded into FPAA by an Altera DEII115 development board through the SPI interface. The clock of the SPI interface is 50 MHz and the whole configuration procedure is done in about 2.6 s. 3.3. Other components circuitry The reconstruction filter is inserted in this FPAA to be used as a smoothing filter in the DT mode and the structure was based on the multiple feedback low pass filter. The cir- 4.2. Measurement results and application examples To validate the proposed architecture, four application examples were physically mapped in the FPAA and measure- 105011-6 J. Semicond. 2014, 35(10) Cheng Xiaoyan et al. Fig. 9. (a) The circuit diagram of reconstruction filter and (b) the architecture of configuration bit stream registers. 4.3. Implementation of PGA circuit and test results The two-stage PGA was mapped in the FPAA as shown in Fig. 12 to demonstrate the CT signal processing capability of the FPAA. The resistance value of PRA can be programmed among 1–25 unit resistors. In the measurement circuit, set R1 =R0 D R3 =R2 D 2. So ideally Vout D 4Vin . Figure 13(a) shows the transient output waveform with 2 MHz input sine signal with amplitude varying from 0.1–0.4 V. From the test results shows that the analog signal input range of the PGA reaches 1.65 ˙ 1 V with a 1.7 deviation from linearity. The max peak to peak output voltage swing can be increased up to 3.3 V. Figure 13(b) illustrates the spurious free dynamic range (SFDR) test of the PGA with a 2 MHz input sine signal. The maximum SFDR reaches 54 dB and the overall signal range can be extrapolated to be 70 dB over the noise level. The static current of the PGA circuit is about 3.2 mA. Compared with the DT mode, the CT mode of the FPAA can process a signal bandwidth up to 2 MHz or a higher bandwidth defined by the OPA bandwidth while not being limited by the bandwidth of the interconnected network. Fig. 10. Die microphotograph of the fabricated FPAA. 4.4. Implementation of a switched capacitor adder Fig. 11. Matlab GUI configuration tool. ment results were given. We firstly present a PGA circuit, and then an adder circuit, finally, two kinds of programmable biquadratic filters. These circuits have been chosen to characterize the FPAA of both CT and DT analog signal processing capabilities. To demonstrate the capabilities of the proposed FPAA in implementing flexible DT circuit structures, an adder and biquadratic SC filters were built to test. The schematic of the adder shown in Fig. 14(a) was embedded in the proposed architecture, as shown in Fig. 14(b). The CF capacitor bank is two times larger than the Cin1 and Cin2 banks in the test example. Ideally, the Vout D Cin1 =CF (Vin1 C Vin2 / D 12 (Vin1 C Vin2 /. Figure 15(a) illustrates the measured results of the transient output signal of the adder with 10 kHz (Vin1 / and 40 kHz (Vin2 / input sine signals. From Fig. 15(a), we can see that the measured result was nearly equal to the math equation (Math1 D 105011-7 J. Semicond. 2014, 35(10) Cheng Xiaoyan et al. Fig. 12. (a) Circuit diagram of two stages PGA and (b) PGA mapped in FPAA. Fig. 14. (a) The schematic of SC adder circuit and (b) the adder circuit mapped in FPAA. (Vin1 C Vin2 //2) built by the oscilloscope. Figure 15(b) shows the precision test of the adder circuit, which sets the Vin1 D Vin2 . So Vout D Vin1 ideally. From the test result, we can get the relative accuracy of SC adder circuits, which is about 96.4% with a large input signal swing from 0.4–3.3 V without considering offset. About 54 mV offset voltage exists in the SC adder, which can be minimized by adopting differential circuits and taking some techniques as correlated double sampling for further cancellation. Due to only employing one amplifier, the static current of the adder circuit is about 1.6 mA. 4.5. Implementation of biquadratic filters The proposed architecture is capable of implementing different kinds of filters. Figure 16 shows the schematic of the second order band pass filter, which was implemented by the FPAA. The transfer function of the second order band pass filter is given by Fig. 13. Test results of PGA. (a) Transient output waveform and (b) power spectral density of PGA with an input sinusoidal wave of 2 MHz @ gain D 4. 105011-8 H.s/ D S2 C1 CB Sfs C 2 CA CB 1 C4 C3 C2 C3 C2 4 2C2 J. Semicond. 2014, 35(10) Cheng Xiaoyan et al. Fig. 15. (a) Transient test result with 1 MHz sample clock and (b) precision test results of adder circuit. Fig. 16. (a) Programmable biquadratic switched capacitor band pass filter and (b) the band pass filter mapped in FPAA. " C4 fs S CA CB 1 C4 C2 C3 C2 4 2C2 # 1 fs2 ; C CA CB 1 C4 C3 C2 4 2C2 S2 C 8 ˆ C2 CA CB ˆ ˆ Q D ˆ ˆ C4 C3 C2 ˆ < 1 ˆ fc D ˆ ˆ 2 C C ˆ ˆ A B :̂ C3 C2 1 4 C4 2C2 fs 1 4 C4 2C2 12 ; GD (6) C1 CB ; C4 C3 12 ; (7) where fc is the center frequency, fs is the clock frequency, Q is the quality factor, and G is the gain. By programming the size of capacitors and clock frequency, a different center frequency and gain of filters can be realized. In the test circuit, Q D 5, G D 1, fs D 1 MHz are set respectively and the center frequency is changed through Matlab GUI to generate different configuration data and download it into the FPAA. Then the programmable center frequency of the second order band pass filter in the FPAA is realized by programming the size of capacitors. Figure 17 plots the frequency response results of the band pass filters measured by the E5061B series network analyzer. The solid line is the measurement results and the dashed line is the theoretical frequency Fig. 17. Measured frequency responses of the second order programmable band pass filters varying with fc . response as Eq. (6). As shown in Fig. 17, no significant differences are observed between the embedded circuit and the ideal software realization. Since the architecture is stray-insensitive, the parasitic capacitances have no significant effects on the transfer function. The resonance frequency of the band pass filter varies from 10 to 100 kHz showing a large programming range. The deviations in the high frequency response of the measurements from the ideal transfer function are mainly affected by the reconstruction filter whose –3 dB bandwidth is about 250 kHz. The higher order band pass filters can be designed in a similar way by just cascading more CABs. Figure 18 shows the SFDR test of the bandpass filter cascading 105011-9 J. Semicond. 2014, 35(10) Cheng Xiaoyan et al. Fig. 18. Power spectral density of bandpass filter with an input sinusoidal wave of 50 kHz and Vpp D 2 V @ fs D 1 MHz. Fig. 20. Measurement of programmable high pass filters transfer functions with different corner frequencies. frequency response generated by Matlab. Figure 20 shows that the measured corner frequency from the FPAA matches well with theory simulation results. The corner frequency of the high pass filter varies from 4–120 kHz showing a large tuning range by tuning capacitors and sampling clock frequency. The slight deviations of the measurements from the simulations shown in Fig. 20 are within the expected manufacturing process variations. The total static current of the biquadratic filters cascading reconstruction filter is about 5 mA. The maximum corner frequency deviation of the high pass filter and center frequency deviation of the band pass filter are about 8.5% and 8.3% respectively showing the high accuracy of the SC circuit implementations. 5. Conclusion Fig. 19. (a) The schematic of second order switched capacitor high pass filter and (b) the high pass filter mapped in FPAA. reconstruction filter with 50 kHz input sine signal and the peak to peak amplitude of the signal is 2 V at the 1 MHz sampling clock. The maximum SFDR reaches 45 dB and the overall signal range can be extrapolated to be about 60 dB over the noise level. To emphasize the diversity of the possible filters on the array, Figure 19(a) shows the schematic of a second order inverse Butterworth high pass filter. Figure 19(b) shows that the high pass filter was mapped in the FPAA. Also the solid line represents the measurement results and the dashed line is the ideal A flexible architecture of FPAA based on a new interconnection network was proposed. By working on dual mode, the architecture can provide versatile analog functions; it not only works in CT mode with a wide signal bandwidth not limited by the Nyquist criterion but it can also work in DT mode with high flexibility and accuracy. In order to reduce nonidealities of CMOS switches, the FPAA employs a flexible interconnection layout lattice and connection boxes to minimize the number of switches in signal paths. For high area utilization, the ratio between PCAs and OPAs in this FPAA is selected to be about 2 within the average value 2–3.5 in normal SC circuits and each CB in one column/row is shared with adjacent columns/rows. The CAB of the proposed FPAA adopts a rail to rail input and output operational amplifier with a new simple low power constant-gm principle for the large signal dynamic range. Both CT operation mode and DT operation mode examples implemented on this FPAA were demonstrated in this paper. The test results show that the proposed FPAA have high flexibility and good performance compared with other works. Up to now, there is still no concrete and direct performance metric to compare the different FPAA designs. Table 2 shows the main characteristics comparison with other FPAA chips. It is shown that the proposed FPAA has good performances with a large input range, high precision, high bandwidth and linearity. Next, work should be taken to enlarge the scale for more analog functions and adopt a full differential operational mode 105011-10 J. Semicond. 2014, 35(10) Parameter Process (m) Power supply (V) CAB elements Input Vpp (V) SFDR (dB) Cheng Xiaoyan et al. Table 2. Comparison to prior designs. This work Ref. [15] Ref. [2] 0.18 0.18 0.13 3.3 3.3 1.2 An operational amplifier RAPU1, RAPU2 7 digitally tuning and a switch transconductors 3.3 54 @ 2 MHz (two stage PGA @ gain D 4) 96.4 265 1.8 — 0.141 50 @ 20 MHz (lossy integrator) Ref. [16] 0.35 floating-gate 2.4 2 FG-OTAs, 2 TGATEs, 2 capacitors, 2 FETs, 2 MITEs 0.4 39.2 @ 20 kHz (2nd order sigma delta) 99.5 — — 100 — 57 Relative precision (%) Max. bandwidth of interconnection network (MHz) Max. clock freq. in DT mode (MHz) Features 2 0.8 — 2.5 CT & DT modes CT&DT modes Application Analog signal processing Analog signal processing Hexagonal lattice, only CT mode Only filter design Mixed-signal array, only CT mode Mixed-signal processing The maximum clock frequency in DT mode of the FPAA is 2 MHz due to the fact that the unit capacitor value in the PCA was chosen to be a little large. Due to not building the test environment, the value is the result of post simulation. with some offset cancel techniques. References [1] Sivilotti M A. A dynamically configurable architecture for prototyping analog circuits. Proceedings of the Fifth MIT Conference on Advanced Research in VLSI, MIT, 1988: 237 [2] Becker J, Henrici F, Trendelenburg S, et al. A fieldprogrammable analog array of 55 digitally tunable OTAs in a hexagonal lattice. IEEE J Solid-State Circuits, 2008, 43(12): 2759 [3] Stoica A, Zebulum R, Keymeulen D, et al. Reconfigurable VLSI architectures for evolvable hardware: from experimental field programmable transistor arrays to evolution-oriented chips. IEEE Trans Very Large Scale Integration (VLSI) Systems, 2001, 9(1): 227 [4] Lee E K F, Gulak P G. A CMOS field-programmable analog array. IEEE J Solid-State Circuits, 1991, 26(12): 1860 [5] Basu A, Brink S, Schlottmann C, et al. A floating-gate-based field-programmable analog array. IEEE J Solid-State Circuits, 2010, 45(9): 1781 [6] Luo J. Circuit design and routing for field programmable analog arrays. Doctor of Philosophy, Department of Electrical and Computer Engineering, University of Maryland, 2005 [7] Cheng X Y, Yin T, Wu Q S, et al. A CMOS FIELD programmable analog array for intelligent sensory application. 23rd International Conference on Field Programmable Logic and Applications, Porto, Portugal, 2013: 2 [8] Hasler P E, Twigg C M. An OTA-based large-scale field programmable analog array (FPAA) for faster on-chip communication and computation. IEEE International Symposium on Circuits and Systems, 2007: 177 [9] Brown T W, Fie T S Z, Hakkarainen M. Prediction and characterization of frequency dependent MOS switch linearity and the design implications. CICC, 2006 [10] Gregorian R, Temes G C. Analog MOS integrated circuits for signal processing. John Wiley & Sons, 1986 [11] Mohan P V A, Ramachandran V, Swamy M N S. Switched capacitor filters: theory, analysis and design. Prentice Hall, 1995 [12] Moldovan L, Li H H. A rail-to-rail, constant gain, buffered opamp for real time video applications. IEEE J Solid-State Circuits, 1997, 32(2): 169 [13] Hogervorst R, Tero J P, Eschauzier R G H, et al. A compact power-efficient 3 V CMOS rail-to-rail input/output operational amplifier for VLSI cell libraries. IEEE J Solid-State Circuits, 1994, 29(12): 1505 [14] Carrillo J M, Duque-Carrillo J F, Torelli G, et al. Constantgm constant-slew-rate high-bandwidth low-voltage rail-to-rail CMOS input stage for VLSI cell libraries. IEEE J Solid-State Circuits, 2003, 38(8): 1364 [15] Fu W H, Jiang J, Qin X, et al. A reconfigurable analog processor using coarse-grained, heterogeneous configurable analog blocks for field programmable mixed-signal processing. Analog Integr Circuits Signal Process, 2011, 2011(68): 93 [16] Wunderlich R B, Adil F, Hasler P. Floating gate-based field programmable mixed-signal array. IEEE Trans Very Large Scale Integration (VLSI) System, 2013, 21(8): 1496 105011-11