Current Mirrors - Analog IC Design.org

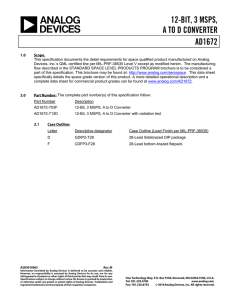

advertisement

Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-1 LECTURE 160 – CURRENT MIRRORS AND SIMPLE REFERENCES LECTURE ORGANIZATION Outline • MOSFET current mirrors • Improved current mirrors • Voltage references with power supply independence • Current references with power supply independence • Temperature behavior of voltage and current references CMOS Analog Circuit Design, 2nd Edition Reference Pages 134-153 CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-2 MOSFET CURRENT MIRRORS What is a Current Mirror? A current mirror replicates the input current of a current sink or current source as an output current. The output current may be identical to the input current or can be a scaled version of it. VDD iIN VDD iOUT = KiIN VDD iin IOUT = KIIN Kiout IIN iOUT iIN Current Mirror VDD Current Mirror 060528-01 The above current mirrors are referenced with respect to ground. Current mirrors can also be referenced with respect to VDD and current sink inputs and outputs. CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-3 Characterization of Current Mirrors A current mirror is basically nothing more than a current amplifier. The ideal characteristics of a current amplifier are: • Output current linearly related to the input current, iout = Aiiin • Input resistance is zero • Output resistance is infinity Also, the characteristic VMIN applies not only to the output but also the input. • V MIN(in) is the range of vin over which the input resistance is not small • V MIN(out) is the range of vout over which the output resistance is not large Graphically: iout iin iout iin + vin - iout Current Mirror Slope = 1/Rout Slope = 1/Rin + vout - Ai 1 VMIN(in) iin vin Input Characteristics Transfer Characteristics vout VMIN(out) Output Characteristics Fig. 300-01 Therefore, Rout, Rin, VMIN(out), VMIN(in), and Ai will characterize the current mirror. CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-4 Simple MOS Current Mirror Circuit: iI iO + vDS1 M2 M1 + vGS - Assume that vDS2 > vGS - VT2, then iO L1W 2V GS-V T221+vDS2 K2’ iI = W 1L2 V GS-V T1 1+vDS1K1’ If the transistors are matched, then K1’ = K2’ and VT1 = VT2 to give, iO L1W 21+vDS2 iI = W 1L2 1+vDS1 If vDS1 = vDS2, then iO L1W 2 iI = W 1L2 Therefore the sources of error are: 1.) vDS1 vDS2 2.) M1 and M2 are not matched. CMOS Analog Circuit Design + vDS2 Fig. 300-02 © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-5 Influence of the Channel Modulation Parameter, If the transistors are matched and the W/L ratios are equal, then iO 1+vDS2 iI = 1+vDS1 if the channel modulation parameter is the same for both transistors (L1 = L2). Ratio error (%) versus drain voltage difference: Measure VDS1,VDS2, iI and iO and solve the above equation for the channel modulation parameter, . 1 + λ vDS2 Ratio Error ⎡ ⎢ ⎣ 1 + λ vDS1 Note that one could use this effect to measure . ⎤ − 1 ⎥ × 100 % ⎦ 8.0 7.0 λ= 0.02 λ= 0.015 λ= 0.01 Ratio Error vDS2 - vDS1 (volts) 6.0 5.0 4.0 3.0 2.0 1.0 vDS1 = 2.0 volt 0.0 2.0 3.0 vDS2 - vDS1 (volts) 1.0 0.0 Fig. 300-03 CMOS Analog Circuit Design 4.0 5.0 © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-6 Illustration of the Offset Voltage Error Influence Assume that VT1 = 0.7V and K’W/L = 110μA/V2. iI = 1μA i Ratio Error ⎡ O − 1 ⎤ × 100 % ⎢ ⎥ ⎣ ii ⎦ 16.0 14.0 12.0 10.0 iI = 3μA 8.0 iI = 5μA 6.0 iI = 10μA 4.0 2.0 iI = 100μA 0.0 0.0 1.0 2.0 3.0 4.0 5.0 6.0 ΔVT (mV) 7.0 8.0 9.0 10 Fig. 300-4 Key: Make the part of VGS causing the current to flow, VON, more significant than VT. CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-7 Influence of Error in Aspect Ratio of the Transistors Example 160-1 - Aspect Ratio Errors in Current Mirrors A layout is shown for a one-to-four current amplifier. Assume that the lengths are identical (L1 = L2) and find the ratio error if W1 = 5 ± 0.1 μm. The actual widths of the two transistors are W 1 = 5 ± 0.1 μm and W2 = 20 ± 0.1 μm iI i Solution i i M2 M1 We note that M1 M2 the tolerance + + VDS2 VDS1 is not multi+ GND VGS plied by the nominal gain Fig. 300-5 factor of 4. The ratio of W 2 to W 1 and consequently the gain of the current amplifier is iO W 2 20±0.1 1±(0.1/20) 0.1 ±0.1 0.1 ±0.4 4 1± 1 4 1± = = = 4 1±(0.1/5) 20 5 20 - 20 = 4 - (±0.03) iI W 1 5±0.1 where we have assumed that the variations would both have the same sign (correlated). It is seen that this ratio error is 0.75% of the desired current ratio or gain. O O I ;;;;;;;;;; CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-8 Influence of Error in Aspect Ratio of the Transistors-Continued Example 160-2 - Reduction of the Aspect Ratio Errors in Current Mirrors Use the layout technique illustrated below and calculate the ratio error of a current amplifier having the specifications of the previous example. Solutions The actual widths of M1 and M2 are W 1 = 5 ± 0.1 μm and W2 = 4(5 ± 0.1) μm The ratio of W 2 to W 1 and consequently the current gain is given below and is for al practical purposes independent of layout error. iO 4(5±0.1) iI = 5±0.1 = 4 ;; ; ;; ;; ;; ; ;;;; ;; ; ;; ;; ;;;;;; ; iI M2a GND CMOS Analog Circuit Design M2b M1 iO M2c ;; ;; M2d iI iO M1 M2 GND Fig. 300-6 © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-9 Summary of the Simple MOS Current Mirror/Amplifier • Minimum input voltage is VMIN(in) = VT+VON Okay, but could be reduced to VON. Principle: VDD M5 M6 M7 Ib Ib Ib M3 M4 iI iI VT VT + M1 VON + - VT+VON - iO + M1 VON - + VT+VON - iO M2 M2 Ib Fig. 300-7 Will deal with later in low voltage op amps. • Minimum output voltage is VMIN(out) = VON 1 • Output resistance is Rout = ID 1 • Input resistance is Rin gm • Current gain accuracy is poor because vDS1 vDS2 CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-10 IMPROVED CURRENT MIRRORS Large Output Swing Cascode Current Mirror IIN iin R M4 1/4 VDD VDD VDD 1/1 IOUT M5 D5=G3 M2 + gm5vgs5 1/1 M3 1/1 iout iin M1 1/1 rds5 vin gm3vgs3 = gm3vin - D3=S5 + rds3 vs5 S3=G5 - • Rout gm2rds2rds1 060528-02 • Rin = ? vin = rds5(iin-gm5vgs5)+vs5 = rds5(iin +gm5vs5)+vs5 = rds5iin+(1+gm5rds5)vs5 But, vs5 = rds3(iin - gm3vin) vin = rds5iin + (1+gm5rds5)rds3iin - gm3rds3(1+gm5rds5)vin vin rds5+rds3+rds3gm5rds5 1 Rin = iin = gm3rds3(1+gm5rds5) gm3 • V MIN(out) = 2VON • V MIN(in) = VT + VON • Current gain is excellent because vDS1 = vDS3. CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-11 Self-Biased Cascode Current Mirror VDD VDD I1 iin I2 iout i in + R gm3vgs3 • Rin = ? R + + M4 M3 vin = iinR + rds3(iin-gm3vgs3) rds3 vin + + rds1(iin-gm1vgs1) vin v2 M2 M1 v1 gm1vgs1 rds1 But, vgs1 = vin-iinR and Small-signal model to calculate Rin. vgs3 = vin-rds1(iin-gm1vgs1) Self-biased, cascode current mirror Fig. 310-03 = vin-rds1iin+gm1rds1(vin-iinR) vin = iinR+rds3iin-gm3rds3[vin-rds1iin+gm1rds1(vin-iinR)]+rds1[iin-gm1(vin+iinR)] vin[1+gm3rds3+gm1rds1gm3rds3+gm1rds1] = iin[R+rds1+rds3+gm3rds3rds1+ gm1rds1gm3rds3R] R+rds1+rds3+gm3rds3rds1+gm1rds1gm3rds3R 1 Rin = gm1 + R 1+gm3rds3+gm1rds1gm3rds3+gm1rds1 • Rout gm4rds4rds2 • V MIN(in) = VT + 2VON •V MIN(out) = 2VON • Current gain matching is excellent CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-12 MOS Regulated Cascode Current Mirror I ii I VDD IBias VDD VDD IO io M3 M1 M4 M2 FIG. 310-11 • Rout gm2rds3 1 • Rin g m4 • V MIN(out) = VT+2VON (Can be reduced to 2VON) • V MIN(in) = VT+VON (Can be reduced to VON) • Current gain matching - good as long as vDS4 = vDS2 CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-13 Summary of MOS Current Mirrors Current Mirror Accuracy Output Resistance Input Resistance Simple Poor rds Wide Output Swing Cascode Self-biased Cascode Regulated Cascode Excellent gmrds2 1 gm 1 gm Excellent gmrds2 GoodExcellent gm2rds3 1 R+g m 1 gm Minimum Output Voltage V ON Minimum Input Voltage V T+VON 2VON V T+VON 2VON V T+2VON V T+2VON (Can be 2VON) V T+VON (Can be VON) CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-14 VOLTAGE REFERENCES WITH POWER SUPPLY INDEPENDENCE Power Supply Independence How do you characterize power supply independence? Use the concept of: VREF V REF/V REF V DD V REF S VDD = V DD/V DD = V REF VDD Application of sensitivity to determining power supply dependence: V REF VREF V DD V REF = S VDD V DD Thus, the fractional change in the reference voltage is equal to the sensitivity times the fractional change in the power supply voltage. For example, if the sensitivity is 1, then a 10% change in VDD will cause a 10% change in V REF. VREF Ideally, we want S V CMOS Analog Circuit Design DD to be zero for power supply independence. © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-15 MOSFET-Resistance Voltage References VDD VDD R R + R1 + vout VREF VREF - R2 Fig. 370-03 2(VDD-V REF) V REF = VGS = VT + R or 2(VDD-V T) 1 1 V REF = VT - R + + R (R)2 VREF V DD 1 S VDD = 1+2(V -V )RVREF DD T This circuit allows VREF to be larger. If the current in R1 (and R2) is small compared to the current flowing through the transistor, then R +R 2 1 V REF R VGS 2 Assume that VDD=5V, W/L =100 and R=100k, VREF S VDD Thus, VREF 0.7875V and = 0.0653 CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-16 Bipolar-Resistance Voltage References VCC VCC R R VREF VREF R2 s kT I VREF = VEB = q ln I V CCVEB V CC and I = R R kT V CC give V REF q ln RIs VREF 1 1 SVCC = ln[VCC/(RIs)] = ln(I/Is) If VCC = 5V, R = 4.3k and Is = 1fA, then VREF = 0.719V. VREF Also, S V CC CMOS Analog Circuit Design = 0.0362 + R1 + vout Fig. 370-04 If the current in R1 (and R2) is small compared to the current flowing through the transistor, then R +R 1 2 V REF R1 VEB Can use diodes in place of the BJTs. © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-17 CURRENT REFERENCES WITH POWER SUPPLY INDEPENDENCE Power Supply Independence Again, we want IREF IREF/IREF V DD IREF S VDD = VDD/V DD = IREF VDD to approach zero. IREF Therefore, as S V DD approaches zero, the change in IREF as a function of a change in V DD approaches zero. CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-18 Gate-Source Referenced Current Reference The circuit below uses both positive and negative feedback to accomplish a current reference that is reasonably independent of power supply. Circuit: VDD RB M7 M4 I2 I1 Startup M1 I5 I6 M6 + VGS1 R - 0V 2 K'NW (V GS1 - VT) 2L Desired operating V point I2 = GS1 R I1 = M5 M3 M2 M8 i IQ Undesired operating point VQ v Fig. 370-06 Principle: If M3 = M4, then I1 I2. However, the M1-R loop gives VGS1=VT1 + 2I1 KN’(W 1/L1) V GS1 V T1 1 2I1 R = R + R KN’(W 1/L1) V T1 2VT1 1 1 1 The output current, Iout=I1=I2 can be solved as Iout= R + + + 1R ( R)2 1R2 R 1 Solving these two equations gives I2 = CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-19 Simulation Results for the Gate-Source Referenced Current Reference 120μA ID1 100μA ID2 80μA 60μA 40μA 20μA 0 0 1 2 VDD 3 4 5 Fig. 370-07 Simple, Bootstrap Current Reference VDD 1 0 DC 5.0 VSS 9 0 DC 0.0 M1 5 7 9 9 N W=20U L=1U M2 3 5 7 9 N W=20U L=1U M3 5 3 1 1 P W=25U L=1U M4 3 3 1 1 P W=25U L=1U M5 9 3 1 1 P W=25U L=1U R 7 9 10KILOHM M8 6 6 9 9 N W=1U L=1U M7 6 6 5 9 N W=20U L=1U The current ID2 appears to be okay, why is ID1 increasing? Apparently, the channel modulation on the current mirror M3-M4 is large. At VDD = 5V, VSD3 = 2.83V and VSD4 = 1.09V which gives ID3 = 1.067ID4 107μA Need to cascode the upper current mirror. SPICE Input File: RB 1 6 100KILOHM .OP .DC VDD 0 5 0.1 .MODEL N NMOS VTO=0.7 KP=110U GAMMA=0.4 +PHI=0.7 LAMBDA=0.04 .MODEL P PMOS VTO=-0.7 KP=50U GAMMA=0.57 +PHI=0.8 LAMBDA=0.05 .PRINT DC ID(M1) ID(M2) ID(M5) .PROBE .END CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-20 Cascoded Gate-Source Referenced Current Reference VDD M3 120μA M4 M5 M3C MC4 MC5 RB M7 I1 RON I2 M2 M8 SPICE Input File: M1 Startup Cascode, Bootstrap Current Reference VDD 1 0 DC 5.0 VSS 9 0 DC 0.0 M1 5 7 9 9 N W=20U L=1U M2 4 5 7 9 N W=20U L=1U M3 2 3 1 1 P W=25U L=1U M4 8 3 1 1 P W=25U L=1U M3C 5 4 2 1 P W=25U L=1U MC4 3 4 8 1 P W=25U L=1U RON 3 4 4KILOHM M5 9 3 1 1 P W=25U L=1U R 7 9 10KILOHM M8 6 6 9 9 N W=1U L=1U CMOS Analog Circuit Design + VGS1 R 0V I5 ID2 100μA 80μA ID1 60μA 40μA 20μA 0 0 1 2 VDD 3 4 5 Fig. 370- M7 6 6 5 9 N W=20U L=1U RB 1 6 100KILOHM .OP .DC VDD 0 5 0.1 .MODEL N NMOS VTO=0.7 KP=110U GAMMA=0.4 PHI=0.7 LAMBDA=0.04 .MODEL P PMOS VTO=-0.7 KP=50U GAMMA=0.57 PHI=0.8 LAMBDA=0.05 .PRINT DC ID(M1) ID(M2) ID(M5) .PROBE .END © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-21 Base-Emitter Referenced Circuit VDD M3 M4 M5 i2 M6 I 1 I2 M1 I5 M2 + VEB1 Q1 M7 R i2=i1 Undesired operating point + VR Startup i2=Vtln(i1/Is)/R Desired operating point i1 - - 070621-01 V EB1 Iout = I2 = R BJT can be a MOSFET in weak inversion. CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-22 Low Voltage Gate-Source Referenced MOS Current Reference The previous gate-source referenced circuits required at least 2 volts across the power supply before operating. A low-voltage gate-source referenced circuit: VDD VON M3 I1 M4 VT VT VT+VON I2 VON VT+VON M1 M2 R VSS VR Fig. 4.5-8A Without the batteries, VT, the minimum power supply is VT+2VON+VR. With the batteries, VT, the minimum power supply is 2VON+VR 0.5V CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-23 Summary of Power-Supply Independent References • Reasonably good, simple voltage and current references are possible • Best power supply sensitivity is approximately 0.01 (10% change in power supply causes a 0.1% change in reference) Type of Reference V REF IREF SV or S V PP PP 1 1 <1 <<1 <<1 <<1 Voltage division Simple Current Reference MOSFET-R BJT-R Gate-source Referenced Base-emitter Referenced CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-24 TEMPERATURE BEHAVIOR OF VOLTAGE AND CURRENT REFERENCES Characterization of Temperature Dependence The objective is to minimize the fractional temperature coefficient defined as, 1 V REF 1 VREF TCF = V REF T = T S T parts per million per °C or ppm/°C Temperature dependence of PN junctions: v iIsexpV t (lnIs) 3 V GO V GO 1 Is = = + -V GO Is T T T TVt TVt Is=KT3exp V t dvBE V BE-VGO = -2mV/°C at room temperature dT T (VGO = 1.205 V at room temperature and is called the bandgap voltage) Temperature dependence of MOSFET in strong inversion: dvGS dVT 2L d iD dT = dT + W CoxdT μo dv mV GS dT - -2.3 °C -1.5 μo=KT Resistors: V T(T)=VT(To)-(T-To) (1/R)(dR/dT) ppm/°C CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-25 V DD Bipolar-Resistance Voltage References R From previous work we know that, kT V DD-VREF + V REF = q ln RIs VREF However, not only is VREF a function of T, but R and Is are also Fig. 380-1 functions of T. dVREF k V DD-V REF kT RIs -1 dVREF V DD-V REF dR dIs dT = qln RIs + q VDD-V REF RIs dT - RIs RdT+IsdT V REF Vt dVREF dIs V REF-V GO Vt dVREF 3Vt V t dR dR = = T - V -V V + t RdT IsdT T V DD-V REF dT - T - R dT DD REF dT V REF-V GO dR 3Vt -V dVREF t T RdT- T V REF-V GO dR 3Vt dT = V t RdT - T Vt T 1+V DD-V REF 3Vt 1 dVREF V REF-V GO V t dR TCF = V REF dT = V REF·T - V REF RdT - V REF·T If VREF = 0.6V, Vt = 0.026V, and the R is polysilicon, then at 27°K the TCF is 0.6-1.205 0.026·0.0015 3·0.026 TCF = 0.6·300 - 0.6·300 = 33110-6-65x10-6-433x10-6 =-3859ppm/°C 0.6 CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) MOSFET Resistor Voltage Reference From previous results we know that 2(VDD-V REF) V REF = VGS = VT + R or 1 VREF = VT - R + 2(VDD-V T) 1 + R (R)2 Note that VREF, VT, , and R are all functions of temperature. It can be shown that the TCF of this reference is Page 160-26 VDD R + VREF Fig. 380-02 V DDVREF 1.5 1 dR dVREF + 2R T RdT dT = 1 1+ 2R(V V ) DD REF V DDVREF 1.5 1 dR 2R T RdT TCF = 1 V REF(1+ 2R(V V )) DD REF + CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-27 Example 160-3 - Calculation of MOSFET-Resistor Voltage Reference TCF Calculate the temperature coefficient of the MOSFET-Resistor voltage reference where W/L=2, VDD=5V, R=100k using the parameters of Table 3.1-2. The resistor, R, is polysilicon and has a temperature coefficient of 1500 ppm/°C. Solution dR First, calculate VREF . Note that R = 220x10-6x105 = 22 and RdT = 1500ppm/°C 1 V REF = 0.7 22 + 2(50.7) 1 2 22 +22 = 1.281V 51.281 1.5 -6 1500x10 300 dVREF 2 22 Now, = = -1.189x10-3V/°C 1 dT 1+ 222(5-1.281) The fractional temperature coefficient is given by 1 -3 TCF = 1.189x10 1.281 = 928 ppm/°C 2.3x10-3+ CMOS Analog Circuit Design Lecture 160 – Current Mirrors and Simple References (3/25/10) © P.E. Allen - 2010 Page 160-28 Gate-Source and Base-Emitter Referenced Current Source/Sinks Gate-source referenced source: V T1 2VT1 1 1 1 The output current was given as, Iout = R + R2 + R + R 1 (1R)2 1 Although we could grind out the derivative of Iout with respect to T, the temperature performance of this circuit is not that good to spend the time to do so. Therefore, let us assume that VGS1 VT1 which gives V T1 dIout 1 dVT1 1 dR dT = R dT - R2 dT Iout R In the resistor is polysilicon, then 1 dIout 1 dVT1 1 dR - 1 dR -2.3x10-3 TCF = Iout dT = V T1 dT - R dT = V T1 - R dT = 0.7 -1.5x10-3 = -4786ppm/°C Base-emitter referenced source: V BE1 The output current was given as, Iout = I2 = R 1 dVBE1 1 dR The TCF = V BE1 dT - R dT 1 If VBE1 = 0.6V and R is poly, then the TCF = 0.6 (-2x10-3) - 1.5x10-3 = -4833ppm/°C. CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-29 VDD Technique to Make gm Dependent on a Resistor Consider the following circuit with all transistors having a W/L = 10. This is a bootstrapped reference which creates a M3 M4 Vbias independent of VDD. The two key equations are: I 3 = I4 I 1 = I2 M2D and M1 + V GS1 = VGS2 + I2R M2A M2B M2CVBias Solving for I2 gives: R=5kΩ V GS1-V GS2 1 2I1 2I2 2I1 1 I2 = = R ß1 - ß2 = R ß 1-2 Fig. 4.5-11 R 1 1 1 1 I2 = R 2ß I2 = I1 = = = 18.18μA 2 -6 1 2ß1R 2·110x10 ·10·25x106 Now, Vbias can be written as 2I2 1 1 Vbias=VGS1= ß1 +VTN = ß1R+VTN = + 0.7 = 0.1818+0.7=0.8818V -6 110x10 ·10·5x103 Any transistor with VGS = Vbias will have a current flow that is given by 1/2ßR2. 2ß 1 1 Therefore, gm = 2Iß = = R gm=R 2 2ßR CMOS Analog Circuit Design © P.E. Allen - 2010 Lecture 160 – Current Mirrors and Simple References (3/25/10) Page 160-30 Summary of Reference Performance Type of Reference MOSFET-R BJT-R Gate-Source Referenced Base-emitter Referenced VREF S VDD TCF <1 <<1 Good if currents are matched Good if currents are matched >1000ppm/°C >1000ppm/°C >1000ppm/°C >1000ppm/°C Comments Requires startup circuit Requires startup circuit • A MOSFET can have zero temperature dependence of iD for a certain vGS • If one is careful, very good independence of power supply can be achieved • None of the above references have really good temperature independence Consider the following example: A 10 bit ADC has a reference voltage of 1V. The LSB is approximately 0.001V. Therefore, the voltage reference must be stable to within 0.1%. If a 100°C change in temperature is experienced, then the TCF must be 0.001%/C or multiplying by 104 requires a TCF = 10ppm/°C. CMOS Analog Circuit Design © P.E. Allen - 2010