Solutions for Final Exam

advertisement

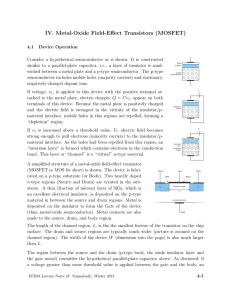

26% 1. For a common-source amplifier with degeneration resistor Rs as shown in Fig. 1, assume that it is operating at a bias current I = 150µA, with W/L = 10µm/0.5µm, V A′ = 15 V/µm, µnCox = 240µA/V2, χ = 0.2, and RL = 20 kΩ. Cgs = 1 pF, Cgd = 0.2 pF, CL = 2 pF, Rsig = 20 kΩ. A) Find gm, ro. (2% each) B) If the resistor Rs = 1.945 kΩ is connected in the source, Find the ratio vgs/vi. (2%) C) Follow the condition in B), find Rin, Rout, Avo, Av, Gm. (2% each) D) Find fH, ft. (3% each) E) Explain the effect of Rs compared with general CS amplifier. (4%) Ans: Fig. 1 A CS amplifier with degeneration resistor Rs. A) g m = 2k n′ (W / L )I D = 2 × 240 × 20 × 150 = 1.2 mA/V ro = V A′ L 15 V/µm × 0.5 µm = = 50 kΩ 150 µA ID B) From equation 6.146: v gs vi = v gs vi = RL || Rout 1 1 + ( g m + g mb ) Rs RL || ro 20 k || Rout 1 1 + (1.2 + 0.2 × 1.2) Rs 20 k || 50 k (1) Rout = ro [1 + ( g m + g mb ) Rs ] = 50 × (1 + 1.2 × 1.2 × Rs ) = 50 + 72 × 1.945 = 190 kΩ → v gs vi = 0.3333 = 1 3 C) Rout = 50 + 72 Rs = 190 kΩ Rin = ∞ Avo = − g m ro = 1.2 mA/V × 50 kΩ = 60 V/V Av = Avo Gm = RL 20 = 60 × = 5.7143 V/V 20 + 190 RL + Rout gm 1.2 = = 0.3157 mA/V 1 + ( g m + g mb ) Rs 1 + 1.2 × 1.2 × 1.945 D) RL′ = Rout || RL = 20 || 190 = 18.095 kΩ R gd = Rsig (1 + Gm R L′ ) = 20 × (1 + 0.3157 × 18.095) = 134.252 kΩ R gs = Rsig + Rs ro 1 + ( g m + g mb ) Rs ro + RL = 20 + 1.945 50 1 + 1.2 × 1.2 × 1.945 × 50 + 20 = 7.3136 kΩ τ H = C gs R gs + C L RL′ + C gd R gd = 1 p × 7.3136 k + 2 p × 18.095 k + 0.2 p × 134.252 k fH = 7.3136 + 36.19 + 26.8504 = 70.354 ns 1 = = 2.2622 MHz 2πτ H f t = Av f H = 5.7143 × 2.2622 = 12.927 MHz E) Rs increases Rin, and Rout, decreases Gm, Avo, and improves the frequency response. 8% 2. A) Describe the characteristics of the emitter follower with respect to the input resistance, the output resistance, the voltage gain, and the frequency response. (4%) B) Describe the characteristics of the CC-CE amplifier with respect to the input resistance, the output resistance, the voltage gain, and the frequency response. (4%) Ans: A) emitter follower: high input resistance, low output resistance, roughly unity gain, and excellent frequency response. B) Rin ↑, Rout↓, AM ↑, fH ↑ 29% 3. For the PMOS differential amplifier shown in Fig. 4, let Vtp = −0.7 V and k ′p W/L = 4.5 mA/V2. Neglect 0.9 mA channel-length modulation. A) For vG1 = vG2 = 0V, find VOV and VGS for each of Q1 and Q2. Also find vS, vD1 and vD2. (7%) B) If the current source requires a minimum voltage of 0.32 V, find the input common-mode range. (4%) C) If the current source having an output resistance RSS = 20 kΩ. If the output is taken single-endedly, find |Ad|, |Acm|, and CMRR. (3% each) D) Following C), if the output is taken differentially and there is a 1% mismatch between the drain resistances, find |Ad|, |Acm|, and CMRR. (3% each) 1.5 kΩ 1.5 kΩ Fig. 4 PMOS differential amplifier. Ans: A) i D = 1 W 2 2 k ′p VOV → 0.45 = 0.5 × 4.5 × VOV → VOV = 0.4472 V 2 L vGS = Vtp – VOV = −0.7 – 0.4472 = −1.1472 V vS = −vGS = 1.1472 V vD1 = vD2 = −2.5 + 0.45 x 1.5 = −1.825 V B) vCMmin = −2.5 + 0.45 x 1.5 – 0.7 = −2.525 V vCMmax = 2.5 – 0.32 – 1.1472 = 1.0328 V C) g m = Ad = ACM 0.45 = 2.0125 mA/V 0.4472 / 2 1 g m RD = 1.51 V/V 2 R 1.5 = D = = 0.0375 V/V 2 RSS 40 CMRR = Ad ACM = 1.51 = 40.25 (≅ 32.1 dB) 0.0375 D) Ad = g m RD = 3.02 V/V ACM = RD ∆RD 1.5 = × 0.01 = 0.375 mV/V 2 RSS RD 40 CMRR = Ad ACM = 3.02 = 8053.4 (≅ 78.1 dB) 0.375 × 10 −3 +VDD 28% 4. Consider the circuit in Fig. 4 with the following devices geometries (in µm). Q2 Q3 Q4 Q1 Q8 W/L 32/0.25 32/0.25 12.8/0.25 12.8/0.25 Q5 Q6 Q7 Q8 W/L 64/0.25 W6/0.25 64/0.25 64/0.25 Let IREF = 200 µA, Vtn = 0.45 V, Vtp = −0.6 V, µnCox = 250 µA/V2, IREF µpCox = 100 µA/V2, |VA| (for all devices) = 3V, VDD = VSS = 1.3V. a) Find W6 such that the amplifier won’t have a systematic offset voltage. (2%) b) Find ID, |VOV|, |VGS|, gm, and ro for all devices. (16%) c) Find A1, A2, and the open-loop gain. (6%) Q5 Q7 I Q1 Q2 D2 Q3 vo CC D6 Q4 −VSS Fig. 4 Two-stage CMOS op-amplifier. Q6 d) Find the input common mode range, and the output voltage range. (4%) Neglect the effect of VA on the bias current. Ans: 2(W / L) 7 (W / L) 6 a) = ⇒ W6 = 25.6 µm (W / L) 5 (W / L) 4 b) Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 100 100 100 200 200 200 200 ID (µA) 100 |VOV| (V) 0.125 0.125 0.125 0.125 0.125 0.125 0.125 0.125 |VGS| (V) 0.725 0.725 0.575 0.575 0.725 0.575 0.725 0.725 gm ( mA ) 1.6 V 1.6 1.6 1.6 3.2 3.2 3.2 3.2 30 30 30 15 15 15 15 ro (kΩ) 30 c) A1 = −Gm1R1 = −gm1(ro2||ro4) = −1.6(15) = −24 V/V A2 = −Gm2R2 = −gm6(ro6||ro7) = −3.2(7.5) = −24 V/V open-loop gain = A1 A2 = 576 V/V = 55.21 dB d) input common mode range: VCM, max: Q5 leaves saturation, = VDD – |VOV5| – |VGS1,2| = 1.3 – 0.125 – 0.725 = 0.45 V VCM, min: Q1 Q2 leaves saturation, = −VSS + |VGS3| – |Vtp1,2| = −1.3 + 0.575 – 0.6 = −1.325 V output voltage range: Q6 or Q7 leaves saturation: Vo, max: VDD – |VOV7| = 1.3 – 0.125 = 1.175 V Vo, min: −VSS + |VOV6| = −1.3 + 0.125 = −1.175 V 9% 5. a) Plot a CMOS implementation of a clocked SR flip-flop. Also give its truth table. (4%) b) Plot a master-slave D flip-flop circuit, and explain how it works, also plot the required clock waveforms. (5%) a) b) φ1 phase: Master input data without locking, Slave locking on previous data value, φ2 phase: Master locking on data value at φ2 rising edge, and Slave is open loop to feed output at nonoverlap time gap, hold data by charge on the parasitic capacitance.