Diode Transistors & Current Mirrors Analysis

advertisement

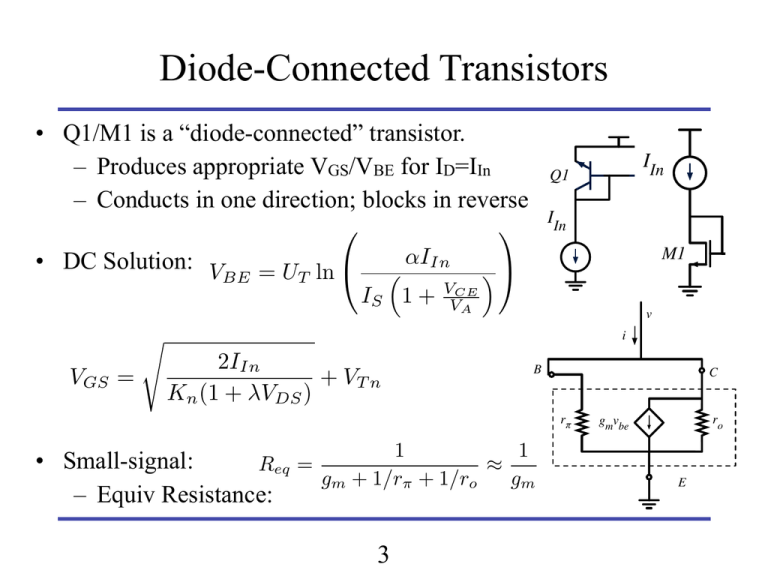

Diode-Connected Transistors

• Q1/M1 is a “diode-connected” transistor.

– Produces appropriate VGS/VBE for ID=IIn

– Conducts in one direction; blocks in reverse

⇤

IOut

M1

VOut

v

i

B

C

rπ

1

1

• Small-signal:

Req =

⇡

gm + 1/r⇡ + 1/ro

gm

– Equiv Resistance:

3

Q2

IIn

⌅

IIn

• DC Solution:

V = U ln ⇧

⇥⌃

BE

T

IS 1 + VVCE

A

2IIn

VGS =

+ VT n

K

(1

+

V

)

n

DS

IIn

Q1

ro

gmvbe

E

Current Mirrors

• M1 is a “diode-connected” transistor.

– Produces appropriate VGS for ID=IIn

IIn

– Active mode guaranteed for enhancement

device

M1

• Applies same VGS to M2

• IOut = ID2 = IIn = ID1

– Assuming M1 and M2 identical and in

active mode

Q1

– Neglecting channel-length modulation

IIn

– w/ BJT mirror, IIn ≠ IC1

• IOut =?

4

IOut

M2

Q2

IOut

VOut

Current Mirrors - Applications

• Copy/distribute a bias or signal current

• Change direction of a current - convert

between current source and sink

• Isolate current source from load impedance

– (RIn ~ 1/gm) << (ROut ~ ro)

IIn

IOut

M2

M1

Q1

Q2

IOut

IIn

VOut

5

MOS Current Mirrors: DC Analysis

1+ λV

(

DS2 ) ≅ I

∴I = I

REF

O REF

1+

λ

V

( DS1)

MOSFETs M1 and M2 are

assumed to have identical VTN,

Kn’, λ, and W/L ratios.

However, VDS1 is not equal to VDS2 and

there is slight mismatch between

output and reference currents. Mirror

ratio is:

€

IREF provides operating bias to

mirror.

1+ λV

(

DS2 )

MR = O =

I

REF (1+ λVDS1)

I

VDS1 = VGS1= VGS2 =VGS

6€

MOS Current Mirror (Example)

Problem:Calculate output current for given current mirror.

Given data: IREF = 150 µA, VSS = 10 V, VTN = 1 V, Kn = 250 µA/V2, λ =

0.0133 V-1

Analysis: (1+ λ VDS1) term is neglected to simplify dc bias calculation.

V

=V

=V +

DS1 GS1 TN

2I

REF =1V + 2(150µA) = 2.10V

Kn

µA

250

V2

#

&

0.0133

%1+

(10V)((

%

$

'

V

∴I = (150µA) #

=165µA

&

O

0.0133

%1+

(2.10V)((

%

$

'

V

€

€

Actual currents are found to be mismatched by

approximately 10%.

7

MOS Current Mirrors: Changing Mirror

Ratio

1+ λV

(

DS2 )

∴I = I

O REF

K (1+ λV

n1

DS1)

W

1+ λV

(

DS2 )

L

2

=I

REF W

1+ λV

(

DS1)

L 1

W

1+ λV

(

DS2 )

L

2

MR =

W

1+ λV

(

DS1)

L 1

K

Mirror ratio can be changed by

modifying W/L ratios of the two

transistors forming the mirror.

- Or w/ multiple FETs in parallel

$

&

&

%

$

&

&

%

"

$

$

#

"

$

$

#

€

'

)

)

(

'

)

)

(

%

'

'

&

%

'

'

&

n2

In given current mirror, Io =5IREF. Again

mismatch in VDS causes error in MR.

€

8

Bipolar Current Mirrors: DC Analysis

BJTs Q1 and Q2 are assumed to

have identical IS, VA, βFO, and

W/L ratios.

Io = IC2,

IB2

IREF = IC1 + IB1 +

VBE1= VBE2 =VBE

!I

O

=I

"

$1+(V

#

CE2

%

/V )'

A &

REF "$ V

2

$1+ CE1 +

$$

V A ! FO

#

%

'

'

''

&

Even w/ equal VC1, VC2, finite β causes

slight mismatch between Io and IREF.

9

Bipolar Current Mirrors: Changing Mirror

Ratio

Emitter area scaling changes the

transport equations using which,

(1+(VCE2 /VA ))

I = nI

REF # V

O

1+n &

CE2

%1+ V + β (

$

A

FO '

Ideally, MR= n, but for finite beta,

€

Mirror ratio can be changed by

modifying the emitter area of the

transistor.

10

Multiple Current Sources

•

•

•

•

11

Reference current enters diode-connected

transistor M1 establishing gate-source

voltage to bias M2 through M5, each with

different W/L ratio.

Absence of current gain defect permits

large number of MOSFETs to be driven by

one reference transistor.

Similar multiple bipolar sources can be

built from one reference BJT.

As base current error term worsens when

more BJTs are added, number of outputs of

basic bipolar mirror are limited.

Buffered Bipolar Current Mirror

Assuming infinite Early voltage for simplicity,

Large mirror ratio leads to large

current gain defect

Q3 provides base currents, reduces

error

Thus error term in denominator is

reduced.

12

Output Resistance of Current Mirrors

This simplifies the ac model of

the current mirror. Similar

analysis applies to MOSFET

current mirror except that the

current gain is infinite. Thus

For diode connected BJT, from smallsignal model,

...If βoand µF >>1

13

or

Current Mirror with Resistor

Degeneration

• How to size resistors for

scaled mirrors?

• Degenerate both sides to

maintain equal VGS

• Resistor scales inversely

with transistor W/L

– Equal voltage drop

across RS

IIn

IOut

1 W

k L

kRS

14

W

L

RS

Reference Current Generation

•

•

Reference current is required by all current mirrors.

When resistor is used, source’s output current is directly

proportional to VEE.

•

Gate-source voltages of MOSFETs can be large and several

MOS devices can be connected in series between supplies to

eliminate large resistors.

VDD + VSS = VSG4+ VGS3 + VGS1 and ID3 = ID1 = I4

•

Change in supply directly alters gate-source voltage of

MOSFETs and the reference current.

BJTs can’t similarly be connected in series due to small fixed

voltage developed across each diode and exponential

relationship between voltage and current.

•

15

Current Mirror Biasing Example

• NMOS Mirror KN = 250uA/V2, Vtn = 0.6.

ID = 25uA. VDD = 10V

– Ignore ro for bias calculation

RBias

16

IOut

Current Mirror Biasing Example

• NMOS Mirror KN = 250uA/V2, Vtn = 0.6.

ID = 25uA, VDD = 10V

– Ignore ro for bias calculation

• VGS = VTn + sqrt(2ID/Kn) = VDD - IDRB

= 1.04 V

• IDRB = 8.95. RB = 358k

17

RBias

IOut

Differential Amplifier

• Differential pair provides

two output currents

• Often want single-ended

output - need to combine the

two currents into one.

• Opposite polarities - can’t

simply wire together.

18

iod/2

-iod/2

Differential Amplifier with Active Load Quick Look

• Current mirror reverses polarity of one output current so

the two can be combined

• Current-mirror load increases output resistance and gain

• Converts differential output current to single-ended

Adm = isc Rth = gm2 (ro2 ||ro4 ) ⇡ µf 2 /2

Ro = ro2 ||ro4

Acm

⇣

ro3

ro2

⌘

1+

isc Rth

=

=

(ro2 ||ro4 )

vic

2µf 3 Rss

✓

◆

(ro2 + ro3 )

ro4

1

=

=

2gm3 ro3 Rss ro2 + ro4

2gm3 Rss

19

If ro4 = ro3

CMOS Differential Amplifier with

Active Load: DC Analysis

ID3 = ID1 = ID2 =ID4 =ISS/2.

Mirror ratio is set by M3 and M4 and is exactly

unity when VSD4 = VSD3 and thus VSD1 = VSD2.

Differential amplifier is completely balanced at

dc when:

20

CMOS Differential Amplifier with Active Load:

Differential-Mode Signal Analysis

The differential amplifier can be

represented by its Norton equivalent.

Total short circuit output current:

Differential-mode voltage gain:

Thevenin equivalent output resistance:

21

High output resistance, well-modeled as

transconductor (VCCS). “Operational

Transconductance Amplifier” (OTA)

CMOS Differential Amplifier with

Active Load: Output Resistance

Drain current of M2 (vx/2ro2)is replicated by

current mirror as drain current of M4. Total

current from source is 2(vx/2ro2)= vx/ro2.

Total current is:

Output resistance

Assume RSS >>1/ gm1.

is:

Resistance looking into drain of

✓ M2 (in isolation)

◆ is:

1

Ro2 = ro2 (1 + gm2 RS ) = ro2 1 + gm2

= 2ro2

gm1

But current mirror doubles id2

22

CMOS Differential Amplifier with Active

Load: Common-Mode Signal Analysis

From small-signal equivalent of differential pair:

Roc = ro2 (1 + gm2 2RSS )

#

%

%

%

%

$

2µf 2 RSS

&

r (

1+ o3 (( #

#

&

r ( % v &(

g

o2 ' % ic (

isc = −%%ioc + g v − o2 v (( ≅ −

%

(

%

m4 3 2 3 ('

µ

% 2R

(

$

f 3 $ SS '

where it is assumed that gm4 = gm3 and Goc << gm3.

€

Acm

⇣

ro3

ro2

⌘

1+

isc Rth

=

=

(ro2 ||ro4 )

vic

2µf 3 Rss

✓

◆

(ro2 + ro3 )

ro4

1

=

=

2gm3 ro3 Rss ro2 + ro4

2gm3 Rss

If ro4 = ro3

23