Manual

advertisement

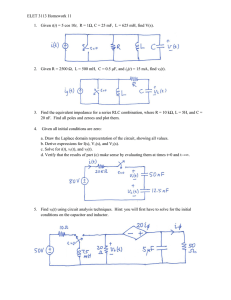

Experiment No. 10: Study of ZVS and ZCS in auxiliary switch active clamp buck converter Objective: The experiment demonstrates a method to implement ZVS (Zero Voltage Switching) on the main switch of the Buck Converter by using an auxiliary switch that itself operates under ZCS (zero Current Switching). Introduction: The PWM dc-dc converters are available in three basic topologies - buck, boost and buck-boost. The active clamp topologies are introduced to implement loss-less switching in the basic converters while retaining the variable duty ratio-constant frequency control intact. It has one auxiliary switch that initiates resonance to implement ZVS/ZCS operation of the main switch under clamped voltage/current condition. The auxiliary switch itself remains loss-free, undergoing either ZCS/ZVS transition during its switching. In this paper a new class of active clamp PWM dc-dc converters is proposed. ZVS-ZCS: In conventional hard switching the power devices experience switching loss. This is due to the reason that during turn-on (from OFF state to ON state) or turn-off (from ON state to OFF state) transients voltage and current appear simultaneously on the device as shown in Fig. 1(a) and 1.(b). In ZVS with the aid of an external circuit in combination with the switching strategy it is ensured that the voltage across the device in the OFF state falls to zero and subsequently it is turned-on. As a result only the current through the device would change during a turn-on transient and ideally the switching loss would be zero. Similarly in ZCS with the aid of an external circuit in combination with the switching strategy it is ensured that the current through the device in the ON state falls to zero and subsequently it is turned-off. As a result only the voltage across the device would change during a turn-off transient and ideally the switching loss would be zero. These ZVS and ZCS are shown in Fig. 2(a) and (b). DESCRIPTION OF PROPOSED CIRCUIT: The process of loss-less switching has been described for the specific example of a PWM buck converter that uses the proposed active clamp circuit as shown in Fig. 3. The circuit waveforms are shown in Fig. 4. The auxiliary switch Q a is turned-on with the initial condition that the main switch Q a is off. The proposed circuit configuration uses a series capacitor that in combination with the auxiliary inductor develops resonance in the clamp circuit. The inductor current first discharges the capacitor across the main switch and as a result the subsequent turn-on of it satisfies ZVS. The inductor current would then reverse and go through zero and thereby ZCS of the auxiliary switch is achieved. It may be observed that the proposed circuit configuration has two diodes that are not directly related to ZVS/ZCS operation. One of these is required to maintain the continuity of the inductor current in the opposite direction during resonance and another for the discharge of the resonant capacitor. The capacitor is charged during the resonant cycle from zero to some negative value and it is discharged by the load current/ the inductor current of the buck converter just after the main switch is turned-off. The proposed topology also includes another diode, that though is not a basic requirement of the topology but improves the operation nevertheless, as it clamps the voltage across the auxiliary switch by providing continuity to the resonant inductor current. In the inductor this current is developed due to the reverse recovery current of the diode that conducts during the negative cycle of the inductor current. CIRCUIT ANALYSIS: Qa Q D2a Ca1 Buck Converter D1a Vg La L Ca2 Dc1 Active Clamp Dc2 D Vo C R Fig. 3 : Proposed active clamp buck converter In the following analysis all the switching devices and the passive components are considered to be ideal. Mode 0: The equivalent circuit is shown in Fig.5. Both Qand Q a are in off state. i D = I L (1) Mode 1: The equivalent circuit is shown in Fig.6. The auxiliary SWITCH Q a is turned-on at t = 0. At t = T 1 the current through the auxiliary inductor i La becomes equal to the load current I L and the diode D stops conduction. C i La (t) = V g La2a sin * 1 t (2) v Ca2 (t) = V g (1 − cos * 1 t) Qa ON t Q ON ON t IL i Dc2 i La t T1 T3 T4 v c1 t T2 v c2 t Fig.4 Key waveforms of the proposed active clamp buck converter v Ca1 (t) = V g * 1 = L 1C a a2 I sin −1 ( VLg a T1 = C a2 ) Mode 2: The equivalent circuit is shown in Fig.7. The diode D is off and the current through the capacitor C a1 is equal to i La − I L . This mode ends at t = T 2 when V Ca1 (T 2 ) = 0. This can be solved from 1 *1 i La (t) = V g L C a1 ||C a2 La cos(* 1 T 1 ) sin * 2 t + I L cos * 2 t * 2 = L (C 1 ||C ) a a2 a1 Since C a1 << C a2 the above equation can be approximated as i La (t) = V g C a1 La cos(* 1 T 1 ) sin * 2 t + I L cos * 2 t * 2 = L 1C a a1 v Ca1 (t) = V g (1 − cos * 1 T 1 ) + V g cos(* 1 T 1 ) cos * 2 t − I L La C a1 sin * 2 t v Ca2 (t) = V g [1 − cos(* 1 T 1 )] = v Ca2 (T 1 ) Mode 3, Mode 4 and Mode 5: In Mode 3 the body diode of the main switch Q conducts. Subsequently Q is turned-on under ZVS and the circuit enters into Mode 4. Mode 4 ends when at t = T 3 , i La = 0. Under that condition the auxiliary switch turns-off under ZCS along with the diode D a1 . In Mode 5 the current in the inductor is negative and it flows through the diode D a2 . The equivalent circuit is shown in Fig.8. This mode ends when at t = T 4 , i La again reaches 0. The differential equations governing i La and v Ca2 are the same in all these modes. Qa off v ca1 D2a Q off Ca1 Qa D1a Vg Dc1 i La vca2 D ID Dc2 Ca1 Vg Ila R Vca2 Dc2 Fig. 5 : Mode 0 equivalent circuit L Ca2 La Dc1 IL C mode 1 D1a mode 0 initial state L Ca2 La Vca1 Q off D2a Turned-on D ID IL C R Fig.6 : Mode 1 equivalent circuit i La (t) = −v Ca2 (T 1 ) C a2 La sin * 1 t + I La (T 2 ) cos * 1 t C v C2 (t) = I L La2a sin * 1 t + v Ca2 (T 1 ) cos * 1 t Mode 6: This mode is the on state of the buck converter. The switch Q is on and it carries the load current I L . Mode 7: The equivalent circuit is shown in Fig.9. This mode starts when Q is turned-off and D c2 begins to conduct. The load current I L is shared between C a1 and C a2 and the turn-off of Q is ZVS. At the end of this mode v Ca2 (T 5 ) = 0 and the buck converter diode D begins to conduct and the circuit returns back to Mode 0. C a2 v C2 (t) = V C2 (T 4 ) − I L C a1 +C t a2 Qa ZCS Turn-off Vca1 D2a Ca1 mode 2 D1a Ca1 mode 5 D1a Vg Ca2 La Dc1 Vca1 D2a L Ila Dc2 Vg IL C Vca2 Dc1 Ila R IL C Vca2 Dc2 Fig.7 Mode 2 equivalent circuit L Ca2 La R Fig. 8 Mode 5 equivalent circuit Mode 5(i) and Mode 5(ii): These are two intermediate modes between Mode 5 and Vca1 Q ZVS Turn off Mode 6 in a practical power converter and D2a mode 7 Ca1 At the end of this mode should not exist if we assume that all the the initial state is reached D1a diodes used in this topology are ideal. In Vg L Ca2 La Mode 5(i), shown in Fig. 10(a), the Dc1 (actual) IL reverse recovery current of D 2a flows C Vca2 R i Dc2 Dc2 through L a . In Mode 5(ii) D c2 conducts as it provides a path for the inductor Fig. 9 : Mode 7 equivalent circuit current developed during the reverse recovery of the diode D 2a . The equivalent circuit is shown in Fig.10(b). As a result the voltage across Q a gets clamped to the D2a Vca1 D1a mode 5(i) Vg La L Dc1 Dc1 Vca1 Ca1 Ca1 reverse D1a recovery current La Ca2 Vg Voltage Vg clamp Ila Vca2 IL C Ca2 Ila Vca2 R mode 5(ii) L IL C Dc2 Dc2 Fig. 10(a) : Mode 5(i) equivalent circuit Fig. 10(b) : Mode 5(ii) equivalent circuit mode 5 R PWM time Ta time S for M1 Tb time R for M1 time Gate pulse for M1 time S for M2 time R for M2 time Gate pulse for M2 time Ta decides ZCS of M1 Tb decides ZVS of M2 5 4 3 2 Vcc U1 Vcc 100k R5 R4 D 4_inv 5.1k C1 10u C2 0.1u 5.1k D1 1k 1k 0 0 9_noninv 8_inv U3 1_Q Vcc 0 5_noninv PWM 5.1k R14 20M R13 Vcc R10 14_out 2_out 100k 14 13 12 11 10 9 8 1 2 3 4 5 6 7 Vcc 2_Q C6 10u C7 0.1u R7 1k R9 2_out 1k 1k 0 CLK R11 Vcc 0 R16 Vcc 6_inv C9 10u R12 JUMPER1 C11 1n 0 R22 R23 7_noninv Vsense 10k 5.1k a1 a2 b1 b2 3 4 G1 S1 T1 R18 1k R19 R20 R24 C14 10u Vcc 1_out 100k 2_Q R27 1k J2 8 7 6 5 0 C16 1n 0 2 1 1 2 a1 a2 b1 b2 3 4 G2 S2 Vcc CON2 T2 UCC27322 0 R28 A 1n 0 1 2 3 4 1_Q B C13 1k +EA U5 100k R21 1k C15 0.1u R25 9_noninv -EA 1k 10M R26 C12 1n 0 1_out PWM JUMPER1 1 2 0 B 0 C C10 0.1u UCC27322 Vcc BR1 BR2 8 7 6 5 1 2 3 4 1k 1k 1n Vo 1k R17 0 0 U4 2_Q 0 C8 UC3526 0 Vcc C5 0.1u 1k CLK C 0 C4 10u R8 0 CD4013BC R15 10k 1k 18 17 16 15 14 13 12 11 10 1 2 3 4 5 6 7 8 9 1n-EA +EA Vcc D R6 U2 C3 LM339 0 1N4148 R1 14_out 14 13 12 11 10 9 8 1 2 3 4_inv 5_noninv 4 5 6_inv 7_noninv 6 7 R3 Isense R2 1_out 2_out Vcc 1 Vcc 8_inv A 0 R29 56k Title <Title> 1k Size A 0 Date: 5 4 3 Document Number <Doc> Sunday, April 25, 2010 2 Rev <RevCode Sheet 1 of 1 2 5 4 3 2 1 J1 2 1 D G1 10 D2 MUR805 IRF640 R31 M2 C17 10 G2 D CON2 24V R30 M1 24V 1n 1n C24 C25 J3 2 1 Vo 4.7n IRF640 CON2 S1 S2 Vsense MUR805 D3 Vo L1 R32 C D4 10uH Isense 10K C D1N4148 T3 R33 C18 R34 100Ohm 1k 3 4 b1 b2 a1 a2 L2 1 2 C19 10uH 100pf 68n C20 C21 C22 C23 R35 1n 1n 1n 1n 1k D5 D6 MUR805 MUR805 R36 0 1k 0 B B A A Title <Title> Size A Date: 5 4 3 Document Number <Doc> Rev <RevCode> Sunday, April 25, 2010 Sheet 2 2 of 2 1 maximum value of V g . From Mode 5(ii) it would return to Mode 5 during the gradual decaying of the reverse recovery current and eventually the circuit moves to Mode 6. The active clamp boost and buck-boost converters are shown in Fig. 10 and Fig. 11 respectively. EXPERIMENTAL PROCEDURE: (1) Design a circuit in the breadboard to generate PWM pulses at a switching frequency of 82 KHz using UCC3526. (2) Use two monostable multivibrators (decide time durations and choose R-C components accordingly) and S-R F/Fs to generate gating signals for main switch Q and auxiliary switch Q a that would be required for ZVS and ZCS respectively. Refer to Fig. 12 for circuit diagram and Fig. 13 for timing diagram. (3) Identify the components of the main and the auxiliary converter circuits in the PCB. (4) Apply the gating signals to the inputs of the driver ICs. (5) Operate the power circuit at the following operating condition: buck converter : L = 25H; C = 100F; R = 2; F S = 82 kHz; D = 0.45; V g = 10V ;Q: IRF640 D: MUR 405. (2) active clamp L a = 0.95H; C a1 = 4nF; C a2 = 68nF; D 1a , D 2a , D c1 and D c2 : MUR 405; Q a : IRF640. (6) Record the waveforms Q , Q a , i La , v c1 and v c2 REPORT : (a) Develop the circuit topology of an auxiliary switch boost converter and analyze its different modes of operation for ZVS of the main switch and ZCS of the auxiliary switch.