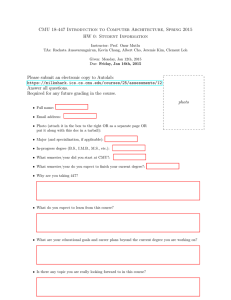

2004 Specifications

advertisement