Slew rate and settling, Common Mode Feedback

advertisement

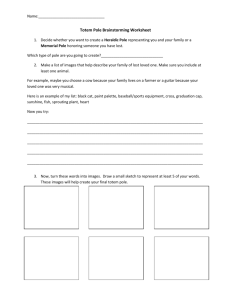

E3 238 Analog VLSI Circuits Lecture 23: More Compensation, Slew rate, CMFB Gaurab Banerjee Department of Electrical Communication Engineering, Indian Institute of Science, Bangalore banerjee@ece.iisc.ernet.in Miller Compensation and Pole Splitting -> Small signal model with two high impedance nodes -> KCL at node 1: => (1) Miller Compensation and Pole Splitting -> KCL at node 2: (2) -> Substitute (2) into (1): Miller Compensation and Pole Splitting RHP zero Low frequency gain -> Consider: -> Use dominant pole approximation: => Miller Compensation and Pole Splitting Miller Compensation and Pole Splitting Pole splitting Start with this number and refine the design RC Pole Splitting Compensation -> One possible solution: Add series resistor RF to CC to modify the location of the zero RC Pole Splitting Compensation Analysis leads to: Impact of CL 1- stage: Dominant pole moves closer to origin -> better phase margin 2- stage: Second pole moves closer to origin -> worse phase margin Slew Rate Consider an op-amp in unity gain feedback. In linear operation, assuming a single pole transfer function: Let us provide a 5V step as input: Slew Rate -> Output response for large input step is slower, and follows a linear ramp. -> In the region of constant slope, the op-amp is slew-rate limited. Slew Rate: 2-stage Op-Amp -> 2nd Stage acts as an integrator -> First stage current (Ix) charges the compensation capacitor -> Maximum current available, under large input step = I0 Circuit acts nonlinearly: Slew rate ≈ 1V/us for commercial, general purpose operational amplifiers Slew Rate Improvement For a large input voltage: For small signal operation: Slew Rate Improvement Assume that compensation results in unity gain at the second pole (45o phase margin). So -> High ω2 => Large slew rate -> For a given ω2 , maximize or minimize -> Large gate overdrive translates to a better slew rate! Ideal and actual switched capacitor output due to slewing and linear settling. Common Mode Feedback -> Fully differential amplifier with two current sources -> What is the common mode level at X and Y? -> Ideally, ID3 , ID4 = ISS/2 -> In reality, due to mismatches in the PMOS and NMOS current mirrors, ID3 , ID4 ≠ ISS/2 -> If ID3 , ID4 > ISS/2, M3/M4 will enter triode (higher value of X/Y) so that their drain currents fall to ISS/2 -> If ID3 , ID4 < ISS/2 Vx, Vy drop, driving the tail current source into triode, and reducing its current to IDS,M3,M4 -> Mismatch related current (IP – IN) flows into RP ║ RN (very high) -> Leads to large voltage error leading P or N type current source into triode. Common Mode Feedback -> Resistive loading of outputs takes place if resistors are used. -> Eliminate resistive loading by inserting buffers (source followers): impacts differential output swings -> Switched capacitors can also be used in performing CMFB. -> Key point: Analyze CMFB loop for stability under feedback using techniques discussed earlier Fully Differential Op-Amp with CMFB Mirrored current to adjust CMFB Input diff-pair with active load Current = DC term + k (Voc-VCM) 2nd stage with Miller Compensation