GHz SAM APPLICATIONS

advertisement

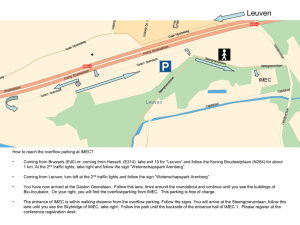

METROLOGY AND FAILURE ANALYSIS CHALLENGES IN SI PROCESSING: GHz SAM APPLICATIONS INGRID DE WOLF AND AHMAD KHALED OUTLINE Introduction microelectronics Imec- PVA TePla collaboration Back-end of line Micro bumps TSV voids & co Conclusions 2 © IMEC 2014 OUTLINE Introduction microelectronics Imec- PVA TePla collaboration Back-end of line Micro bumps TSV voids & co Conclusions 3 © IMEC 2014 MICROELECTRONICS BEOL (Back-End-Of-Line): metal lines – isolation - vias From Global Foundries Purpose BEOL: Electrically connect the devices from the FEOL (front-end-of-line). Pre (or Poly)-metal dielectric (PMD) Silicon FEOL (Front-End-Of-Line): transistors, resistors, capacitors,... (active devices) 4 © IMEC 2014 MICROELECTRONICS: 3D • Heterogeneous integration Build one system with different functions/technologies (memory, sensors, batteries, etc.) Battery MEMS DNA Chip • The on-chip interconnect length decreases (BEOL becomes simpler) Image Sensor RF Chip Processor • Better performance Memory • Sleek form factor - 1mm3 instead of 50mm2 silicon !!! Beyne et al., Swinnen et al. 5 © IMEC 2014 MICROELECTRONICS: 3D "Via-middle": fabrication of TSV’s after FEOL device processing but before BEOL interconnect. imec POR process: Si Si 50 μm 5μm o 5 µm diameter; o 50 µm deep; o Aspect ratio 10 (currently working on 3 µm diameter and via last) 6 INGRID DE WOLF © IMEC 2014 OUTLINE Introduction microelectronics Imec- PVA TePla collaboration Back-end of line Micro bumps TSV voids & co Conclusions 7 © IMEC 2014 IMEC-PVA TEPLA COLLABORATION Basic applications Exploratory 3D integration 200MHz-1GHz SAM LEDs, MEMS, Solar... Focus on 3D and BEOL 8 © IMEC 2014 PVA TEPLA SAM SYSTEMS @ IMEC Autowafer 300 SAM 300 GHz SAM: installed in June 2014 9 © IMEC 2014 AUTOWAFER 200 In-line wafer to wafer bonding inspection: 200/300mm Full thickness bonded wafers 25um/200mm wafers on carrier 50um/300mm wafers on carrier Process availability 10 © IMEC 2014 SAM 300 Conventional stack/package level studies ▸ Delamination ▸ Voids in underfill ▸ etc 11 © IMEC 2014 GHz SAM 3D/BEOL applications ▸ ▸ ▸ ▸ Crack detection in BEOL Void detection in TSV Delamination of micro-bumps Failure analysis - Delamination - Cracks - Stress Other... 12 © IMEC 2014 OUTLINE Introduction microelectronics Imec- PVA TePla collaboration Back-end of line Micro bumps TSV voids & co Conclusions 13 © IMEC 2014 BACK-END OF LINE (BEOL) Sub-32 nm technology requires ultralowk dielectric materials (k<2.5) in the BEOL to reduce the RC delay The k-value decreases with increasing 2.7 porosity. 2.6 Solution: Silicon 2.4 k-value Porous low-k Materials 2.5 2.3 2.2 2.1 2.0 1.9 1.8 20 25 30 35 40 45 50 Open porosity (%) 14 © IMEC 2014 BACK-END OF LINE (BEOL) BUT: The mechanical properties of porous ultralow-k become worse with increasing porosity. ▸ The E-modulus decreases ▸ The energy required for cohesive fracture decreases 1 2 Vanstreels, imec 15 © IMEC 2014 BACK-END OF LINE (BEOL) Result: Very fragile BEOL that easily cracks X. F. Zhang, et al. Advanced Metallization Conference, 2008. Any additional mechanical stress can cause problems in the BEOL: Packaging, bumping, Cu-pillars.... induce stress 16 © IMEC 2014 BACK-END OF LINE (BEOL) ▸ Packaging causes additional stresses because of curing & thermal shrinkage of polymer based materials (overmould, underfill) ▸ Package level interconnections (mbumps, Cu pillars, TSVs,...) cause local stresses How to study this? Cu-pillar PTCQ Laminate INGRID DE WOLF 17 © IMEC 2014 BEOL strength test: 4-pt bending Critical energy release rate Gc 21 (1 substrate 2 ) P 2 L2 Gc 16 Esubstrate B 2 H 3 Adhesion tests on uniform filma BEOL strength tests silicon Chip Low-k BEOL Interface material: Cu, SiCN, TaNTa Output: • Adhesion strengths between uniform layers M1 VIA M2 VIA Epoxy-glue M3 VIA M4 VIA silicon Output: • Weakest interface • Stress level at which BEOL cracks M5 VIA M6 VIA M7 Passivation Q: Where is the crack/delamination running and stopping? 18 KRIS VANSTREELS © IMEC 2014 SAMPLE WITH ‘CRACK STOPPER’ Crack stopper: metals in BEOL designed to stop a crack notch crack stopper crack stopper Test: 4-point bending Question: Is the crack stopper stopping the crack? 19 © IMEC 2014 SAMPLE WITH ‘CRACK STOPPER’ ▸ IR scanning laser microscope: good resolution difficult to see delamination ▸ SAM (175 MHz) experiment done at PVA TePla delamination easy to detect Resolution: need GHz SAM Crack stopper stops crack Opened area after crack propagation 20 © IMEC 2014 FUTURE CHALLENGES ▸ Can we detect at which BEOL interface the crack runs? ▸ Can we measure cracks in BEOL below (50mm/F=50mm) Cu-pillars? 2 mm Use BABSI to make cracks PTCQ Laminate Cu-pillar Failures in BEOL delamination Cu-pillar BEOL 21 © IMEC 2014 BABSI on Cu pillar on BEOL Indenter tip FN Dx FLateral Crack initiation 10µm or SEM (before BABSI): Cu pillar F=50µm D=50µm zmax LEXT IR (After BABSI): BEOL Silicon substrate Make crack but stop before Cu pillar is removed: where is crack? 22 KRIS VANSTREELS – MAM 2014 © IMEC 2014 7 FIRST TESTS WITH GHz SAM Partly sheared Cu-pillar (BABSI test) GHz SAM: look through Cu pillar from top (50 mm high): touch Cu? Cu pillar F=50µm D=50µm Si below is 50 mm thick: look from backside Metals from BEOL visible: 23 © IMEC 2014 FIRST TESTS WITH GHz SAM GHz SAM through back of thinned Si: promising results but difficult to find sheared bump back Further work to be done Zoom-in 24 © IMEC 2014 OUTLINE Introduction microelectronics Imec- PVA TePla collaboration Back-end of line Micro bumps TSV voids & co Conclusions 25 © IMEC 2014 3D STACKING CHALLENGES FOR SAM µbump scaling: both width and height (20 µm 10 µm and lower) Which bumps fails and where? - Delamination of top or bottom? Which chip Detection of small voids 5µm 20µm 26 © IMEC 2014 GHZ SAM ON X-SECTION BUMPS micro-bumps: SAM inspection on a X-section ▸ Detect sub-surface voids ▸ Discriminate between void and no void 20 µm likely crack in bump voids 20 µm 20 µm 20 µm 20 µm particles on surface (not voids) Experiments done @ PVA TePla 27 © IMEC 2014 OUTLINE Introduction microelectronics Imec- PVA TePla collaboration Back-end of line Micro bumps TSV voids & co Conclusions 28 © IMEC 2014 PROBLEM:TSV VOID Possible reliability effects not really known ▸ Delamination? ▸ Corrosion? ▸ Electromigration effects? (voids grow) ▸ SIV (probably not: needs high stress gradient and many vacancies) How to detect voids? Mass metrology. X-ray, SAM, GHz SAM,... INGRID DE WOLF 29 © IMEC 2014 MASS METROLOGY Can wafer mass monitoring detect voids in TSVs? ▸5x50 mm TSVs with voids with various sizes and void-free TSVs were deliberately generated Mass change due to plating: masspost plating – masspre plating = 995 + 5 mg Can be used for void monitoring if the mass change due to the presence of voids > 5 mg Only expected if voids take more than 15% of Cu volume. INGRID DE WOLF Calculated mass change due to voids noise level 30 © IMEC 2014 X-RAY: 5 X 50 TSVS Experiments on ¼ wafer part: Voids Holes processed on purpose Vendor A INGRID DE WOLF 31 © IMEC 2014 X-RAY: 5 X 50 TSVS Wafer with voids Wafer without voids Vendor B Voids Voids of 2 mm can be detected on wafer level by X-ray INGRID DE WOLF 32 © IMEC 2014 200 MHz C-SCAN F = 5 mm TSV focus on surface Voids deliberately generated during plating no voids not filled large void @ top large void @ top void @ top small void @ top 200 MHz SAM detects differences between some of these samples. Are the differences due to voids? INGRID DE WOLF void @ bottom 33 © IMEC 2014 200MHz AND 1GHz C-SCAN 200MHz SAM F = 5 mm TSV focus on surface 1GHz SAM 1GHz SAM Smaller scan field 80 µm 30 µm GHz SAM: Better spatial resolution INGRID DE WOLF Are these ‘differences’ related to the presence of voids or caused by sound reflection at the overburden? FIB 34 © IMEC 2014 F = 5 mm TSV 1GHz C-SCAN Perfect correlation between FIB and SAM: 1 focus on surface 2 3 4 1GHz SAM SAM detects (big)voids. Smaller scan field 4 3 2 1 FIB 30 µm C-SAM can, if focused at the correct position, detect voids immediately after plating (prove of concept) Further refinements of SAM settings are required. The detection limits are not known yet (better than 0.6 mm in theory for GHz SAM) INGRID DE WOLF 35 © IMEC 2014 C-SCAN & B-SCAN C-scan before polish C-scan after polish FIB FIB 50 µm -30 After polish signature in C-scan is less clear: B-scan 80 µm B-scan: The ‘good TSV’ shows a different signal -40 B-SAM shows promising results for obtaining additional information on void presence and location z [µm] -50 -60 -70 -80 10 20 30 40 x [µm] 50 60 36 INGRID DE WOLF © IMEC 2014 GHZ SAM: FRINGES C-scan after polish After polish signature in C-scan is less clear.... Fringes! FIB Fringes around TSVs. Different at FIB-cut and edge 50 µm 10 µm Can they be used for failure analysis? What is their origin? 37 INGRID DE WOLF © IMEC 2014 GHz SAM: FRINGE ORIGIN Fringe origin 1: thickness variation Interference of waves reflected from top and bottom of chip 50 mm chip Thinned by manual polishing INGRID DE WOLF 38 © IMEC 38 2014 GHz SAM – TSV DEPTH Fringe separation ~ 2 mm 5mm x 30mm TSV Fringe separation ~ 4 mm 5mm x 50mm TSV Fringe distance seems to change with TSV depth: to be confirmed 39 © IMEC 39 2014 GHz SAM – TSV DEPTH 30 µm ( sample D07) 40 µm ( sample D18) 50 µm ( sample D14) Fringes distance seems to increase Fringe distance seems to change with TSV depth Vibration induced noise makes image analysis difficult. Can these fringes be caused by interference between reflected waves from top and bottom TSV???? 40 © IMEC 40 2014 GHz SAM: FRINGE ORIGIN Fringe origin 2: Rayleigh waves (book A. Briggs) ▸ Rayleigh waves are surface waves ▸ Interference between reflected sound waves and Rayleigh waves gives fringe pattern ▸ Depends on focus (picture based on slides from PVA TePla) ▸ Can this be used for failure analysis, to detect for example ‘vertical delamination’ at a TSV? INGRID DE WOLF 41 © IMEC 41 2014 TSV DELAMINATION Expected and also observed mostly at the top of the TSV. Caused by stress/Cu pumping? What was first: void or delamination. Is the void causing delamination? How to detect vertical delamination? Fringes are expected to be affected INGRID DE WOLF 42 © IMEC 2014 GHz SAM – DELAMINATION Experiment 1: TSVs: 10 µm, depth 100 µm ▸ Make ‘delamination’ using FIB Cut: 1 mm wide, estimated depth 1 mm CTR FIB cut Samples with FIB-cut show fringes. Clear difference in signal with and without cut. INGRID DE WOLF 43 © IMEC 43 2014 GHz SAM – DELAMINATION Experiment 2: ▸ GHz SAM on airgap samples after CMP No airgaps Airgaps 20 µm 10 µm TSVs: 5 µm, depth 50 µm Samples with airgaps show fringes. Clear difference in signal with and without airgap. INGRID DE WOLF 44 © IMEC 44 2014 GHz SAM – DELAMINATION Experiment 3: edges and holes Airgap around array of TSVs GHz SAM TSV after etch (no Cu) Optical microsope ▸ Airgaps cause fringes in GHz SAM ▸ Empty TSVs cause fringes in GHz SAM Fringes are correlated with ‘discontinuities’: FA INGRID DE WOLF TSVs: 5 µm, depth 50 µm 45 © IMEC 45 2014 GHz SAM – TSV VOIDS Sample with many voids TSVs: 5 µm, depth 50 µm 25 nm Ta for Cu pumping studies Focus deeper Voids give differences in fringe contrast between TSVs.. Image changes with focus: GHz-data = f(focus depth) required. INGRID DE WOLF 46 © IMEC 46 2014 GHz SAM – TSV DIAMETER 3mm x 50mm TSV 5mm x 50mm TSV 3µm AL142893_D04 5µm AL137363_D02 Fringe also seen near 3 mm TSVs 47 © IMEC 47 2014 GHz SAM – TSV VOIDS Sample with many voids Defect visible in GHz SAM at some positions. Large void or Ta delamination? To be investigated Defects can be detected in samples with voids: failure indication? TSVs: 5 µm, depth 50 µm 25 nm Ta for Cu pumping studies 48 © IMEC 48 2014 CURRENT CHALLENGES Increase understanding of GHz SAM: What do we see? Why? Simulations might help. Future: ▸ Smaller TSVs - TSV void detection (< 1mm voids) - Delamination at sidewalls in TSV - Voids at bottom of TSV ▸ Smaller bumps (5 mm) - Void in bumps after plating - Void in bump connection - Delamination/cracking of bumps ▸ Delamination/cracking of BEOL - Horizontal and vertical pinpointing of delamination/crack position ▸ Thinner stacked chips (50 mm down to 10 mm) 49 © IMEC 2014 GHZ SAM CONCLUSIONS GHz system installed at imec in June ▸ Research focuses on 3D and BEOL ▸ Cracks and delamination in BEOL layers under study ▸ Fringes related to Rayleigh waves/interference were reproduced - Rayleigh wave related fringes are affected by discontinuities (voids, holes, cracks, material inclusions,...) Fringe pattern highly depends on focus: V(z) measurements expected to be required for void analysis - Top-bottom interference fringes are affected by thickness variations Still a lot of work to be done to understand this technique in depth. INGRID DE WOLF 50 © IMEC 50 2014 MANY THANKS PVA TePla Sebastian Brand 51 © IMEC 2014