EPITAXIAL DEPOSITION AND SILICON ON INSULATOR (SOI

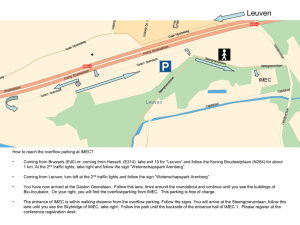

advertisement

The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be EPITAXIAL DEPOSITION AND SILICON ON INSULATOR (SOI) RNT-IMEC EPI/SOI 1 OUTLINE Definitions Applications Epi process Epi tools Epi film characterization SOI SIMOX SmartCut RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 2 Page 1 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be DEFINITIONS Epitaxial- “arranged upon” Homoepitaxy – same substrate and film Si on Si Heteroepitaxy- different substrate and film Silicon on sapphire or Si on Si-Ge (HBT, strained Si) RNT-IMEC EPI/SOI 3 TYPES OF EPITAXY Liquid phase epitaxy (LPE) III-V epi layer; GaAs Refreeze of laser melted silicon Solid phase epitaxy (SPE) Crystalline regrowth of an ion implanted amorphized layerα-Si 550C Vapor phase epitaxy (VPE) is performed by Chemical Vapor Deposition (CVD) Provides excellent control of thickness, doping, and crystallinity High temperature (800-1100C)- autodoping and solid state diffusion RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 4 Page 2 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be EPI DEVICE APPLICATIONS Bipolar transistors All bipolar are built in epi to provide low collector resistance and high breakdown voltages CMOS Improved latchup Improve oxide breakdown characteristics by eliminating polishing defects, COPs, surface roughness Standard in Microprocessors and advanced logic devices Not used in DRAM because of cost issue Inexpensive epi may be used in DRAM Can relax wafer requirements RNT-IMEC EPI/SOI 5 EPI LAYERS IN DEVICES epi layer Bipolar transistor Buried layer CMOS transistors epi layer RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 6 Page 3 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be GASES USED IN SILICON EPI Silane (SiH4) pyrolysis H2 reduction Silicon tetrachloride (Sil Tet) – SiCl4 H2 reduction Trichlorosilane (TCS) – SiHCl3 Si + 2H2 Dichlorosilane (DCS)- SiH2Cl2 SiH4 (H2) H2 reduction Disilane Si2H6 RNT-IMEC EPI/SOI 7 GASES USED IN SILICON EPI Dopant gases Diborane (B2H6) Phosphine (PH3) Arsine (AsH3) RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 8 Page 4 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be EPI DEPOSITION Growth rate Silane>DCS>TCS>sil tet For same temperature Reaction rate controlled RNT-IMEC EPI/SOI 9 TYPES OF EPI DEPOSITION Deposition system APCVD LPCVD RTCVD UHVCVD GSMBE Pressure range (torr) 760 0.1-10 1-10 10-5 10-5-10-6 Silicon precursor DCS DCS Silane, disilane (Si2H6) and DCS Silane, disilane Silane, disilane For CVD below 800C the reaction is surface controlled with an activation energy of ~1.6-2.0 eV RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 10 Page 5 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be EPITAXIAL CVD PROCESSES APCVD- atmospheric pressure CVD (cold-wall reactor) Pressure 760 torr RTCVD (rapid thermal CVD) cold/warm wall LPCVD- cold/warm wall Pressure ~0.1 torr Gas source molecular beam epitaxy (GSMBE) Pressure ~10 torr Pressure ~10-5 torr Ultra-high vacuum CVD (UHVCVD) hot wall Pressure ~10-5-10-6 torr RNT-IMEC EPI/SOI 11 DOPING CONTROL Intentional doping Use PH3, AsH3, or B2H6 for controlled doping Incorporation not linear with dopant in gas phase Dopants change growth rates Doping range for B is 1016-1019/cm3 Doping range for As and P is 1016-1020/cm3 Autodoping Outdiffusion from heavily doped substrate Impurity incorporation from dopant in gas phase RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 12 Page 6 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be DOPING PROFILE IN EPI LAYER RNT-IMEC EPI/SOI 13 MINIMIZING AUTODOPING Fast growth rate to minimize out-diffusion Vapor phase autodoping slows down once surface becomes depleted of dopants Low temperature deposition reduces boron autodoping (not As, however) Seal backside of substrate with lightly doped poly or LT oxide Avoid the use of HCl etching Cap (thin undoped Si) -purge-grow (doped film) Reduced pressure epitaxy Minimize boundary layer and removes dopants to the exhaust RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 14 Page 7 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be GROWING EPI LAYERS Wafer prep Scrub + SC-1 + SC-2- leaves thin oxide layer Remove oxide by high temperature HCl (1-5% in H2) etch Remove oxide by H2 treatment at >800C RNT-IMEC EPI/SOI 15 HYDROGEN PRE-BAKE Hydrogen pre-bake in epi tool in low O2/H2O partial pressure Oxide stable Si stable RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 16 Page 8 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be TYPICAL PROCESS RNT-IMEC EPI/SOI 17 EPI TOOL Upper Outer Lamps Process Gas Injection Quartz Upper Inner Lamps Pyrometer #1 Exhaust Laminar Gas Flow Lower Outer Lamps Lower Inner Lamps Stainless Steel Energy from Lamps Pyrometer #2 RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 18 Page 9 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be LOW TEMPERATURE EPI Low temperature required for Si-Ge HBT Selective epi Raised source drain isolation Low temperature conventional epi Ultra-high vacuum (UHV) deposition (IBM) Low temperature rapid thermal deposition (RTCVD) RNT-IMEC EPI/SOI 19 SELECTIVE EPI GROWTH Growth over exposed silicon only TYPE 1 Siltet>TCS>DCS TYPE 2 RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 20 Page 10 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be SELECTIVE EPI GROWTH RNT-IMEC EPI/SOI 21 CHARACTERIZATION OF EPI FILMS Optical surface inspection for defects Electrical Slip, Stacking fault, and dislocations Sheet resistance – 4-pt. Probe SRP to interface to measure the doping profile Thickness FTIR tools RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 22 Page 11 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be STRAINED SILICON Put strain in the lattice by using Si-Ge then depositing strained Si on top- processing is done in the Si Different than using Si-Ge for process layer Increased electron and hole mobility Drive current increased by about 10-20% RNT-IMEC EPI/SOI 23 STRAINED SILICON SOURCE: SOITEC RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 24 Page 12 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be STRAINED SILICON LAYERS IBM web site RNT-IMEC EPI/SOI 25 STRAINED SILICON LATTICE Intel web site RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 26 Page 13 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be STRAINED SILICON IMPROVES CHANNEL MOBILITY SOURCE IMEC http://www.imec.be /wwwinter/processing/asd /activities/strained.shtml RNT-IMEC EPI/SOI 27 WHY SILICON ON INSULATOR (SOI) Reduced junction capacitance Reduced reverse body effect Oxide capacitance less than reversed biased p-n junction The SOI transistor body potential is floating instead of contacted as in bulk devices. More devices can be stacked at low voltage (e.g., 3 input vs. 2- input logic gates can be designed Faster speeds Enhanced circuit speed as much as 20-50% at device operating temperatures RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 28 Page 14 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be WHY SOI? Reduced soft error sensitivity Charge collection volumes are limited by the buried oxide layer. Becomes more important as voltages and device dimensions decrease Devices are free of latch-up Fabrication process is simplified by reducing the number of masking steps by as much as 30% Result in smaller circuit layout RNT-IMEC EPI/SOI 29 IMPROVED CIRCUIT LAYOUT PMOS N+ P+ NMOS P+ N+ N-well NMOS P+ N+ N+ Buried oxide RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 P+ Bulk inverter PMOS P+ N+ SOI inverter 30 Page 15 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be ISSUES WITH SOI Substrate costs Low thermal conductivity (buried oxide) for high power devices Floating body electrical effects RNT-IMEC EPI/SOI 31 APPLICATIONS OF SOI IBIS website RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 32 Page 16 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be SIMOX FORMATION High dose oxygen implant in the bulk Si substrate 4x1017-2x1018 atoms/cm2 Requires special implanters Buried oxide thickness control(energy) 80-400 nm Implant causes damage to silicon Dislocations, stacking faults, etc Requires special dedicated implanters (IBIS, Hitachi) High temperature anneal (~1320C) Forms buried oxide layer (BOX) Damaged silicon layer recrystallizes Requires capping layer to prevent silicon evaporation RNT-IMEC EPI/SOI 33 SIMOX PROCESS O+, 4x1017-2x1018 atoms/cm2 O in silicon 1320C anneal to form Buried oxide (BOX) BOX epi May deposit epi to increase Si thickness RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 34 Page 17 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be MODIFIED LOW DOSE (MLD) SIMOX Reduces implant time BOX thickness ~ 135 nm SOI thickness ~ 145 nm SIMOX implanter –IBIS 45 mA beam current T (wafer) 300-570C 13 wafers/batch 300mm RNT-IMEC EPI/SOI 35 SMARTCUT (SOITEC Unibond) PROCESS : Initial silicon A Buried oxide Oxidation H+ ions 5x1016 cm-2 Smart-Cut implant Cleaning and bonding A B RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 B He can also be used Can be performed using PII Wet clean or plasma treated bonding 36 Page 18 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be SMARTCUT PROCESS A SmartCut splitting at 500°C B Annealing 1100°C CMP touch polishing SOI wafer Wafer A becomes B A New A RNT-IMEC EPI/SOI 37 SMARTCUT VS SIMOX SIMOX Oxygen implant Specific implanter 3 low-dose wafers/hour (8") No bonding No splitting 1300°C anneal Recrystallized SmartCut Thermal buried oxide Hydrogen implant Standard implanter 16 wafers/hour (8") SiO2/Si bonding Splitting 1100°C anneal Polishing Starting silicon quality RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 38 Page 19 The Microelectronics Training Center, IMEC v.z.w. www.imec.be/mtc delfi.imec.be TEM OF SILICON/OXIDE SMARTCUT INTERFACE Silicon film Top interface Bottom interface Substrate (Back gate) RNT-IMEC EPI/SOI 39 STRAINED SILICON ON INSULATOR SOURCE: SOITEC RNT-IMEC EPI/SOI MTC 2003 : Silicon Processing course IMEC© 2003 40 Page 20