Three-Layer Polysilicon Surface Micromachining Process

advertisement

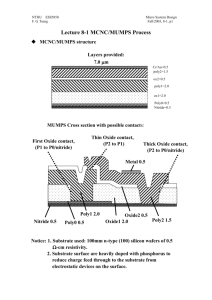

Chapter 1 Three-Layer Polysilicon Surface Micromachining Process 1.1 Introduction The Multi-User MEMS Processes or MUMPs™ is a commercial program that provides the international industrial, governmental and academic communities with cost-effective, proof-of-concept surface micromachining fabrication. MUMPs™ is designed for general purpose micromachining by outside users who would like to fabricate MEMS devices. The following is a general description of the MUMPs™ process geared toward users of the MUMPs™ service who may not have a strong background in microfabrication, but it contains information that is useful to all MUMPs™ users. Figure 1.1. Cross sectional view showing all 7 layers of the MUMPs™ process (not to scale). Figure 1.1 is a cross section of the three-layer polysilicon surface micromachining MUMPs™ process. This process has the general features of a standard surface micromachining process: (1) polysilicon is MUMPs™ Design Handbook – 5/26/99 1 Three-Layer Polysilicon Surface Micromachining Process used as the structural material, (2) deposited oxide (PSG) is used as the sacrificial layer, and silicon nitride is used as electrical isolation between the polysilicon and the substrate. The process is different from most customized surface micromachining processes in that it is designed to be as general as possible, and to be capable of supporting many different designs on a single silicon wafer. Since the process was not optimized with the purpose of fabricating any one specific device, the thicknesses of the structural and sacrificial layers were chosen to suit most users, and the layout design rules were chosen conservatively to guarantee the highest yield possible. 1.2 Process Overview The MUMPs™ process is a three-layer polysilicon surface micromachining process derived from work performed at the Berkeley Sensors and Actuators Center (BSAC) at the University of California in the late 80’s and early 90’s. Several modifications and enhancements have been made to increase the flexibility and versatility of the process for the multi-user environment. The process flow described below is designed to introduce inexperienced users to polysilicon micromachining. The text is supplemented by detailed drawings that show the process flow in the context of building a typical micromotor. The process begins with 100 mm n-type (100) silicon wafers of 1-2 Ω-cm resistivity. The surface of the wafers are first heavily doped with phosphorus in a standard diffusion furnace using POCl3 as the dopant source. This helps to reduce or prevent charge feedthrough to the substrate from electrostatic devices on the surface. Next, a 600 nm low-stress LPCVD (low pressure chemical vapor deposition) silicon nitride layer is deposited on the wafers as an electrical isolation layer. This is followed directly by the deposition of a 500 nm LPCVD polysilicon film–Poly 0. Poly 0 is then patterned by photolithography, a process that includes the coating of the wafers with photoresist (Figure 1.2), exposure of the photoresist with the appropriate mask and developing the exposed photoresist to create the desired etch mask for subsequent pattern transfer into the underlying layer (Figure 1.3). After patterning the photoresist, the Poly 0 layer is then etched in an RIE (Reactive Ion Etch) system (Figure 1.4). A 2.0 µm phosphosilicate glass (PSG) sacrificial layer is then deposited by LPCVD (Figure 1.5) and annealed @1050˚C for 1 hour in argon. This layer of PSG, known as First Oxide, is removed at the end of the process to free the first mechanical layer of polysilicon. The sacrificial layer is lithographically patterned with the DIMPLES mask and the dimples are transferred into the sacrificial PSG layer by RIE, as shown in Figure 1.6. The nominal depth of the dimples is 750 nm. The wafers are then patterned with the third mask layer, ANCHOR1, and reactive ion etched (Figure 1.7). This step provides anchor holes that will be filled by the Poly 1 layer. After etching ANCHOR1, the first structural layer of polysilicon (Poly 1) is deposited at a thickness of 2.0 µm. A thin (200 nm) layer of PSG is deposited over the polysilicon and the wafer is annealed at 1050˚C for 1 hour (Figure 1.8). The anneal dopes the polysilicon with phosphorus from the PSG layers both above and below it. The anneal also serves to significantly reduce the net stress in the Poly 1 layer. The polysilicon (and its PSG masking layer) is lithographically patterned using a mask designed to form the first structural layer POLY1. The PSG layer is etched to produce a hard mask for the subsequent polysilicon etch. The hard mask is more resistant to the polysilicon etch chemistry than the photoresist and ensures better transfer of the pattern into the polysilicon. After etching the polysilicon (Figure 1.9), the photoresist is stripped and the remaining oxide hard mask is removed by RIE. After Poly 1 is etched, a second PSG layer (Second Oxide) is deposited and annealed(Figure 1.10). The Second Oxide is patterned using two different etch masks with different objectives. The POLY1_POLY2_VIA level provides for etch holes in the Second Oxide down to the Poly 1 layer. This provide a mechanical and electrical connection between the Poly 1 and Poly 2 layers. The POLY1_POLY2_VIA layer is lithographically patterned and etched by RIE (Figure 1.11). The ANCHOR2 level is provided to etch both the First and Second Oxide layers in one step, thereby eliminating any mis-alignment between separately etched holes. More importantly, the ANCHOR2 etch eliminates the need to make a cut in First Oxide unrelated to anchoring a Poly 1 structure, which need- 2 MUMPs™ Design Handbook -5/26/99 Process Overview lessly exposes the substrate to subsequent processing that can damage either Poly 0 or Nitride (see Section 2.3.3). The ANCHOR2 layer is lithographically patterned and etched by RIE in the same way as POLY1_POLY2_VIA. Figure 1.12 shows the wafer cross section after both POLY1_POLY2_VIA and ANCHOR2 levels have been completed. The second structural layer, Poly 2, is then deposited (1.5 µm thick) followed by the deposition of 200 nm PSG. As with Poly 1, the thin PSG layer acts as both an etch mask and dopant source for Poly 2 (Figure 1.13). The wafer is annealed for one hour at 1050 C to dope the polysilicon and reduce the residual film stress. The Poly 2 layer is lithographically patterned with the seventh mask (POLY2) and the PSG and polysilicon layers are etched by RIE using the same processing conditions as for Poly 1. The photoresist then is stripped and the masking oxide is removed (Figure 1.14). The final deposited layer in the MUMPs™ process is a 0.5 µm metal layer that provides for probing, bonding, electrical routing and highly reflective mirror surfaces. The wafer is patterned lithographically with the eighth mask (METAL) and the metal is deposited and patterned using lift-off. The final, unreleased structure is shown in Figure 1.15. The wafers are diced, sorted and shipped to the MUMPs™ user for sacrificial release and test. Figure 1.16 shows the device after sacrificial oxide release. The release is performed by immersing the chip in a bath of 49% HF (room temperature) for 1.5-2 minutes. This is followed by several minutes in DI water and then alcohol to reduce stiction followed by at least 10 minutes in an oven at 1100 C. Generally the participants receive their dice and perform the sacrificial oxide release in their own facility. For those participants who request it, release of their dice at Cronos’ facility can be arranged for an additional fee. Figure 1.2. The surface of the starting n-type (100) wafers are heavily doped with phosphorus in a standard diffusion furnace using POCl 3 as the dopant source. A 600 nm blanket layer of low stress silicon nitride (Nitride) is deposited followed by a blanket layer of 500 nm polysilicon (Poly 0). The wafers are then coated with UV-sensitive photoresist. MUMPs™ Design Handbook – 5/26/99 3 Three-Layer Polysilicon Surface Micromachining Process 4 Figure 1.3. The photoresist is lithographically patterned by exposing it to UV light through the first level mask (POLY0) and then developing it . The photoresist in exposed areas is removed leaving behind a patterned photoresist mask for etching. Figure 1.4. Reactive ion etching (RIE) is used to remove the unwanted polysilicon. After the etch, the photoresist is chemically stripped in a solvent bath. This method of patterning the wafers with photoresist, etching and stripping the remaining photoresist is used repeatedly in the MUMPs™ process. Figure 1.5. A 2.0 µm layer of PSG is deposited on the wafers by low pressure chemical vapor deposition (LPCVD). This is the first sacrifical layer. MUMPs™ Design Handbook – 5/26/99 Process Overview Figure 1.6. The wafers are coated with photoresist and the second level (DIMPLE) is lithographically patterned. The dimples, 750 nm deep, are reactive ion etched into the first oxide layer. After the etch, the photoresist is stripped. Figure 1.7. The wafers are re-coated with photoresist and the third level (ANCHOR1) is lithographically patterned. The unwanted oxide is removed in an RIE etch and the photoresist is stripped. Figure 1.8. A blanket 2.0 µm layer of un-doped polysilicon is deposited by LPCVD followed by the deposition of 200 nm PSG and a 1050˚C/1 hour anneal. The anneal serves to both dope the polysilicon and reduce its residual stress. MUMPs™ Design Handbook – 5/26/99 5 Three-Layer Polysilicon Surface Micromachining Process Figure 1.9. The wafer is coated with photoresist and the fourth level (POLY1) is lithographically patterned. The PSG is first etched to create a hard mask and then Poly 1 is etched by RIE. After the etch is completed, the photoresist and PSG hard mask are removed. Figure 1.10. The Second Oxide layer, 0.75 µm of PSG, is deposited on the wafer. This layer is patterned twice to allow contact to both Poly 1 and substrate layers. Figure 1.11. The wafer is coated with photoresist and the fifth level (POLY1_POLY2_VIA) is lithographically patterned. The unwanted Second Oxide is RIE etched, stopping on Poly 1, and the photoresist is stripped. 6 MUMPs™ Design Handbook – 5/26/99 Process Overview Figure 1.12. The wafer is re-coated with photoresist and the sixth level (ANCHOR2) is lithographically patterned. The Second and First Oxides are RIE etched, stopping on either Nitride or Poly 0, and the photoresist is stripped. The ANCHOR2 level provides openings for Poly 2 to contact with Nitride or Poly 0. Figure 1.13. A 1.5 µm un-doped polysilicon layer is deposited follwed by a 200 nm PSG hardmask layer. The wafers are annealed at 1050˚C for one hour to dope the polysilicon and reduce residual stress. Figure 1.14. The wafer is coated with photoresist and the seventh level (POLY2) is lithographically patterned. The PSG hard mask and Poly 2 layers are RIE etched and the photoresist and hard mask are removed. All mechanical structures have now been fabricated. The remaining steps are to deposit the metal layer and remove the sacrificial oxides MUMPs™ Design Handbook – 5/26/99 7 Three-Layer Polysilicon Surface Micromachining Process Figure 1.15. The wafer is coated with photoresist and the eighth level (METAL) is lithographically patterned. The metal (gold with a thin adhesion layer) is deposited by lift-off patterning which does not require etching. The side wall of the photoresist is sloped at a reentrant angle, which allows the metal to be deposited on the surfaces of the wafer and the photoresist, but provides breaks in the continuity of the metal over the reentrant photoresist step. The photoresist and unwanted metal (atop the photoresist) are then removed in a solvent bath. The process is now complete and the wafers can be coated with a protective layer of photoresist and diced. The chips are sorted and shipped. Figure 1.16. The structures are released by immersing the chips in a 49% HF solution. The Poly 1 “rotor” can be seen around the fixed Poly 2 hub. The stacks of Poly 1, Poly 2 and Metal on the sides represent the stators used to drive the motor electrostatically. 8 MUMPs™ Design Handbook – 5/26/99 Chapter 2 MUMPs™ Design Guidelines and Rules 2.1 Design Rules and Considerations 2.1.1 Introduction The purpose of the design rules is to ensure the greatest possibility of successful fabrication. The rules have evolved through process development, the experience of the Cronos staff, and most importantly, experience from previous MUMPs™ runs. The design rules are a set of requirements and advisements that are defined by the limits of the process (i.e. the stable process window) which in turn is defined by the capabilities of the individual process steps. In general, minimum design rules are defined by the resolution and alignment capabilities of the lithography system. This section of the document describes the design rules, both mandatory and advisory, that exist for the MUMPs™ three-layer polysilicon micromachining process. Design rules in the document define the minimum feature sizes and spaces for all levels and minimum overlap and spacing between relevant levels. The minimum line widths and spaces are mandatory rules . Mandatory rules are given to ensure that all layouts will remain compatible with Cronos’s lithographic process tolerances. Violation of minimum line/space rules will result in missing, undersized, oversized or fused features. Minimum overlap (enclosure, cut-in and cutout rules) requirements reduce the effect of large topographies and prevent unnecessary etching of underlying layers. Minimum spacing between levels guarantees that features of two different levels can be delineated by photolithography and etch. Please note: The minimum geometry allowed should not be confused with thenominalgeometryadesigneruses.Minimumgeometriesshouldonlybeusedwhereabsolutely necessary. When size is not an issue, the feature should be designed larger than the minimum allowed value. In general, the enclosure and interlevel spacing rules are advisory rules. Cronos recognizes that there may be valid reasons requiring that an enclosure or interlevel spacing rule be violated. We also recognize the limitations of our process and equipment. As such, we try to explain why an advisory rule exists and the possible or probable consequence of violating it. We allow users to ignore the advisory rules, MUMPs™ Design Handbook - 5/21/99 9 MUMPs™ Design Guidelines and Rules but at their own risk. Cronos is not responsible for the possible processing consequence of violating an advisory rule. A word on the conventions followed in this document. Lithography levels (i.e. names for each masking level) will be written in upper case. When referring to a specific layer of material, be it oxide or polysilicon, the material will be typed in lower case with the first letter capitalized. For example POLY1 refers to the masking level for patterning the first polysilicon layer. Table 2.1 outlines the material layer names, thicknesses and the lithography levels associated with those layers. Table 2.1. Layer names, thicknesses and lithography levels. Hole levels are printed on the same line as their corresponding polysilicon or metal levels. Material Layer Thickness ( µm) Lithography Level Name Nitride 0.6 -- Poly 0 0.5 POLY0 (HOLE0) First Oxide 2.0 Poly 1 2.0 Second Oxide 0.75 Poly 2 1.5 POLY2 Metal 0.5 METAL DIMPLE ANCHOR1 POLY1 (HOLE1) POLY1_POLY2_VIA ANCHOR2 (HOLE2) (HOLEM) 2.2 Design Rules The design rules for the MUMPs™ process are described both in tabular form and in schematic drawings. The tables list the rules and give references to the specific figure in which the rule is described. There are 14 mandatory rules. These are highlighted with an asterisk (*) in the tables and printed in bold text to help distinguish them. All other rules are cautionary guidelines (advisory rules) which should only be violated for specific desired applications1. Table 2.2 lists the field convention used in the Cronos process and a brief description of the purpose of each level. All polysilicon levels are light field and all oxide levels are dark field. [Please note that the data should always be drawn (digitized) as described in the rules and not based upon your historical understanding of the light and dark field conventions. Too often the terms light field and dark field mean different things in different facilities. The convention used here is that accepted by the commercial mask maker used by Cronos.] In light field levels, draw the feature–the object you want left behind after the etch. In dark field levels, draw the holes–the areas you want to etch away. For example, POLY0 is a light field level. When drawing POLY0, you will draw (digitize) the poly structures. When drawing ANCHOR1, a dark field level, you will draw the holes that will later serve as Poly 1 anchor holes. Please pay special attention to this concept. Failure to comply with this convention will result in layer polarity reversals. 1. Cronos is not responsible for process consequences that might result from violating either mandatory or advisory rules. 10 MUMPs™ Design Handbook - 5/21/99 Design Rules Mask conventions Table 2.2. Mnemonic Level Name Field type Purpose POLY0 light pattern ground plane ANCHOR1 dark open holes for Poly 1 to Nitride or Poly 0 connection DIMPLE dark create dimples/bushings for Poly 1 POLY1 light pattern Poly 1 POLY1_POLY2_VIA dark open holes for Poly 1 to Poly 2 connection ANCHOR2 dark open holes for Poly 2 to Nitride or Poly 0 connection POLY2 light pattern Poly 2 METAL light pattern Metal HOLE0 dark provide holes for POLY0 HOLE1 dark provide release holes for POLY1 HOLE2 dark provide release holes for POLY2 HOLEM dark provide release holes in METAL Table 2.3 lists the cross reference between Cronos’s descriptive name, the CIF name and the GDS level number. These are the level names and numbers referred to in the process guide and in any communications you may have with Cronos’s layout support. Please adopt this naming scheme on your own Table 2.3. Cronos level name, CIF and GDSII™ level designation, and nominal and minimum features and spaces for each level. Mnemonic level name CIF level name GDS level number Nominal line/space Minimum feature Minimum space *POLY0 CPZ 13 3.0 2.0 2.0 *ANCHOR1 COF 43 3.0 3.0 2.0 *DIMPLE COS 50 3.0 2.0 3.0 *POLY1 CPS 45 3.0 2.0 2.0 *POLY1_POLY2_VIA COT 47 3.0 2.0 2.0 *ANCHOR2 COL 52 3.0 3.0 2.0 *POLY2 CPT 49 3.0 2.0 2.0 *METAL CCM 51 3.0 3.0 3.0 *HOLE0 CHZ 41 3.0 2.0 2.0 *HOLE1 CHO 0 4.0 3.0 3.0 *HOLE2 CHT 1 4.0 3.0 3.0 *HOLEM CHM 48 5.0 4.0 4.0 MUMPs™ Design Handbook - 5/21/99 11 MUMPs™ Design Guidelines and Rules Cross Sections Poly0 Oxide1 Oxide2 H Poly1 Poly2 Metal Anchor2 Metal L Mask Levels Poly0 Anchor1 Poly1 Poly1-Poly2 Via Poly2 Dimple Figure 2.9. H: POLY1 enclose POLY1_POLY2_VIA–4.0 µm The distance between the POLY1_POLY2_VIA hole and the edge of Poly 1 necessary to ensure the via hole is entirely over Poly 1. L: POLY2 enclose POLY1_POLY2_VIA–4.0 µm The amount Poly 2 must extend beyond the POLY1_POLY2_VIA hole to ensure complete coverage of the hole. 20 MUMPs™ Design Handbook - 5/21/99 Table 2.7. 28 MUMPs™ Design Handbook - 5/21/99 2 4/H/2.9 POLY1_POLY2_VIA 2 4/N/2.13 DIMPLE HOLE2 HOLE1 HOLE2 2/T/2.16 2/U/2.16 3/M/2.12 5/J/2.7 ANCHOR2 METAL 4/L/2.9 VIA POLY1 POLY0 - 4/O/2.14 4/G/2.6 POLY2 ANCHOR2 ANCHOR1 POLY0 2 5/D/2.7 POLY2 2 5/E/2.8 ANCHOR2 - 4/C/2.6 Enclose POLY1 2 Minimum Spacing 4/B/2.5 2 Minimum Feature ANCHOR1 - Level 2 HOLEM POLY2 POLY1 POLY0 Level 1 3/I/2.10 3/K/2.11 5/F/2.8 4/A/2.5 Spacing 5/P/2.14 Cut-In 4/Q/2.14 Cut-Out Design rule reference sheet. Table shows minimum dimensions (µm) (bold text), rule name and figure number, respectively. MUMPs™ Design Guidelines and Rules Process and Design Issues (or Hints and Pitfalls) Section 2.3 is highly recommended reading for any MUMPs™ user, novice or experienced. It includes several common design errors that warrant extended discussion based on observations from previous MUMPs™ runs. This section also contains guidelines for several processing methods that may be of interest. 2.3 Process and Design Issues (or Hints and Pitfalls) This section is based upon the experience Cronos has gained working with many groups of people, both novices and experts in the area of MEMS. Below are some of the more common errors made in designing surface micromachined MEMS along with some helpful hints. 2.3.1 Layout convention This was covered in section 2.2 but will be reiterated here. The convention used by the MUMPs™ processes in defining mask levels is simple. For all polysilicon levels and the metal level (POLY0, POLY1, POLY2 and METAL) the masks are light field. For these levels, draw (i.e. digitize) the polysilicon (or metal) feature you want to keep. All oxide levels and hole levels (DIMPLE, ANCHOR1, ANCHOR2, POLY1_POLY2_VIA and HOLE0,1,2,M) are dark field. For these levels, draw the hole you want to make. It is imperative that these conventions be followed for your devices to be fabricated correctly. 2.3.2 Don’t put a hole where you don’t need it. The MUMPs™ process has three levels for making polysilicon connections and anchors–ANCHOR1, ANCHOR2 and POLY1_POLY2_VIA. The purpose of these levels is outlined in Table 2.2. An error made frequently by beginning users is to place oxide holes where they are not needed (i.e. to not fill a hole with polysilicon). This detrimentally affects the device in two distinct ways. First, stringers may form inside the anchor holes when removing the polysilicon. Second, and more importantly, the underlying layers are exposed to unnecessary etching that can thin or remove them altogether. The following example illustrates the effect of not adequately covering ANCHOR1 holes with POLY1. Figure 2.17 shows ANCHOR1 holes etched down to both Poly 0 and Nitride. Some of the Nitride is removed in the overetch of the ANCHOR1 holes. Figure 2.18 shows the same anchor holes after the Poly 1 layer has been etched. In this case, the ANCHOR1 holes are not entirely covered by Poly 1 and the underlying layers are attacked further. The Nitride layer is thinned to the point where shorting to the substrate can occur and the exposed Poly 0 is completely removed resulting in unintentional isolation of Poly 0 structures. In addition, a 4 to 4.5 µm step has been produced which complicates lithography at subsequent steps. AAAAAAAAA AAAAAAAAAAAAAAAA AAAAAAAAA Figure 2.17. ANCHOR1 cuts down to Nitride and Poly 0. Note that the underlying Nitride has been partially etched (see fig. 1.1 for fill patterns). MUMPs™ Design Handbook - 5/21/99 29