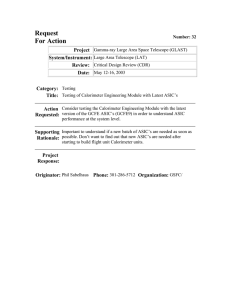

a digitally programmable application specific integrated circuit for

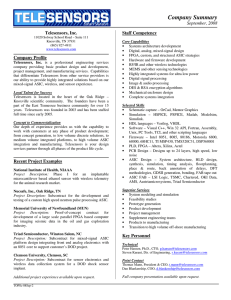

advertisement