Laboratory 5

advertisement

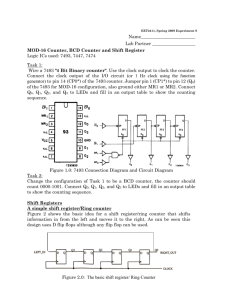

Name: ECE Box Number: Name: ECE Box Number: Laboratory #5 ECE 2022 1 Introduction This laboratory consists of three parts. In the first part you will build an RS flip flop using NAND gates. In the second and third parts you will be exploring the timing differences between an asynchronous counter and a synchronous counter. As results from these experiments you have to complete the following items: RS Flip Flop: 1. Build the RS flip flop 2. Demonstrate it to the TA Asynchronous Counter: 1. Build the Asynchronous Counter 2. Connect it to your 1 Hz Clock and demonstrate it to the TA 3. Connect it to the function generator set to maximum frequency 4. Draw the waveforms in the provided figures Synchronous Counter: 1. Build the Synchronous Counter 2. Connect it to your 1 Hz Clock and demonstrate it to the TA 3. Connect it to the function generator set to maximum frequency 4. Draw the waveforms in the provided figures 2 RS Flip Flop In this part of the lab you will build an RS flip flop using NAND gates. The circuit diagram is shown in Figure 1. Pin 7 of the 74LS00 is ground and Pin 14 is Vcc. Connect a wire to each input R and S as shown in Figure 1. Connect each of the outputs Q and Q to an input of your LED drivers. When you tap wire 1 to ground the flip flop gets set, when you tap wire 2 to ground it gets reset. Demonstrate this circuit to the TA. 1 2 ECE 2022 Lab #5 VCC R1 1KΩ S PSfrag replacements 1 3 Q 6 Q 2 wire 1 4 R2 1KΩ R 5 wire 2 Figure 1: RS Flip Flop Schematic 3 Asynchronous Counter The asynchronous counter described here is constructed from JK flip flops. The inputs J and K are tied together to form a toggle flip flop. Each flip flop toggles its output at the falling edge of the input clock, i.e. it divides the clock by two. In an asynchronous counter the clock of the flip flop is driven by the output of the previous flip flop. This causes the the delays to add up. You will examine this behavior. Build the asynchronous counter shown in Figure 2. The 74LS112 IC contains two JK flip flops. Pin 8 of this IC is ground and Pin 16 is Vcc. The outputs Q0 through Q3 should be connected to your LED driver circuit inputs. VCC 4 3 1 2 15 CLK PRE J Q CLK K Q 4 3 5 1 2 15 6 CLR U1 PRE J 10 Q CLK K Q CLR U2 5 11 6 13 12 14 PRE J 10 Q CLK K Q 9 11 7 13 12 CLR U1 14 PRE J Q CLK K Q 9 7 CLR U2 Q0 Q1 Q2 Q3 Figure 2: Asynchronous Counter Schematic 3.1 Using a 1 Hz Clock Connect the input “CLK” to the 1 Hz clock that you built for pre-lab. Show the functioning circuit to the TA. 3.2 Using a fast Clock Set the function generator to the highest frequency possible, selecting a square wave. Connect CH1 of the oscilloscope directly to the function generator Adjust the generator so that the square wave goes from 0 Volt to 5 Volt. Measure the frequency and write it below. Caution: You will be asked to connect this signal generator output to your logic circuit. Your circuit could possibly be damaged if you do not have the signal generator appropriately adjusted. 3 ECE 2022 Lab #5 Be sure the oscilloscope is set to the DC and not AC mode. Short the input probe of the scope and adjust it so that the 0V input you have introduced shows up as a line at exactly the center of the screen. Be sure you know what scale you are in, that is, how many volts per division of deflection. Double check this last setting by now unshorting the probe and connecting it to your power supply ground and 5 V terminals. Do you read this as 5 V on the screen? If so, continue, and perform the signal generator setting after both connecting the oscilloscope ground clip to the black signal generator clip and the probe tip to the red signal generator clip. Frequency = Now connect the output of the function generator to the input “CLK” of your counter. Remember: that means both connecting the black signal generator clip to your circuit’s ground connection, and the red clip to the CLK input. Connect CH1 of the oscilloscope to the output Q 3 and CH2 to the output Q0 . Set the trigger on the oscilloscope to respond to CH1 and adjust the settings so that you see one full waveform on CH1. (This part of the experiment is a good one to learn the meaning of the various trigger setting options on the oscilloscope - talk to the TA about this if necessary.) Next adjust the oscilloscope so that the rising edge of the output waveform Q 3 on CH1 fills about half the screen. Measure the distance between the center of the rising edge of Q 3 and the center of the falling edge of Q0 . Draw the waveform into Figure 3. Note the settings for Volts/Div. and sec/Div. for each channel and mark the ground position of CH1 and CH2. Next adjust the Channel 1 Volts/Div sec/Div Channel 2 Volts/Div sec/Div Figure 3: Rising Edge of Q3 on Asynchronous Counter oscilloscope so that the falling edge of the Q3 fills about half the screen. Measure the distance between the center of the falling edge of Q3 and the center of the rising edge of Q0 . Draw the waveform into Figure 4. Note the settings for Volts/Div., sec/Div. for each channel and mark the ground position of CH1 and CH2. Enter the values for falling and rising edge delay below. Falling Edge Delay = Rising Edge Delay = 4 ECE 2022 Lab #5 Channel 1 Volts/Div sec/Div Channel 2 Volts/Div sec/Div Figure 4: Falling Edge of Q3 on Asynchronous Counter 4 Synchronous Counter The synchronous counter is also comprised of JK flip flops. The inputs J and K are tied together to form a toggle flip flop. Each flip flop toggles its output at the falling edge of the input clock. The difference from the asynchronous counter is that the clock inputs of all flip flops are connected to the same clock. The flip flops do not toggle anymore at every single clock cycle. A simple logic using two AND gates determines if the flip flops toggle. As the clock inputs of all flip flops are connected to the same clock it is called a synchronous counter. The delays do not add up. You will examine this behavior. Build the synchronous counter shown in Figure 5. The IC 74LS112 contains two JK flip flops. Pin 8 of this IC is ground and Pin 16 is Vcc. The IC 74LS08 contains four AND gates. Pin 7 of this IC is ground and Pin 14 is Vcc. The outputs Q0 through Q3 should be connected to your LED driver circuit inputs. 1 12 3 11 2 13 VCC 4 3 1 2 15 PRE J Q CLK K CLR Q 5 6 4 3 1 2 15 PRE J 10 Q CLK K CLR Q 5 11 6 13 12 14 PRE J 10 Q CLK K Q CLR CLK 9 11 7 13 12 14 PRE J Q CLK K Q 9 7 CLR Q0 Q1 Q2 Q3 Figure 5: Synchronous Counter Schematic 5 ECE 2022 Lab #5 4.1 Using a 1 Hz Clock Connect the input “CLK” to the 1 Hz clock that you built for pre-lab. Show the functioning circuit to the TA. 4.2 Using a fast Clock Set the function generator to the highest frequency possible, selecting a square wave. Connect CH1 of the oscilloscope directly to the function generator Adjust the generator so that the square wave goes from 0 Volt to 5 Volt. Measure the frequency and write it below. Frequency = Now connect the output of the function generator to the input “CLK” of your counter. Connect CH1 of the oscilloscope to the output Q3 and CH2 to the output Q0 . Set the trigger on the oscilloscope to respond to CH1 and adjust the settings so that you see one full waveform on CH1. Next adjust the oscilloscope so that the rising edge of the output waveform Q 3 on CH1 fills about half the screen. Measure the distance between the center of the rising edge of Q 3 and the center of the falling edge of Q0 . Draw the waveform into Figure 6. Note the settings for Volts/Div. and sec/Div. for each channel and mark the ground position of CH1 and CH2. Next adjust the Channel 1 Volts/Div sec/Div Channel 2 Volts/Div sec/Div Figure 6: Rising Edge of Q3 on Synchronous Counter oscilloscope so that the falling edge of the Q3 fills about half the screen. Measure the distance between the center of the falling edge of Q3 and the center of the rising edge of Q0 . Draw the waveform into Figure 7. Note the settings for Volts/Div., sec/Div. for each channel and mark the ground position of CH1 and CH2. Enter the values for falling and rising edge delay below. Falling Edge Delay = Rising Edge Delay = 6 ECE 2022 Lab #5 Channel 1 Volts/Div sec/Div Channel 2 Volts/Div sec/Div Figure 7: Falling Edge of Q3 on Synchronous Counter