High bandwidth transimpedance amplifier design using active

advertisement

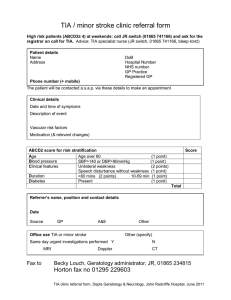

High Bandwidth Transimpedance Amplifier Design Using Active Transmission Lines Hyeon-Min Bae. Naresh Shanbhag Coordinated Science Laboratory Department of Electrical and Computer Engineering, University of Illinois, Urbana-Champaign, Urbana, IL-61801 Abstract- A transimpedance amplifier (TIA) is designed based on the first order wave equation. The feedback resistance is set as the ohJective function for transimpedance. The main feedback amplifier provides transimpedance and a wide band compensation amplifier determines the characteristics of overall TIA. The stability of lhe T l A is not affected due to the open loop nature of compensation. Simulation results show that the TIA achieves a 58 dB gain and 1.32 GHz bandwidth in a 0.25 ym standard CMOS process. Index Terms-TIA, wave equation, active transmission lines un = V&he output node) and Then (3) becomes = V,,(the input node). 4: where A' = Equation ( 5 ) is the description of a unity.gain feedback amplifier. The dispersion relation can be found by substituting = aeJ(kn+wt) (6) in ( 5 ) to obtain 1. INTRODUCTiON A lossless transmission line can be described as By substituting (7) into (61, we get gain factor G given by, which is called a wave equation where 1 and x represents the time and space axis, respectively. The equation consists of two terms, one of which is propagating to the right (positive x) and the other to the left. T h e first order wave equation that propagates to the right is given by + The general solution of above equation is f (x ct). implying that a wave is propagating at a speed c. In reality, an ideal integrator required to implement (2) is not feasible. However, the above equation can be written in an implementable form as follows The truncation error T of ( 5 ) is found by using Taylor expansion at U,, which is given by 1 1 T=a(-hu,,- z ( h ) * u z z z " ' ) , (9) 2 where uzz and U,,, are the second and third order spatial derivatives of U(+, t ) , respectively. It is clear that a unity gain feedback amplifier is highly dispersive because all the high order terms appear. I I . H I G HBANDWIDTH TIA DESIGN In this section, a transimpedance amplifier (TIA) will be configured using an active transmission line and a design procedure will be presented. A TIA is used to conven the where A is the gain of the amplifier and p is the 3-db pole current into voltage. The TiA requirements are high bandwidth location. With an initial condition of u ( 0 , t ) = asin(wt), (0.7 times the data rate), high gain, low noise (< ImA). A simple resistor is a transimpedance device but it is not effective u(0,O) = 0 and u'(0,O) = 0, we solve (3) to get in terms of gain-bandwidth product. The capacitance of the photo detector (PD) and that of the bonding pad make the input node a dominant pole location. where wun,ty is the unity gain frequency of the amplifier. From A single-stage TIA has sufficient phase margin and ro(4), it is clear that a non-ideal integrator attenuates the input bustness to substrate coupling noise [ I ] but the bandwidth signal and the degree of attenuation is determined by the 3- is usually smaller than a two stage design. However. a twodb pole location p. Also from (4). the propagation speed of stage design has several drawbacks. Addition of the second the wave is determined by the unity gain frequency wun,ty. stage adds an additional pole and reduces the phase margin. Also it is hard to increase the open-loop gain because of the Equations (3),(4) describe an active transmission line. However, in order to implement (3), we discretize the limited voltage headroom. Capacitor peaking 121 can increase derivative. Considering stability, we set = where the bandwidth but stability becomes a problem. e 0-7803-776 I-31031S17.0002003 IEEE 1-253 vo (h) (a) Fig. I . A transimpedance ampliBcr:(a) a conventional TIA design. and (h) an kquivalcnt representation. In a conventional TIA in Fig. I(a), the dominant pole .is located at the input node. Assuming that the g a i n b f the amplifier is finite and the bandwidth is infinite, the equivalent amplifier including the input node capacitance is.a single pole amplifier. As a single pole amplifier can be regarded as a leaky integrator, the overall system satisfies V," ~R, -1 leaky v, - ZTI (IO) described as following lim ( At-n & ( V ( x , t+ %) + V ( x+ A x , t + 9)) 2At V ( x , t ) +V ( z + A x , t ) +P 2 6,(V(x+%,t)+V(z+%,t+At)) +a )=O, ' 2Ax (16) where & V ( x ,t ) and 6,V(x,t) are central differences defined as: V,,,dt = V,. (11) By substituting Vtdea1=-i~Rf and from (IO) and .(11), we have 6,V(z,t) = ' V ( z+ -1A z , t ) - V ( Z- s1A z , t ) , 2 b,V(x,t) = V ( x , t + -1A t ) V ( x ; t- -At). 1 (17) (18) 2 2 Equation (16) can be simplified by noting V ( x , t )= V,deol, and V ( z + A x ,t ) = V o ( t ) where &deal is the objective function that the output voltage V, should follow. The system corresponding to (12) is shown in Fig. l(b). As shown in introduction, we can regard V,, and V, as two nodes in discrete space. Thus, we can rewrite (12) as following, assuming the leaky integrator has a gain A and a 3-dB pole p . The box TIA maintains symmetry of averaged differences. The truncation error Tho, due to the discretized spatial domain can t ) and which be found by using Taylor expansion at V ( x + is . . where V,,, and V,,,,, are the third and fifth order spatial derivatives of V , respectively. The box TIA has a third order accuracy regarding spatial discretization, whereas a conventional single stage TIA has a second order accuracy. Similarly, the gain factor Gbor for the box TIA is + 6 where V ( s , t ) = I&,,l(t), V ( z A z , t ) = V,(t), is a unity gain bandwidth Ap, and A,V(x,t) and A , V ( z , t ) are forward differences shown below: A,V(z,t) = V ( x + A x , t ) - V ( x , t ) , A,V(x,t ) = V ( z ,t At) - V ( x ,t ) . + (14) (15) - Equation (13) is an active transmission line equation with a zero order dispersion term when Ax 0 (shown in (3)) and it represents a conventional TIA. We propose a new TIA circuit called a box TIA, which is 1-254 %, = ( A - l ) p - jw ( A + i ) p + jw Substituting (10) in (19) and we get V, = -2Jleaky (V, + iTRf)dt+ i ~ R f = -!le,,, (Vo + iTRl)dt + %, (22) where the integrator is a single-pole amplifier. Figure 2(a) shows the block diagram of the box TIA. (b) (a) Fig. 2 The proposed box TIA: (a) direcl implementalian. and (b) a modified slmcture wiIh lefl half plane zem. However, this scheme generates a closed loop.~right half plane zero and thus the system has nonminimum phase. The location of open loop zero and the gain of compensation amplifier is adjusted to create a closed loop left half plane zero and to compensate for the dominant pole. In this design, the dominant pole is compensated by using multiple signal path instead of using cascaded stages 111. Therefore, the compensation amplifier can be included in the closed loop resulting in improved linearity. Figure 2(b) shows the modified block diagram of the box TIA with a left half plane zero zip. The transfer function of modified box TIA is I A1 YOU, Vou1.b Fig. 3. TIA implemcnlatian using CMOS PCDCCSI compensation amplifier cancels the dominant pole created by the main amplifier. Figure 4 demonstrates pole, zero locations of the compensated TIA. ziP(B+ 1) As the compensation is made using multiple signal path, (24) =p. B the stabilitv of the overall TIA is determined bv the main feedback amplifier, which is stable due to single stage design, 111. CIRCUIT IMPLEMENTATION and the frequency response is determined by the poles induced Figure shows lhe design using a by the wide band compensation amplifier. Compared to two Process. A wide bandwidth left Plane zero is imp1emented .stare . . ~denions -~ ... 121. . ~, the , rDronosed ~ ~ scheme r ~~.~ has relaxed stabilitv ~, using a simple common source amplifier with an active issues and can operate with a lower supply voltage. Also, inductor 131. The location of the zero zip is bv achievinec a laree transconductance in M, and Mh. .. the substrate coupling noise can be reduced [I]. By using this (25) zip = C,,,iR compensation scheme, the product of transimpedance and and that of the dominant pole p , , , ~ is bandwidth of TIA is increased by more than 50% compared to that of a single stage TIA. AB+A+l The gain of compensation amplifier and the location of open loop zero should satisfy ~~~~ ~~ ~~ ~~~~ I Pred = ~~~ I (26) Rf(C+ Cbfa + CMb)' A. Noise Analysis where A is the gain of the main amplifier and B is the gain of compensation amplifier, CSa,zis the gate-source capacitance of At,, and CA,, and CA,,, are the total input capacitance of Af,, and M b , respectively. In reality, the main feedback loop creates two real poles and the compensation amplifier generates one real left half plane cero and two high frequency left half plane complex poles. The zero introduced by the 1-255 The equivalent input Fig. 3 is: current of the proposed TIA in +u2(Cgs.Ma i:, + c g s , M b + Cdl2 91.,*,b (i2,Ma + ';,MI)= X B)2g:,Mb + 'Z:,Mb (27) -: IV. SIMULATION RESULT Figure 5 shows that the TIA bandwidth with a 1pF input capacitor is 1.32GHr with the transimpedance gain of 58dB at room temperiture. The transimpedance bandwidth product is increased more than 61.5 % compared to a single stage TIA. ~.~~~~... ~~~~ -c- Fig. 4. Pole. zero location of TIA ::a.. ~ *..~.~~ t .E where c d is the capacitance of the photo-detector, - B is the DC gain of compensation amplifier, if is the feedback resistor noise current. i d , M b , i d , M o and are the noise currents of transistors Mb, M a and M1, respectively, C g s , and ~ aC g s , M b are the gate-source capacitances of transistors M a and Mb. respectively, and g m , M . and g m , M b are the transconductances of transistors M a and Mb, respectively. By noting that B sz the equivalent noise conductance is 9-.U1 c e 101 l0M l00M 1G Frequeory(Hz) . 10G Fig. 5. Simulated transimpedance of the,complete front-end with I p F input capacitor 3 The simulated performance of the proposed TIA is summarized in Table 1. ' W gm = ~LnCoxyA = +WL, Bandwidth Power dissipation Power supply Input noise currenl (30) where A = Vg, - Vt and substituting cg,,Mab = . TABLE1 SIMULATION SUMMARY vv 58 d 1.32 GHz(1 pF capacimce) (29) 2 cg, . input -P 2.5V maximum input a m n t . Full scale output ac,,,~.. 0.7~A 0.58mA 0 . 5 V peak-to-peak V. CONCLUSION By taking the partial derivative of (31) with respect to C g o , ~we a . can show that the noise conductance is minimum when The minimum equivalent noise conductance is therefore given by m. P- (J'+J We analyzed the TIA as an active transmission line. The reduction of truncation error caused by the discretization of the spatial domain was design goal. As a result, TIA with multiple signal path has been created. The right half plane zero generated as a result was converted to left half plane zero to prevent having a nonminimum phase, Accordingly, the compensated TIA achieves 58dB gain and 1.32GHz bandwidth with 1pF input node capacitance using 0.25 pm standard CMOS process. REFERENCES [I]A. Tanabe, M. Soda, Y. Nakahwa. T, Tamura. K.Yoshida. A. Furukawa, "A single-chip 2.4-Gbls CMOS aprical receiver IC with low substrate cross-talk preamplific?. lEEE b u r w l of Solid-State Circuirs. vol. 33, no. 12. pp. 2148 -2153. Dec. 1998. [2l C. Kuo. C. Hsiao. S Yang. Y,Chan. "2 Gbit/s transimpedance amplifier -:- and the noise is minimum with 01 = As B 1, we set (L to be close to unity in our design. The simulated input referred noise current for the proposed TIA is approximately 0.7pA,,,,, which is well within the specifications. 1-256 fabricated by 0.35 p m CMOS rcchnologies". Elrcrmnir I r r r m vul. 37. no. 19. Sept. 2001. [31 E. Sackinger el. al.. "A 3GHz. 3 2 d B CMOS limiting amplifier far SONET OC-48 receivers". ISSCC Digest ,if k h n i c u l Papers, pp. 158159. Feb. ZMQ