A high gain wide dynamic range transimpedance amplifier for

advertisement

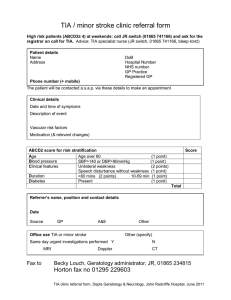

Vol. 35, No. 1 Journal of Semiconductors January 2014 A high gain wide dynamic range transimpedance amplifier for optical receivers Liu Lianxi(刘帘曦)1; 2; , Zou Jiao(邹姣)1 , En Yunfei(恩云飞)3 , Liu Shubin(刘术彬)1 , Niu Yue(牛越)1 , Zhu Zhangming(朱樟明)1; 2 , and Yang Yintang(杨银堂)1; 2 1 School of Microelectronics, Xidian University, Xi’an 710071, China Laboratory of Wide Band-Gap Semiconductor Materials and Devices, Xi’an 710071, China 3 National Key Laboratory of Science and Technology on Reliability Physics and Application Technology of Electrical Component, Guangzhou 510610, China 2 Key Abstract: As the front-end preamplifiers in optical receivers, transimpedance amplifiers (TIAs) are commonly required to have a high gain and low input noise to amplify the weak and susceptible input signal. At the same time, the TIAs should possess a wide dynamic range (DR) to prevent the circuit from becoming saturated by high input currents. Based on the above, this paper presents a CMOS transimpedance amplifier with high gain and a wide DR for 2.5 Gbit/s communications. The TIA proposed consists of a three-stage cascade pull push inverter, an automatic gain control circuit, and a shunt transistor controlled by the resistive divider. The inductive-series peaking technique is used to further extend the bandwidth. The TIA proposed displays a maximum transimpedance gain of 88.3 dB with the –3 dB bandwidth of 1.8 GHz, p exhibits an input current dynamic range from 100 nA to 10 mA. The output voltage noise is less than 48.23 nV/ Hz within the –3 dB bandwidth. The circuit is fabricated using an SMIC 0.18 m 1P6M RFCMOS process and dissipates a dc power of 9.4 mW with 1.8 V supply voltage. Key words: transimpedance amplifier; high gain; inductive-series peaking; wide dynamic range DOI: 10.1088/1674-4926/35/1/015001 EEACC: 2570 1. Introduction In optical fiber communication systems, the transimpedance amplifier (TIA) is the most favorable and efficient choice for the front-end preamplifier, which is a critical element in optical receivers and affects the whole system in terms of speed, sensitivity, and signal-to-noise ratio. The TIA does not suffer from the dynamic range problem related to the high-impedance design, and furthermore it provides a good trade-off between the wide bandwidth of the low-impedance design and the low noise performance of the high-impedance designŒ1 . In the design of a TIA, some of the most important requirements on the TIA are the transimpedance gain, –3 dB bandwidth, dynamic range (DR), sensitivity, and linearity. DR is defined as the ratio of maximum-to-minimum input photocurrent that can still be sensed by the optical receiverŒ2 . Due to the differences of the transmitting current and the fiber length, the transimpedance amplifier should have a wide DR. To achieve a wide –3 dB bandwidth, which has a significant impact on the speed of TIA, an inductive-series peaking technique will be employed. The sensitivity is defined as the acceptable mean minimum optical power at the specified bit error ratio (BER). The sensitivity S can be expressed as: SD p Q Iin ; R0 (1) where Q is the noise distance determined by the signal current and input noise current. For a typical value BER of 10 9 in practice, the value of Q is equal to 6. Iin is the total input noise current. R0 is the responsivity of the photodetector. For a highspeed photodetector, the responsivity is very small (typically 0.04 A/W), which requires more a stringent noise performance to obtain high sensitivityŒ3 . The linearity can express the nonlinearity distortion level of the circuit, of which the value determines the maximum power of the input signal the circuit can tolerate. So the lower and upper bound of DR can also suggest the sensitivity and the linearity respectively to an extent. However the improvements of these demands may be contradictory. Therefore, a trade-off among them should be taken into accountŒ4 . Recently, a number of advanced circuit structures of TIAs have been reported. The work on the TIA presents two trends: one is resolving the bottleneck of the bandwidth, and the other is optimizing the sensitivity and DRŒ5 . In this design, an AGC circuit is used to achieve a wide DR. Besides, a shunt transistor is also employed to further enlarge the DR. Receiving a high-power optical signal using a linear TIA is generally very difficult. In order to obtain a wide DR, the full input photocurrent range is commonly divided into two regions: inactive and activeŒ6 . Moreover, the 2-stage compression concept has been describedŒ7 . On the basis of this concept, the full input current range is separated into three regions in this design (inactive, one-active and both-active), thus further broadening the DR and increasing the input current overdrive * Project supported by the National Natural Science Foundation of China (Nos. 61376033, 61006028), the National High-Tech Program of China (Nos. 2012AA012302, 2013AA014103), and the Opening Project of Science and Technology on Reliability Physics and Application Technology of Electronic Component Laboratory. † Corresponding author. Email: lxliu@mail.xidian.edu.cn; adam79416@126.com Received 20 May 2013, revised manuscript received 12 July 2013 © 2014 Chinese Institute of Electronics 015001-1 J. Semicond. 2014, 35(1) Liu Lianxi et al. Fig. 1. (a) A single stage of the push–pull inverter. (b) The equivalent small signal model. AV is the open-loop gain of the push–pull inverter, which is given by capability. 2. Analysis of basic structure For the sake of analysis, a single stage CMOS implementation of a push pull inverter is depicted in Fig. 1(a). The push pull inverter can realize current reuse thus achieving a high enough gain. By setting parameters reasonably, the PMOS transistor M1 and the NMOS transistor M2 are biased in their saturation region to maximize the transconductance and increase the gain bandwidth product of the entire structureŒ8 . The voltage drop of the feedback resistor RF can provide the bias voltage for M1 and M2 transistors without an additional bias source and regulate the input matching. The transistor M3 serves as an active load so that the amplifier transistors M1 and M2 can enlarge their sizes to avoid overshoot. Moreover, it can also increase the bandwidth and minimize the Miller effect. Figure 1(b) shows the equivalent small signal model. The current source Iin and Cp are the equivalent model of the photodiode. Cp represents its parasitic capacitance. Cgs1 , Cgs2 , Cgd1 , and Cgd2 stand for the gate–source and gate–drain parasitic capacitances of the transistors M1 and M2, respectively. The parameters gm1 and gm2 are the transconductances of the transistors M1 and M2, respectively. RL acts as the load resistance and it can be expressed as Eq. (1). 1 RL D RO k k Rin ; gm3 (2) where RO represents the output resistances of the transistors M1 and M2. 1/gm3 is the resistance of the active load transistor M3 and Rin is the input resistance of the push pull inverter, which can be expressed asŒ9 : Rin D Rinop Rin .AV D 0/ RNP k .RF C RO / D D ; AV AV AV (3) where Rinop is the open-loop input resistance of the push pull inverter and RNF represents the input resistances of the transistors M1 and M2. Normally, RNF is much larger than RF and RO is less than RF , so the input resistance Rin can be approximately expressed as: Rin RF : AV (4) Vout D .gm1 C gm2 / RL : Vin AV D (5) As all of the input current will flow through the feedback resistance RF , therefore, the output voltage is equal to Iin RF , and then the transimpedance gain is given byŒ9 AR D Vout Iin RF D D RF : Iin Iin (6) The cut-off frequency at –3 dB is calculated byŒ10 f 3dB D 1 C AV ; 2RF CT (7) where CT involves the input capacitance of the push–pull inverter and the parasitic capacitance of photodetector CP . The equivalent noise power at the input node is given by 2 inoise D 2qIdark B C C 8kT 3gm 4kT B C 2qIG B RF B 2 3 .2 C / C B ; T 2 Rin (8) where q is the electron charge, k is Boltzmann’s constant, T is the absolute temperature, Idark is the dark current of the photo detector, IG is the gate current, and B indicates the useful bandwidth. The second term and the fourth term on the right of the equation are the thermal noises of the feedback resistance RF and the input transistors M1 and M2, respectively. 3. The proposed TIA circuit The TIA is generally required to convert a small current signal to a large enough voltage signal. The push pull inverter is used in the design to realize a high gain. The PMOS and NMOS transistors in the push pull inverter can be both biased in the saturation region to maximize the transconductance. On the basis of the 2-stage compression concept, an AGC circuit and a shunt transistor are employed respectively to achieve 1-stage compression and 2-stage compression thus obtaining a wide DR. In order to extend the bandwidth further, the inductive-series peaking technique is used in this design. 015001-2 J. Semicond. 2014, 35(1) Liu Lianxi et al. Fig. 2. The improved complete TIA circuit. The improved whole transimpedance amplifier circuit is shown in Fig. 2. The proposed TIA consists of a high gain stage, an automatic gain control circuit, and a shunt transistor controlled by the resistive divider. The high gain stage comprises a three cascaded push-pull inverter (M1–M9) to achieve the gain in demand. To further extend the bandwidth of the TIA, the inductor L is inserted between the first push-pull inverter and a second one separates the gate capacitances of transistors M3, M4 and M5 from the parasitic capacitance of the first stage. Compared with the active inductorŒ11 , which normally consists of a MOS transistor and a resistor, the off-chip spiral inductor L used in this design can provide a higher inductance value in low-voltage high-speed circuits. To maintain the feedback resistor in the required range, an automatic gain control loop was implemented to guarantee the maximum sensitivity at the minimum optical power and provide linearity for the high optical power. In order to reduce the complexity and power consumption to a great extent, the proposed AGC circuit only includes the resistance R3 and transistor M10 to adjust the transimpedance gain. The resistance value of the transistor M10 will vary with the different control voltage. Transistor M11 acts as a shunt transistor and forms a parallel current path. When transistor M11 is on, part of photocurrent will flow into ground through M11 thus further enhancing the input DR. The resistances R1 and R2 are regarded as resistive divider (RD). The resistive divider (RD) generating Vgate allows not only a reduction in chip area and power consumption of the TIA circuit, but also a further extension of the DR. The control voltage of the shunt transistor is normally produced using two traditional methods. One is to generate it by the bias circuit or control logic, but this increases the cost, the power consumption, and the chip area. The other is to provide the control voltage by the output of the TIA. Once the output reaches the threshold voltage of M11, the shunt transistor will work. However, the photocurrent at that point may be small, and so the current flowing through the shunt transistor into the amplifier will be smaller and may not be converted to a high enough voltage. The problem can be avoided through using the resistive divider presented in this paper to obtain a wider DR so long as the resistance value of R1 is set much larger than that of R2 . The voltage drop of R2 cannot reach the threshold voltage of M11 until the output voltage Vout of the TIA is high enough, which Fig. 3. (a) The transimpedance gain versus frequency response of the TIA. (b) DC-transfer characteristic of the TIA. is derived from a large input current. The relation of Vgate with Vout can be described as: Vgate R2 D : Vout R1 (9) The full input current range is divided into three regions, which includes inactive, one-active, and both-active. In the inactive region, the input current is very small and transistors M10 and M11 are turned off; the transimpedance gain is approximated to RF . The TIA responds linearly to the input current. In the one-active region where the input current has a medium value, transistor M10 starts to be turned on while M11 is still off, the transimpedance gain is reduced and approximated to RF //R3 . While in the both-active region, the input current is large enough, so both transistors M10 and M11 must be turned on, and the transimpedance gain is reduced more seriously, which cannot be calculated simply. In order to optimize frequency and noise response, the lengths of all MOS transistors are set at the smallest size the process conditions permit. The push–pull inverter of the first stage is tuned as large as possible to reduce the relative noise contribution. 4. Simulation results To verify the proposed TIA circuit, Candence-Spectre simulations are performed using SMIC 0.18 m 1P6M RFCMOS technology. Figure 3(a) shows the transimpedance gain versus frequency response of the TIA. The dashed line depicts the tran- 015001-3 J. Semicond. 2014, 35(1) Liu Lianxi et al. Fig. 4. (a) The transient response for the output voltage versus input current at different process corners. (b) The output noise of the TIA. Fig. 5. The histograms of the output voltage signal when (a) Iin D 100 nA, (b) Iin D 1 A, (c) Iin D 1 mA, (d) Iin D 10 mA. simpedance gain of the TIA without the inductor and the solid line with the inductor. For the simulation result of the AC analysis, two lines coincide with each other at low frequency and the maximum transimpedance gains are both 88.3 dB. Without the inductor, the –3 dB bandwidth is about 1 GHz. After the inductor is inserted, the –3 dB bandwidth can be enhanced up to 1.8 GHz. When the loop gain equals 1, the gain crossover point is about at the –3 dB bandwidth frequency point on the wave of closed-loop gain namely the transimpedance gain. So for the TIA circuit, the phase margin is about 50. The DC-transfer characteristic of the TIA is depicted in Fig. 3(b). The input current is logarithmically swept from 100 nA to 10 mA. As mentioned in Section 3, the full range is divided into three regions. The inactive region is from 100 nA (node n0) to 0.32 mA (node n1) in which the output voltage increases with the input current. And the one-active region varies from 0.32 mA (node n1) to 0.8 mA (node n2) where the output voltage begins to reduce as a result of an attenuated transimpedance gain. The range from 0.8 mA (node n2) to 10 mA (node n3) belongs to the both-active region and the output voltage continues to decrease. Moreover, the output voltage does not exceed 1.8 V within the input current dynamic range. The transient response is shown in Fig. 4(a) for the output voltage versus input current at different process corners. 015001-4 J. Semicond. 2014, 35(1) Reference Ref. [4] Ref. [12] Ref. [13] MG2252Œ14 MAX3275Œ15 Table 1. Performance summary of the proposed TIA: comparison with other works. Process Supply (V) Gain (dB/ BW (GHz) DR (dB) Power (mW) 90 nm 1 85.8 1.4 55 4.3 RFCMOS (1.77 A–1 mA) 0.13 m N/A 82.3 1.8 52 118 RFCMOS (5 A–2 mA) 1.1 68 0.28 85.2 8.7 40 nm RFCMOS (220 nA–4 mA) 92.4 RFCMOS 3.3 80 1.8 46 (10 A–2 mA) SiGe Bipolar ONET4291TAŒ16 N/A This work Liu Lianxi et al. 0.18 m RFCMOS 3.3 70.4 2.3 32 (50 A–2 mA) 82.5 3.3 70.1 2.8 56 1.8 88.3 1.8 32 (50 A–2 mA) 100 (100 nA–0 mA) The input current pulse is the same, of which the pulse-width is 400 ps with a rise/fall time of 10 ps and the peak-to-peak current is 10 mA. The simulation result exhibits that the TIA can respond normally to a fast and large input current. In addition, the output swing shows little change at different process corners. The output noise of the overall circuit is depicted in Fig. 4(b). As shown in Fig. 4(b), p the maximum output voltage noise is less than 48.23 nV/ Hz from 10 MHz to 1.8 GHz. According to the conversion relations of the input equivalent current noise and the output p noise, the equivalent input current noise is about 1.86 pA/ Hz within the bandwidth. In Eq. (1), the noise distance Q equals 6 for BER of 10 9 and the responsivity R0 is a typical value of 0.04 A/W, the sensitivity S is equal to –27.7 dBm byp calculation for the equivalent input current noise of 1.86 pA/ Hz. The simulation results verify the efficiency and advantages of the design. To estimate the effect of the process and mismatch on the proposed TIA, a Monte Carlo simulation for the whole circuit is conducted. The result of a 200-run Monte Carlo simulation for the designed TIA is shown in Fig. 5, which is based on a cumulative normal probability distribution. Figures 5(a)–5(d) depict the histograms of the output voltage signal when the input current signal Iin is equal to 100 nA, 1 A, 1 mA, and 10 mA, respectively, where N is the number of Monte Carlo iterations, Videal is the ideal output voltage without considering the process or mismatch, sd is the standard deviation, and mu is the mean value. As one can see, the process and mismatch have little effect on the response of the output voltage signal with the input current signal. The main performance of this proposed TIA is summarized and compared with some similar works presented in other references in Table 1. The transimpedance gain of this design is higher than that of the other related works, as shown in Table 1. This effect mainly results from that the push pull inverter is used in the design because the PMOS and NMOS transistors can be both biased in their saturation region to maximize the transconductance. Due to the use of the AGC circuit and 9.4 Noise RMS output noise 2.47 mV Input referred noise p 0.8 pA/ Hz RMS input noise 220 nA RMS input referred noise 200 nA RMS input referred noise 300 nA Input referred noise p 8.8 pA/ Hz RMS output p noise: 48.23 nV/ Hz Input referred p noise: 1.86 pA/ Hz the shunt transistor controlled by the resistive divider, the dynamic range of this TIA is the widest. Moreover, the power consumption of the TIA is relatively low thanks to the simple structure of elements such as the AGC circuit. The proposed AGC circuit only includes a resistance and a transistor to adjust the transimpedance gain, thus reducing the complexity and power consumption to a great extent. Therefore, this TIA design is very applicable for optical receivers. 5. Conclusion A 0.18 m RFCMOS high performance transimpedance amplifier had been presented in this work. It is designed for an external photodiode which is modeled by a capacitance of 1 pF. The TIA can tolerate an input dynamic range of 100 dB (100 nA–10 mA) thanks to the shunt transistor controlled by the resistive divider. The proposed TIA displays a higher transimpedance gain of 88.3 dB with –3 dB bandwidth of 1.8 GHz due to the inductive-series peaking p technique. The maximum output noise is less than 48.23 nV/ Hz within the – 3 dB bandwidth, and the equivalent input current noise is about p 1.86 pA/ Hz. The low noise can be used to detect a small current at the input. The total power consumption is 9.4 mW with a 1.8 V supply voltage. So the TIA proposed is perfectly suitable for 2.5 Gbit/s optical fiber communication systems. References [1] Kamrani E, Sawan M. Fully integrated CMOS avalanche photodiode and distributed-gain TIA for CW-fNIRS. IEEE Biomedical Circuits and Systems Conference, San Francisco, CA, 2011: 317 [2] Micusik D, Zimmermann H. A 240 MHz-BW 112 dB-DR TIA. IEEE International Solid-State Circuits Conference, San Francisco, CA, 2007: 554 [3] Huang Beiju, Zhang Xu, Chen Hongda. 1-Gb/s zero-pole cancellation CMOS transimpedance amplifier for Gigabit Ethernet applications. Journal of Semiconductors, 2009, 30(10): 105005 [4] Tian Jun, Wang Zhigong, Liang Bangli, et al. A CMOS 1.4 THz 155 Mb/s differential transimpedance preamplifier for optical receiver. Chinese Journal of Semiconductors, 2004, 25(11): 1486 015001-5 J. Semicond. 2014, 35(1) Liu Lianxi et al. [5] Xu Hui, Feng Jun, Liu Quan, et al. A 3.125-Gb/s inductorless transimpedance amplifier for optical communication in 0.35 m CMOS. Journal of Semiconductors, 2011, 32(10): 105003 [6] Aznar F, Celma S, Calvo B, et al. A 0.18 m CMOS integrated transimpedance amplifier-equalizer for 2.5 Gb/s. 53rd IEEE International Midwest Symposium on Circuits and Systems, Seattle, WA, 2010, 40: 604 [7] Micusik D, Zimmermann H. 130 dB-DR transimpedance amplifier with monotonic logarithmic compression and high-current monitor. IEEE International Solid-State Circuits Conference, San Francisco, CA, 2008: 78 [8] Guermaz M B, Bouzerara L, Escid H, et al. Low-noise and highbandwidth 0.8 m CMOS transimpedance amplifier for optical receiver circuit. Journal of Circuits, Systems, and Computers, 2005, 14(2): 267 [9] Sansen W M C. Analog design essentials. The International Series in Engineering and Computer Science, 2006, 859: 391 [10] Hammoudi E, Mokhtar A. 2.75 GHz low noise 0.35 m CMOS transimpedance amplifier. 18th Mediterranean Conference on Control & Automation, Marrakech, Morocco, 2010: 928 [11] Xue Zhaofeng, Li Zhiqun, Wang Zhigong, et al. A low noise 1.25Gb/s front-end amplifier for optical receivers. Chinese Journal of Semiconductors, 2006, 27(8): 1373 [12] Yu G, Zou X, Zhang L, et al. A low-noise high-gain transimpedance amplifier with high dynamic range in 0.13 m CMOS. IEEE International Symposium on Radio-Frequency Integration Technology, Singapore, Singapore, 2012: 37 [13] Hassan M, Zimmermann H. An 85 dB dynamic range transimpedance amplifier in 40 nm CMOS technology. IEEE NORCHIP, Lund, 2011: 1 [14] http://www.mignal.com/word/DS_MG2252.pdf [15] http://china.maximintegrated.com/datasheet/index.mvp/id/3187/ t/al [16] http://www.ti.com/lit/ds/symlink/onet4291ta.pdf 015001-6