TELEDYNE RELAYS

SERIES

421

ESTABLISHED RELIABILITY

TO-5 RELAYS

SPDT MAGNETIC LATCHING

SERIES

DESIGNATION

RELAY TYPE

421

SPDT basic relay

421D

SPDT relay with internal diode for coil transient suppression

421DD

SPDT relay with internal diodes for coil transient suppression and

polarity reversal protection

DESCRIPTION

The 421D and 421DD Series utilizes internal discrete silicon diodes for

coil suppression and polarity reversal protection.

The TO-5 relay, originally conceived and developed by Teledyne, has

become one of the industry standards for low level switching from dry

circuit to 0.5 ampere. Designed expressly for high density PC Board

mounting, its small size and low coil power dissipation make the TO-5

relay one of the most versatile ultraminiature relays available.

By virtue of its inherently low intercontact capacitance and contact circuit

losses, the TO-5 relay has shown itself to be an excellent ultraminiature

RF switch for frequency ranges well into the UHF spectrum. A typical

RF application for the TO-5 relay is in hand held radio transceivers,

wherein the combined features of good RF performance, small size,

low coil power dissipation and high reliability make it a preferred

method of Transmitter-Receive switching (see Figure 1).

The following unique construction features and manufacturing techniques

provide excellent resistance to environmental extremes and overall

high reliability:

• All welded construction.

• Unique uni-frame design providing high magnetic efficiency and

mechanical rigidity.

• High force/mass ratios for resistance to shock and vibration.

• Advanced cleaning techniques provide maximum assurance of

internal cleanliness.

• Precious metal alloy contact material with gold plating assures

excellent high current and dry circuit switching capabilities.

The 421 Series magnetic latching relays are ideally suited for applications

where power dissipation must be minimized. The relays can be operated

with a short duration pulse. After contacts have transferred, no external

holding power is required.

The magnetic latching feature of the 421 Series provides a “memory”

capability, since the relays will not reset upon removal of power.

PRINCIPLE OF OPERATION

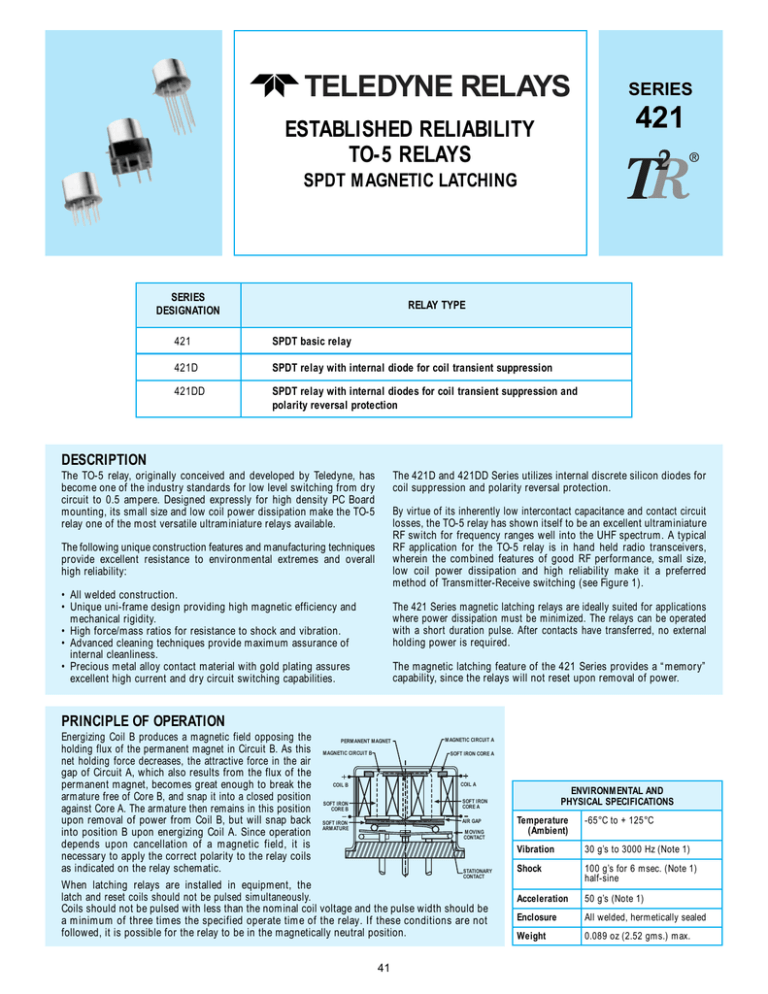

Energizing Coil B produces a magnetic field opposing the

MAGNETIC CIRCUIT A

PERMANENT MAGNET

holding flux of the permanent magnet in Circuit B. As this MAGNETIC CIRCUIT B

SOFT IRON CORE A

net holding force decreases, the attractive force in the air

gap of Circuit A, which also results from the flux of the

COIL A

COIL B

permanent magnet, becomes great enough to break the

armature free of Core B, and snap it into a closed position SOFT IRON

SOFT IRON

CORE A

CORE B

against Core A. The armature then remains in this position

AIR GAP

upon removal of power from Coil B, but will snap back SOFT IRON

MOVING

into position B upon energizing Coil A. Since operation ARMATURE

CONTACT

depends upon cancellation of a magnetic field, it is

necessary to apply the correct polarity to the relay coils

as indicated on the relay schematic.

STATIONARY

CONTACT

When latching relays are installed in equipment, the

latch and reset coils should not be pulsed simultaneously.

Coils should not be pulsed with less than the nominal coil voltage and the pulse width should be

a minimum of three times the specified operate time of the relay. If these conditions are not

followed, it is possible for the relay to be in the magnetically neutral position.

41

ENVIRONMENTAL AND

PHYSICAL SPECIFICATIONS

Temperature

(Ambient)

-65°C to + 125°C

Vibration

30 g’s to 3000 Hz (Note 1)

Shock

100 g’s for 6 msec. (Note 1)

half-sine

Acceleration

50 g’s (Note 1)

Enclosure

All welded, hermetically sealed

Weight

0.089 oz (2.52 gms.) max.

SERIES 421

GENERAL ELECTRICAL SPECIFICATIONS

(-65°C to +125°C unless otherwise noted) (Notes 2 & 7)

Contact Arrangement

Rated Duty

Contact Resistance

Contact Load Rating (DC)

(See Fig. 2 for other DC

resistive voltage/current ratings)

1 Form C (SPDT)

Continuous

0.125 ohm max. before life; 0.225 ohm max. after life at 0.5A/28VDC, (measured 1/8” from header)

Resistive:

0.5 Amp/28VDC

Inductive:

200 mA/28VDC (320 mH)

Lamp:

100 mA/28VDC

Low Level: 10 to 50 µA/10 to 50 mV

Resistive:

250 mA/115VAC, 60 and 400Hz (Case not grounded)

100 mA/115VAC, 60 and 400Hz (Case grounded)

10,000,000 cycles (typical) at low level

00,100,000 cycles min. at all other loads specified above

2A/28VDC Resistive (100 cycles min.)

Contact factory

290 milliwatts typical at nominal rated voltage @ 25°C

1.5 msec max. at nominal rated coil voltage

1.5 msec max.

4.5 msec @ nominal voltage

0.4 pf typical

10,000 megohms min. between mutually isolated terminals

Atmospheric pressure: 500 VRMS/60 Hz

70,000 ft.: 125 VRMS/60Hz

Contact Load Ratings (AC)

Contact Life Ratings

Contact Overload Rating

Contact Carry Rating

Coil Operating Power

Operate Time

Contact Bounce

Minimum Operate Pulse

lntercontact Capacitance

Insulation Resistance

Dielectric Strength

Diode P.I.V.

421D, 421DD

Negative Coil Transient

421D, 421DD

100 VDC min.

1.0 VDC max.

DETAILED ELECTRICAL SPECIFICATIONS

(-65°C to +125°C unless otherwise noted) (Note 7)

BASE PART

NUMBERS

(See Note 9 for full P/N Example

Coil Voltage (VDC)

421-5

421D-5

421DD-5

➧

Nom.

Max.

421, 421D

421DD (Note 3)

Min.

Max.

421

421D

421DD

Coil Resistance

(Ohms ± 10% @ 25°C)

Coil Current (mADC @ 25°C)

421DD Series only

Set & Reset Voltage (VDC, Max.)

5.0

6.0

61

48

78.0

111.8

3.5

3.7

4.5

421-6

421D-6

421DD-6

421-9

421D-9

421DD-9

421-12

421D-12

421DD-12

421-18

421D-18

421DD-18

421-26

421D-26

421DD-26

6.0

8.0

120

97

45.8

63.0

4.5

4.5

5.5

9.0

12.0

280

280

25.7

34.9

6.8

6.8

7.8

12.0

16.0

500

500

19.6

26.7

9.0

9.0

10.0

18.0

24.0

1130

1130

13.4

18.8

13.5

13.5

14.5

26.5

32.0

2000

2000

11.2

15.2

18.0

18.0

19.0

PERFORMANCE CURVES

(NOTE 2)

TYPICAL RF PERFORMANCE

TYPICAL DC CONTACT RATING (RESISTIVE)

0

.1

300

INSER

TION

.3

LOSS

LOAD VOLTAGE (VDC)

.2

10

1.92

20

N LOSS

RETUR

30

1.22

SWR)

(V

1.07

40

50

60

1.02

TACTS

S CON

CROS

NA

OLATIO

1.01

VSWR

dB

.4

70

200

150

100

50

1.00

IS

250

1.00

.01

0.5

.1

.5

1.0

0

0.1

0.2

0.3

0.4

0.5

0.6

FREQUENCY (GHz)

LOAD CURRENT (AMPS DC)

FIGURE 1

FIGURE 2

42

0.7

0.8

0.9

1.0

SERIES 421

OUTLINE DIMENSIONS

TERMINAL LOCATIONS AND PIN NUMBERING (REF. ONLY)

(Viewed from Terminals)

SCHEMATIC DIAGRAMS

CASE DETAIL

.370

(9.40)

DIA. MAX.

.031 (.79)

± .003 (0.08)

COIL B

.335

(8.51)

DIA. MAX.

36° ±3° TYP.

9

.035 (.89)

± .010 (0.25)

1

.280 (7.11) MAX.

COIL A

2

8

7

.200 (5.08)

± .010 (.25) DIA.

421

6

4

WIRE LEAD: .75 (19.05) MIN.

PIN: .187 (4.75) ± .010 (.25)

(See Note 5)

COIL B

+.002 (.05)

.017 (.43) –.001 (.03) DIA.

DIMENSIONS ARE SHOWN IN INCHES (MILLIMETERS)

SPACER PAD

SPREADER PAD

Relays can be supplied with a spacer pad attached to the relay

header. The pad permits the relay to be spaced away from the

mounting surface facilitating solder joint inspection. To order add

M4 to the part number (e.g. ER421M4-26A).

Relays can be supplied with spreader pads which are attached

to the relays. Spreader pads can be supplied by adding M to the

part number (e.g. ER421M-26A).

.370 50 MAX

(9.40)

.150

(3.81)

COIL A

421D

COIL B

.100 (2.54)

.100 (2.54)

.300

(7.62)

COIL A

.305 MAX.

(7.75)

.200

(5.08)

(.41) .016

.18 .007

421DD

.398 MAX

(10.11)

NOTES:

NOTES:

SCHEMATICS ARE VIEWED FROM TERMINALS

1. Material: Diallyl Phthalate.

2. Increase contact resistance by 0.025 ohm.

3. Spreader pad conform to MIL-M-38527.

1. Material: Polyester film.

2. Increase contact resistance by 0.01 ohm.

COIL A LAST ENERGIZED

NOTES:

1.

2.

3.

4.

5.

Relay contacts will exhibit no chatter in excess of 10 µsec or transfer in excess of 1 µsec.

“Typical” characteristics are based on available data and are best estimates. No on-going verification tests are performed.

For reference only. Coil resistance not directly measurable at relays terminals due to internal series semiconductor. 421DD only.

Screened HI-REL versions available. Contact factory.

Unless otherwise specified, relays will be supplied as follows: Length will be standard 0.75” (19.05) minimum and will be either

gold plated or solder coated. Contact your local representative for ordering information.

6. The slash and characters appearing after the slash are not marked on the relay.

7. Unless otherwise specified, parameters are initial values.

8.

RELIABILITY LEVEL

FAILURE RATE %/10,000 CYCLES

A

1.5

B

0.75

9.

Teledyne Part Numbering System for Established Reliability Relays (See T2R® Program Introduction)

EXAMPLE:

ER 421 D Z M4 – 26

A / SQ

Established

Reliability Designator

Termination Variant

Q = Solder Coated Leads (Notes 5 and 6)

S = .187” Leads (Notes 5 and 6)

Relay Series

Reliability and Screening Level (Note 8)

D = Diode Suppression

DD = Diode Suppression and Polarity Protection

Coil Voltage

Mounting Variant

Ground Pin (See page 112)

M = Spreader Pad

M4 = Spacer Pad

©1996

TELEDYNE RELAYS

43

12525 Daphne Avenue

Hawthorne, California 90250

TECHNICAL DATA SHEET

6 Lake Street, Lawrence, MA 01841

1-800-446-1158 / (978) 620-2600 / Fax: (978) 689-0803

Website: http://www.microsemi.com

SCHOTTKY BARRIER DIODES

– LEADLESS PACKAGE FOR SURFACE MOUNT

– METALLURGICALLY BONDED

– DOUBLE PLUG CONSTRUCTION

Qualified per MIL-PRF-19500/444

DEVICES

QUALIFIED LEVELS

1N5711UR-1

1N5712UR-1

1N6857UR-1

1N6858UR-1

CDLL2810

CDLL5711

CDLL5712

JAN

JANTX

JANTXV

CDLL6263

CDLL6857

CDLL6858

MAXIMUM RATING AT 25°C

-65°C to +150°C

-65°C to +150°C

5711 & 6263 types

2810, 5712 & 6858 types

6857 type

all types

Operating

Temperature:

Storage Temperature:

Operating Current:

:33mA dc @ TEC = +140°C

:75mA dc @ TEC = +130°C

:150mA dc @ TEC = +110°C

:Derate to 0 (zero) mA dc @ +150°C

Derating:

ELECTRICAL CHARACTERISTICS (TA = 25°C, unless otherwise specified)

MINIMUM

BEAKDOWN

VOLTAAGE

MAXIMUM

FORWARD

VOLTAGE

MAXIMUM

FORWARD

VOLTAGE

MAXIMUM

REVERSE

LEAKAGE

CURRENT

VBR @ 10μA

VF @ 1mA

VF @ I F

I R @ VR

VOLTS

VOLTS

1N5711UR-1

70

1N5712UR-1

20

1N6857UR-1

1N6858UR-1

TYPE

NUMBER

MAXIMUM

CAPACITANCE

@

VR = 0 VOLTS

f = 1.0MHz

CT

ESDS

CLASS

FIGURE 1

nA

VOLTS

PICO FARADS

0.41

VOLTS

@ mA

1.0 @ 15

200

50

2.0

1

0.41

1.0 @ 35

150

16

2.0

1

20

0.35

0.75 @ 35

150

16

4.5

2

70

0.36

0.65 @ 15

200

50

4.5

2

CDLL2810

20

0.41

1.0 @ 35

100

15

2.0

1

CDLL5711

70

0.41

1.0 @ 15

200

50

2.0

1

CDLL5712

20

0.41

1.0 @ 35

150

16

2.0

1

CDLL6263

60

0.41

1.0 @ 15

200

50

2.2

1

CDLL6857

20

0.35

0.75 @ 35

150

16

4.5

2

CDLL6858

70

0.36

0.65 @ 15

200

50

4.5

2

NOTE:

1.

2.

Effective Minority Carrier Lifetime (τ) is 100 Pico Seconds

Qualification testing to J, JX, JV and JS levels for 6857 and 6858 types is underway. Contact the

factory for qualification completion dates. These two part numbers are being introduced by CDI as

“drop-in” replacements for the 5711 and 5712. They provide a more robust mechanical design and a

higher ESDS class with the only trade-off being an increase in capacitance.

T4-LDS-0041 Rev. 1 (100246)

Page 1 of 3

TECHNICAL DATA SHEET

6 Lake Street, Lawrence, MA 01841

1-800-446-1158 / (978) 620-2600 / Fax: (978) 689-0803

Website: http: //www.microsemi.com

GRAPHS

FIGURE 1

FIGURE 2

I – V Curve Showing Typical Forward Voltage Variation with

Temperature for the CDLL2810 and CDLL5712 Schottky

Diodes.

FIGURE 3

I – V Curve Showing Typical Forward Voltage Variation with

Temperature for Schottky Diode CDLL5711.

CDLL2810 and CDLL5712 Typical Variation of Reverse

Current (IR) vs. Reverse Voltage (VR) at Various Temperatures

FIGURE 4

CDLL5711 Typical; Variation of Reverse Current (IR); vs.

ReverseVoltage (VR) at Various Temperatures.

FIGURE 5

Typical Dynamic

Resistance (RD) vs. Forward Current

Current (IF)

T4-LDS-0041 Rev. 1 (100246)

Page 2 of 3

TECHNICAL DATA SHEET

6 Lake Street, Lawrence, MA 01841

1-800-446-1158 / (978) 620-2600 / Fax: (978) 689-0803

Website: http: //www.microsemi.com

PACKAGE DIMENSIONS

NOTE:

1. Dimensions are in inches. Millimeters are given for general

information only.

2. In accordance with ASME Y14.5M, diameters are equivalent to Φx

symbology.

Symbol

BD

BL

ECT

S

Dimensions

Inches

Millimeters

Min

Max

Min

Max

.063

.067

1.60

1.70

.130

.146

3.30

3.71

.016

.022

0.41

0.55

.001 Min

Notes

DESIGN DATA

CASE: DO-213AA, Hermetically sealed glass case. (MELF, SOD-80, LL34)

LEAD FINISH: Tin / Lead

THERMAL RESISTANCE: (RθJEC): 100°C/W maximum at L = 0 inch

THERMAL IMPEDANCE: (ZθJX): 40°C/W maximum.

POLARITY: Cathode end is banded.

MOUNTING POSITION SURFACE SELECTION: The Axial Coefficient of Expansion (COE) of this device is approximately +6PPM/°C.

The COE of the Mounting Surface System should be selected to provide a suitable match with this device.

T4-LDS-0041 Rev. 1 (100246)

Page 3 of 3

a

800 MHz, 50 mW

Current Feedback Amplifier

AD8001

FEATURES

Excellent Video Specifications (RL = 150 , G = +2)

Gain Flatness 0.1 dB to 100 MHz

0.01% Differential Gain Error

0.025 Differential Phase Error

Low Power

5.5 mA Max Power Supply Current (55 mW)

High Speed and Fast Settling

880 MHz, –3 dB Bandwidth (G = +1)

440 MHz, –3 dB Bandwidth (G = +2)

1200 V/s Slew Rate

10 ns Settling Time to 0.1%

Low Distortion

–65 dBc THD, fC = 5 MHz

33 dBm Third Order Intercept, F1 = 10 MHz

–66 dB SFDR, f = 5 MHz

High Output Drive

70 mA Output Current

Drives Up to 4 Back-Terminated Loads (75 Each)

While Maintaining Good Differential Gain/Phase

Performance (0.05%/0.25)

APPLICATIONS

A-to-D Drivers

Video Line Drivers

Professional Cameras

Video Switchers

Special Effects

RF Receivers

FUNCTIONAL BLOCK DIAGRAMS

8-Lead PDIP (N-8),

CERDIP (Q-8) and SOIC (R-8)

NC 1

8

–IN

2

7

V+

+IN 3

6

OUT

5

NC

V– 4

5-Lead SOT-23-5

(RT-5)

AD8001

NC

VOUT 1

AD8001

5

+VS

4

–IN

–VS 2

+IN 3

NC = NO CONNECT

transimpedance linearization circuitry. This allows it to drive

video loads with excellent differential gain and phase performance on only 50 mW of power. The AD8001 is a current

feedback amplifier and features gain flatness of 0.1 dB to 100 MHz

while offering differential gain and phase error of 0.01% and

0.025°. This makes the AD8001 ideal for professional video

electronics such as cameras and video switchers. Additionally,

the AD8001’s low distortion and fast settling make it ideal for

buffer high speed A-to-D converters.

The AD8001 offers low power of 5.5 mA max (VS = ± 5 V) and

can run on a single +12 V power supply, while being capable of

delivering over 70 mA of load current. These features make this

amplifier ideal for portable and battery-powered applications

where size and power are critical.

GENERAL DESCRIPTION

The AD8001 is a low power, high speed amplifier designed

to operate on ± 5 V supplies. The AD8001 features unique

The outstanding bandwidth of 800 MHz along with 1200 V/µs

of slew rate make the AD8001 useful in many general-purpose

high speed applications where dual power supplies of up to ± 6 V

and single supplies from 6 V to 12 V are needed. The AD8001 is

available in the industrial temperature range of –40°C to +85°C.

9

VS = 5V

RFB = 820

6

GAIN – dB

3

G = +2

RL = 100

0

–3

VS = 5V

RFB = 1k

–6

–9

–12

10M

100M

FREQUENCY – Hz

1G

Figure 1. Frequency Response of AD8001

Figure 2. Transient Response of AD8001; 2 V Step, G = +2

REV. D

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© 2003 Analog Devices, Inc. All rights reserved.

AD8001–SPECIFICATIONS (@ T = + 25C, V = 5 V, R = 100 , unless otherwise noted.)

A

Model

DYNAMIC PERFORMANCE

–3 dB Small Signal Bandwidth,

N Package

R Package

RT Package

S

L

AD8001A

Typ

Max

Conditions

Min

Unit

G = +2, < 0.1 dB Peaking, R F = 750 Ω

G = +1, < 1 dB Peaking, RF = 1 kΩ

G = +2, < 0.1 dB Peaking, R F = 681 Ω

G = +1, < 0.1 dB Peaking, R F = 845 Ω

G = +2, < 0.1 dB Peaking, R F = 768 Ω

G = +1, < 0.1 dB Peaking, RF = 1 kΩ

350

650

350

575

300

575

440

880

440

715

380

795

MHz

MHz

MHz

MHz

MHz

MHz

G = +2, R F = 750 Ω

G = +2, R F = 681 Ω

G = +2, R F = 768 Ω

G = +2, VO = 2 V Step

G = –1, VO = 2 V Step

G = –1, VO = 2 V Step

G = +2, VO = 2 V Step, RF = 649 Ω

85

100

120

800

960

110

125

145

1000

1200

10

1.4

MHz

MHz

MHz

V/µs

V/µs

ns

ns

–65

dBc

2.0

2.0

18

0.01

0.025

33

14

–66

nV/√Hz

pA/√Hz

pA/√Hz

%

Degree

dBm

dBm

dB

Bandwidth for 0.1 dB Flatness

N Package

R Package

RT Package

Slew Rate

Settling Time to 0.1%

Rise and Fall Time

NOISE/HARMONIC PERFORMANCE

Total Harmonic Distortion

Input Voltage Noise

Input Current Noise

Differential Gain Error

Differential Phase Error

Third Order Intercept

1 dB Gain Compression

SFDR

fC = 5 MHz, VO = 2 V p-p

G = +2, RL = 100 Ω

f = 10 kHz

f = 10 kHz, +In

–In

NTSC, G = +2, R L = 150 Ω

NTSC, G = +2, R L = 150 Ω

f = 10 MHz

f = 10 MHz

f = 5 MHz

DC PERFORMANCE

Input Offset Voltage

2.0

2.0

10

5.0

TMIN –TMAX

Offset Drift

–Input Bias Current

TMIN –TMAX

+Input Bias Current

Open-Loop Transresistance

INPUT CHARACTERISTICS

Input Resistance

Input Capacitance

Input Common-Mode Voltage Range

Common-Mode Rejection Ratio

Offset Voltage

–Input Current

+Input Current

OUTPUT CHARACTERISTICS

Output Voltage Swing

Output Current

Short Circuit Current

POWER SUPPLY

Operating Range

Quiescent Current

Power Supply Rejection Ratio

–Input Current

+Input Current

3.0

TMIN –TMAX

VO = ± 2.5 V

TMIN –TMAX

250

175

+Input

–Input

+Input

0.025

0.04

5.5

9.0

25

35

6.0

10

900

10

50

1.5

3.2

VCM = ± 2.5 V

VCM = ± 2.5 V, TMIN –TMAX

VCM = ± 2.5 V, TMIN –TMAX

50

R L = 150 Ω

R L = 37.5 Ω

2.7

50

85

54

0.3

0.2

60

50

MΩ

Ω

pF

±V

1.0

0.7

5.0

75

56

0.5

0.1

dB

µA/V

µA/V

±V

mA

mA

3.1

70

110

± 3.0

TMIN –TMAX

+VS = +4 V to +6 V, –VS = –5 V

–VS = – 4 V to – 6 V, +VS = +5 V

TMIN –TMAX

TMIN –TMAX

mV

mV

µV/°C

±µA

±µA

±µA

±µA

kΩ

kΩ

± 6.0

5.5

2.5

0.5

V

mA

dB

dB

µA/V

µA/V

Specifications subject to change without notice.

–2–

REV. D

AD8001

ABSOLUTE MAXIMUM RATINGS 1

MAXIMUM POWER DISSIPATION

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12.6 V

Internal Power Dissipation @ 25°C2

PDIP Package (N) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.3 W

SOIC (R) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.8 W

8-Lead CERDIP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.1 W

SOT-23-5 Package (RT) . . . . . . . . . . . . . . . . . . . . . . . 0.5 W

Input Voltage (Common Mode) . . . . . . . . . . . . . . . . . . . . ± VS

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . ± 1.2 V

Output Short Circuit Duration

. . . . . . . . . . . . . . . . . . . . . . Observe Power Derating Curves

Storage Temperature Range N, R . . . . . . . . . –65°C to +125°C

Operating Temperature Range (A Grade) . . . –40°C to +85°C

Lead Temperature Range (Soldering 10 sec) . . . . . . . . . 300°C

The maximum power that can be safely dissipated by the

AD8001 is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic

encapsulated devices is determined by the glass transition temperature of the plastic, approximately 150°C. Exceeding this

limit temporarily may cause a shift in parametric performance

due to a change in the stresses exerted on the die by the package.

Exceeding a junction temperature of 175°C for an extended

period can result in device failure.

2.0

MAXIMUM POWER DISSIPATION – W

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Specification is for device in free air:

8-Lead PDIP Package: θJA = 90°C/W

8-Lead SOIC Package: θJA = 155°C/W

8-Lead CERDIP Package: θJA = 110°C/W

5-Lead SOT-23-5 Package: θJA = 260°C/W

While the AD8001 is internally short circuit protected, this

may not be sufficient to guarantee that the maximum junction

temperature (150°C) is not exceeded under all conditions. To

ensure proper operation, it is necessary to observe the maximum

power derating curves.

8-LEAD

PDIP PACKAGE

TJ = +150C

8-LEAD

CERDIP PACKAGE

1.5

8-LEAD

SOIC PACKAGE

1.0

0.5

5-LEAD

SOT-23-5 PACKAGE

0

–50 –40 –30 –20 –10 0 10 20 30 40 50 60

AMBIENT TEMPERATURE – C

70

80

90

Figure 3. Plot of Maximum Power Dissipation vs.

Temperature

ORDERING GUIDE

Model

Temperature

Range

Package

Description

Package

Option

Branding

AD8001AN

AD8001AQ

AD8001AR

AD8001AR-REEL

AD8001AR-REEL7

AD8001ART-REEL

AD8001ART-REEL7

AD8001ACHIPS

5962-9459301MPA*

–40°C to +85°C

–55°C to +125°C

–40°C to +85°C

–40°C to +85°C

–40°C to +85°C

–40°C to +85°C

–40°C to +85°C

–40°C to +85°C

–55°C to +125°C

8-Lead PDIP

8-Lead CERDIP

8-Lead SOIC

13" Tape and REEL

7" Tape and REEL

13" Tape and REEL

7" Tape and REEL

Die Form

8-Lead CERDIP

N-8

Q-8

R-8

R-8

R-8

RT-5

RT-5

HEA

HEA

*

Q-8

Standard Military Drawing Device.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD8001 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

REV. D

–3–

WARNING!

ESD SENSITIVE DEVICE

AD8001–Typical Performance Characteristics

806

0.001F

+VS

VOUT TO

TEKTRONIX

CSA 404 COMM.

SIGNAL

ANALYZER

0.1F

806

AD8001

0.1F

VIN

HP8133A

PULSE

GENERATOR

50

RL = 100

0.001F

TR/TF = 50ps

–VS

400mV

5ns

TPC 4. 2 V Step Response, G = +2

TPC 1. Test Circuit , Gain = +2

909

0.001F

+VS

0.1F

VOUT TO

TEKTRONIX

CSA 404 COMM.

SIGNAL

ANALYZER

AD8001

0.1F

VIN

LeCROY 9210

PULSE

GENERATOR

TR/TF = 350ps

TPC 2. 1 V Step Response, G = +2

0.5V

50

RL = 100

0.001F

–VS

TPC 5. Test Circuit, Gain = +1

5ns

TPC 3. 2 V Step Response, G = +1

TPC 6. 100 mV Step Response, G = +1

–4–

REV. D

AD8001

1000

9

VS = 5V

RFB = 820

G = +2

RL = 100

GAIN – dB

3

0

VS = 5V

RFB = 1k

–3

VS = 5V

RL = 100

G = +2

800

–3dB BANDWIDTH – MHz

6

–6

600

N

PACKAGE

400

R

PACKAGE

200

–9

–12

10M

100M

FREQUENCY – Hz

0

500

1G

TPC 7. Frequency Response, G = +2

0.1

0

HARMONIC DISTORTION – dBc

OUTPUT – dB

–0.5

900

1000

5V SUPPLIES

RF = 750

–0.3

–0.4

800

–50

RF = 698

–0.2

700

TPC 10. –3 dB Bandwidth vs. RF

RF =

649

–0.1

600

VALUE OF FEEDBACK RESISTOR (RF) – G = +2

RL = 100

VIN = 50mV

–0.6

–0.7

–60

VOUT = 2V p-p

RL = 100

G = +2

–70

SECOND HARMONIC

–80

THIRD HARMONIC

–90

–0.8

–0.9

1M

10M

FREQUENCY – Hz

–100

10k

100M

DIFF PHASE – Degrees

–50

5V SUPPLIES

VOUT = 2V p-p

RL = 1k

G = +2

–70

SECOND HARMONIC

10M

100M

0.08

0.06

G = +2

RF = 806

2 BACK TERMINATED

LOADS (75)

0.04

0.02

0.00

1 BACK TERMINATED

LOAD (150)

–80

0.02

–90

DIFF GAIN – %

HARMONIC DISTORTION – dBc

1M

FREQUENCY – Hz

TPC 11. Distortion vs. Frequency, RL = 100 Ω

TPC 8. 0.1 dB Flatness, R Package (for N Package Add

50 Ω to RF)

–60

100k

THIRD HARMONIC

–100

–110

10k

0.00

–0.01

–0.02

100k

1M

FREQUENCY – Hz

10M

0

100M

IRE

100

TPC 12. Differential Gain and Differential Phase

TPC 9. Distortion vs. Frequency, RL = 1 kΩ

REV. D

1 AND 2 BACK TERMINATED

LOADS (150 AND 75)

0.01

–5–

AD8001

5

1000

0

N PACKAGE

900

VIN = –26dBm

–10

GAIN – dB

–3dB BANDWIDTH – MHz

–5

RF = 909

–15

–20

–25

800

R PACKAGE

700

VIN = 50mV

RL = 100

G = +1

600

–30

–35

100M

1G

500

600

3G

FREQUENCY – Hz

TPC 13. Frequency Response, G = +1

–40

0

RF = 649

–50

–1

DISTORTION – dBc

RF = 953

–2

OUTPUT – dB

1100

TPC 16. –3 dB Bandwidth vs. RF, G = +1

1

–3

–4

–5

900

700

800

1000

VALUE OF FEEDBACK RESISTOR (RF) – G = +1

RL = 100

VIN = 50mV

–6

RL = 100

G = +1

VOUT = 2V p-p

–60

SECOND HARMONIC

–70

–80

THIRD HARMONIC

–7

–90

–8

–9

2M

10M

100M

FREQUENCY – Hz

–100

10k

1G

100M

0

G = +1

RL = 1k

VOUT = 2V p-p

–3

–60

–6

OUTPUT – dBV

DISTORTION – dBc

10M

3

–40

–70

SECOND HARMONIC

–80

THIRD HARMONIC

–90

–9

–12

–15

–18

–21

–100

–110

10k

1M

FREQUENCY – Hz

TPC 17. Distortion vs. Frequency, RL = 100 Ω

TPC 14. Flatness, R Package, G = +1 (for N Package Add

100 Ω to RF)

–50

100k

RL = 100

G = +1

–24

100k

1M

FREQUENCY – Hz

10M

–27

1M

100M

TPC 15. Distortion vs. Frequency, RL = 1 kΩ

10M

FREQUENCY – Hz

100M

TPC 18. Large Signal Frequency Response, G = +1

–6–

REV. D

AD8001

45

2.2

40

2.0

30

INPUT OFFSET VOLTAGE – mV

G = +100

35

RF = 1000

25

GAIN – dB

20

G = +10

15

RF = 470

10

5

0

–5

RL = 100

–10

–15

DEVICE NO. 1

1.8

1.6

DEVICE NO. 2

1.4

1.2

1.0

DEVICE NO. 3

0.8

0.6

–20

–25

1M

10M

100M

FREQUENCY – Hz

0.4

–60

1G

3.35

5.8

3.25

5.6

3.15

+VOUT

RL = 150

VS = 5V

3.05

| –VOUT |

2.95

2.93

2.85

+VOUT

RL = 50

VS = 5V

2.75

80

100

5.4

5.2

VS = 5V

5.0

4.8

4.6

| –VOUT |

2.65

–20

0

20

40

60

JUNCTION TEMPERATURE – C

TPC 22. Input Offset vs. Temperature

SUPPLY CURRENT – mA

OUTPUT SWING – Volts

TPC 19. Frequency Response, G = +10, G = +100

–40

2.61

2.55

–60

–40

–20

0

20

40

60

JUNCTION TEMPERATURE – C

80

4.4

–60

100

125

4

120

SHORT CIRCUIT CURRENT – mA

INPUT BIAS CURRENT – A

5

3

–IN

2

1

0

–1

+IN

–2

0

20

40

60

80

100

JUNCTION TEMPERATURE – C

120

140

SOURCE ISC

115

110

| SINK ISC |

105

100

95

90

–3

–40

–20

0

20

40

60

80

100

120

85

–60

140

JUNCTION TEMPERATURE – C

–40

–20

0

20

40

60

JUNCTION TEMPERATURE – C

80

100

TPC 24. Short Circuit Current vs. Temperature

TPC 21. Input Bias Current vs. Temperature

REV. D

–20

TPC 23. Supply Current vs. Temperature

TPC 20. Output Swing vs. Temperature

–4

–60

–40

–7–

AD8001

6

1k

100

VS = 5V

RL = 150

VOUT = 2.5V

4

ROUT – TRANSRESISTANCE – k

5

3

–TZ

2

1

0

–60

1

G = +2

RF = 909

0.1

+TZ

–40

10

–20

0

20

40

60

80

100

JUNCTION TEMPERATURE – C

120

0.01

10k

140

TPC 25. Transresistance vs. Temperature

100

100k

1M

FREQUENCY – Hz

10M

TPC 28. Output Resistance vs. Frequency

100

1

RF = 576

0

–1

10

10

NONINVERTING CURRENT VS = 5V

RF = 649

–2

OUTPUT – dB

INVERTING CURRENT VS = 5V

NOISE CURRENT – pA/√Hz

NOISE VOLTAGE – nV/√Hz

100M

–3

–4

G = –1

RL = 100

VIN = 50mV

RF = 750

–5

–6

–7

–8

VOLTAGE NOISE VS = 5V

1

10

100

1k

FREQUENCY – Hz

1

100k

10k

–9

1M

10M

100M

FREQUENCY – Hz

1G

TPC 29. –3 dB Bandwidth vs. Frequency, G = –1

TPC 26. Noise vs. Frequency

–48

–52.5

–55.0

–49

–CMRR

–PSRR

–57.5

–50

PSRR – dB

CMRR – dB

–60.0

–51

+CMRR

–52

–53

2.5V SPAN

3V SPAN

–62.5

CURVES ARE FOR WORSTCASE CONDITION WHERE

ONE SUPPLY IS VARIED

WHILE THE OTHER IS

HELD CONSTANT.

–65.0

–67.5

–70.0

–54

–72.5

+PSRR

–55

–56

–60

–75.0

–40

–20

0

20

40

60

80

100

JUNCTION TEMPERATURE – C

120

–77.5

–60

140

TPC 27. CMRR vs. Temperature

–40

–20

0

20

40

60

JUNCTION TEMPERATURE – C

80

100

TPC 30. PSRR vs. Temperature

–8–

REV. D

AD8001

30

–10

10

51

150

–20

VOUT

62

0

150

PSRR – dB

CMRR – dB

910

CURVES ARE FOR WORSTCASE CONDITION WHERE

ONE SUPPLY IS VARIED

WHILE THE OTHER IS

HELD CONSTANT.

20

910

VIN

–30

–10

–PSRR

–20

–30

–40

+PSRR

–PSRR

+PSRR

–40

RF = 909

G = +2

–50

–50

–60

300k

1M

10M

FREQUENCY – Hz

100M

1M

1G

TPC 31. CMRR vs. Frequency

1G

10M

100M

FREQUENCY – Hz

TPC 34. PSRR vs. Frequency

1

RF = 549

0

–1

RF = 649

OUTPUT – dB

–2

–3

G = –2

RL = 100

VIN = 50mVrms

–4

–5

RF = 750

–6

–7

–8

10M

100M

FREQUENCY – Hz

1G

TPC 35. 2 V Step Response, G = –1

TPC 32. –3 dB Bandwidth vs. Frequency, G = –2

100

100

3 WAFER LOTS

COUNT = 895

MEAN = 1.37

STD DEV = 1.13

MIN = –2.45

MAX = +4.69

90

80

70

90

80

CUMULATIVE

70

COUNT

60

50

FREQ DIST

40

40

30

30

20

20

10

10

0

–5

–4

–3

–2

–1

0

1

2

3

INPUT OFFSET VOLTAGE – mV

4

5

TPC 36. Input Offset Voltage Distribution

TPC 33. 100 mV Step Response, G = –1

REV. D

60

50

–9–

0

PERCENT

–9

1M

AD8001

THEORY OF OPERATION

A very simple analysis can put the operation of the AD8001, a

current feedback amplifier, in familiar terms. Being a current

feedback amplifier, the AD8001’s open-loop behavior is expressed

as transimpedance, ∆VO/∆I–IN, or TZ. The open-loop transimpedance behaves just as the open-loop voltage gain of a voltage

feedback amplifier, that is, it has a large dc value and decreases

at roughly 6 dB/octave in frequency.

Since the RIN is proportional to 1/gM, the equivalent voltage

gain is just TZ × gM, where the gM in question is the transconductance of the input stage. This results in a low open-loop

input impedance at the inverting input, a now familiar result.

Using this amplifier as a follower with gain, Figure 4, basic

analysis yields the following result.

Considering that additional poles contribute excess phase at

high frequencies, there is a minimum feedback resistance below

which peaking or oscillation may result. This fact is used to

determine the optimum feedback resistance, R F. In practice,

parasitic capacitance at Pin 2 will also add phase in the feedback

loop, so picking an optimum value for R F can be difficult.

Figure 6 illustrates this problem. Here the fine scale (0.1 dB/

div) flatness is plotted versus feedback resistance. These plots

were taken using an evaluation card which is available to customers so that these results may readily be duplicated.

Achieving and maintaining gain flatness of better than 0.1 dB at

frequencies above 10 MHz requires careful consideration of

several issues.

0.1

TZ (S )

VO

=G×

VIN

TZ (S ) + G × RIN + R1

R1

R2

RF = 698

–0.1

RIN = 1 / g M ≈ 50 Ω

–0.2

OUTPUT – dB

G = 1+

RF =

649

0

R1

G = +2

–0.3

RF = 750

–0.4

–0.5

R2

–0.6

RIN

–0.7

VOUT

–0.8

VIN

–0.9

1M

10M

FREQUENCY – Hz

100M

Figure 6. 0.1 dB Flatness vs. Frequency

Figure 4. Follower with Gain

Recognizing that G × RIN << R1 for low gains, it can be seen to

the first order that bandwidth for this amplifier is independent

of gain (G). This simple analysis in conjunction with Figure 5

can, in fact, predict the behavior of the AD8001 over a wide

range of conditions.

1M

100k

Choice of Feedback and Gain Resistors

Because of the above-mentioned relationship between the bandwidth and feedback resistor, the fine scale gain flatness will, to

some extent, vary with feedback resistance. It, therefore, is

recommended that once optimum resistor values have been

determined, 1% tolerance values should be used if it is desired to

maintain flatness over a wide range of production lots. In addition,

resistors of different construction have different associated parasitic

capacitance and inductance. Surface-mount resistors were used

for the bulk of the characterization for this data sheet. It is not

recommended that leaded components be used with the AD8001.

TZ – 10k

1k

100

10

100k

1M

10M

FREQUENCY – Hz

100M

1G

Figure 5. Transimpedance vs. Frequency

–10–

REV. D

AD8001

Printed Circuit Board Layout Considerations

Driving Capacitive Loads

As to be expected for a wideband amplifier, PC board parasitics

can affect the overall closed-loop performance. Of concern are

stray capacitances at the output and the inverting input nodes. If

a ground plane is to be used on the same side of the board as

the signal traces, a space (5 mm min) should be left around the

signal lines to minimize coupling. Additionally, signal lines

connecting the feedback and gain resistors should be short

enough so that their associated inductance does not cause high

frequency gain errors. Line lengths on the order of less than

5 mm are recommended. If long runs of coaxial cable are being

driven, dispersion and loss must be considered.

The AD8001 was designed primarily to drive nonreactive loads.

If driving loads with a capacitive component is desired, best

frequency response is obtained by the addition of a small series

resistance, as shown in Figure 8. The accompanying graph

shows the optimum value for RSERIES versus capacitive load. It is

worth noting that the frequency response of the circuit when

driving large capacitive loads will be dominated by the passive

roll-off of RSERIES and CL.

909

Power Supply Bypassing

RSERIES

Adequate power supply bypassing can be critical when optimizing the performance of a high frequency circuit. Inductance in

the power supply leads can form resonant circuits that produce

peaking in the amplifier’s response. In addition, if large current

transients must be delivered to the load, then bypass capacitors

(typically greater than 1 µF) will be required to provide the best

settling time and lowest distortion. A parallel combination of

4.7 µF and 0.1 µF is recommended. Some brands of electrolytic

capacitors will require a small series damping resistor ≈4.7 Ω for

optimum results.

IN

RL

500

CL

Figure 8. Driving Capacitive Loads

40

G = +1

DC Errors and Noise

R

R

VOUT = VIO × 1 + F ± I BN × RN × 1 + F ± I BI × RF

RI

RI

RF

RI

RN

IBI

IBN

VOUT

Figure 7. Output Offset Voltage

REV. D

–11–

30

RSERIES – There are three major noise and offset terms to consider in a

current feedback amplifier. For offset errors, refer to the equation

below. For noise error the terms are root-sum-squared to give a

net output error. In the circuit in Figure 7 they are input offset

(VIO), which appears at the output multiplied by the noise gain

of the circuit (1 + RF/RI), noninverting input current (IBN × RN)

also multiplied by the noise gain, and the inverting input current,

which when divided between RF and RI and subsequently

multiplied by the noise gain always appears at the output as

IBN × RF. The input voltage noise of the AD8001 is a low 2 nV/

√Hz. At low gains though the inverting input current noise times

RF is the dominant noise source. Careful layout and device

matching contribute to better offset and drift specifications for

the AD8001 compared to many other current feedback amplifiers. The typical performance curves in conjunction with the

following equations can be used to predict the performance of

the AD8001 in any application.

20

10

0

0

5

10

15

20

25

CL – pF

Figure 9. Recommended RSERIES vs. Capacitive Load

AD8001

Communications

Operation as a Video Line Driver

Distortion is a key specification in communications applications.

Intermodulation distortion (IMD) is a measure of the ability of

an amplifier to pass complex signals without the generation of

spurious harmonics. The third order products are usually the

most problematic since several of them fall near the fundamentals

and do not lend themselves to filtering. Theory predicts that the

third order harmonic distortion components increase in power at

three times the rate of the fundamental tones. The specification

of third order intercept as the virtual point where fundamental and

harmonic power are equal is one standard measure of distortion

performance. Op amps used in closed-loop applications do not

always obey this simple theory. At a gain of +2, the AD8001

has performance summarized in Figure 10. Here the worst third

order products are plotted versus input power. The third order

intercept of the AD8001 is +33 dBm at 10 MHz.

The AD8001 has been designed to offer outstanding performance as a video line driver. The important specifications of

differential gain (0.01%) and differential phase (0.025°) meet

the most exacting HDTV demands for driving one video load.

The AD8001 also drives up to two back terminated loads as

shown in Figure 11, with equally impressive performance (0.01%,

0.07°). Another important consideration is isolation between

loads in a multiple load application. The AD8001 has more

than 40 dB of isolation at 5 MHz when driving two 75 Ω back

terminated loads.

909

75

75 CABLE

909

+VS

VOUT NO. 1

75

0.001F

+

0.1F

–45

THIRD ORDER IMD – dBc

–50

G = +2

F1 = 10MHz

75

CABLE

F2 = 12MHz

AD8001

VIN

2F2 – F1

–55

75

75 CABLE

0.1F

VOUT NO. 2

75

75

–60

0.001F

2F1 – F2

–65

–VS

Figure 11. Video Line Driver

–70

–75

–80

–8 –7

–6

–5

–4

–3 –2 –1 0

1

INPUT POWER – dBm

2

3

4

5

6

Figure 10. Third Order IMD; F1 = 10 MHz, F2 = 12 MHz

–12–

REV. D

AD8001

ADC. Using the AD9058’s internal +2 V reference connected

to both ADCs as shown in Figure 12 reduces the number of

external components required to create a complete data

acquisition system. The 20 Ω resistors in series with ADC inputs

are used to help the AD8001s drive the 10 pF ADC input

capacitance. The AD8001 only adds 100 mW to the power

consumption while not limiting the performance of the circuit.

Driving A-to-D Converters

The AD8001 is well suited for driving high speed analog-todigital converters such as the AD9058. The AD9058 is a dual

8-bit 50 MSPS ADC. In the circuit below, the AD8001 is

shown driving the inputs of the AD9058, which are configured

for 0 V to 2 V ranges. Bipolar input signals are buffered, amplified

(–2×), and offset (by +1.0 V) into the proper input range of the

1k

ENCODE

74ACT04

10

ENCODE A

8

649

38

ANALOG

IN A

0.5V

324

10pF

50

36

ENCODE B

–VREF A

+VS

–VREF B

5, 9, 22,

24, 37, 41

AD9058

20

AD8001

6

RZ1

(J-LEAD)

AIN A

1.3k

+5V

0.1F

D0A (LSB)

18

17

AD707

0.1F

20k

20k

3

0.1F

43

15

+VINT

14

+VREF A

13

+VREF B

12

D7A (MSB)

1.3k

649

D0B (LSB)

324

28

RZ2

29

30

20

AD8001

40

31

AIN B

32

33

1

D7B (MSB)

–VS

RZ1, RZ2 = 2,000 SIP (8-PKG)

35

7, 20,

26, 39

0.1F

4,19, 21

25, 27, 42

Figure 12. AD8001 Driving a Dual A-to-D Converter

REV. D

–13–

8

34

COMP

0.1F

8

11

74ACT 273

ANALOG

IN B

0.5V

74ACT 273

16

2

–2V

–5V

1N4001

CLOCK

AD8001

(4.7 µF–10 µF) tantalum electrolytic capacitor should be connected in parallel, but not necessarily so close, to supply current

for fast, large-signal changes at the output.

Layout Considerations

The specified high speed performance of the AD8001 requires

careful attention to board layout and component selection. Proper

RF design techniques and low parasitic component selection

are mandatory.

The feedback resistor should be located close to the inverting

input pin in order to keep the stray capacitance at this node to a

minimum. Capacitance variations of less than 1 pF at the inverting input will significantly affect high speed performance.

The PCB should have a ground plane covering all unused portions

of the component side of the board to provide a low impedance

ground path. The ground plane should be removed from the area

near the input pins to reduce stray capacitance.

Stripline design techniques should be used for long signal traces

(greater than about 1 inch). These should be designed with a

characteristic impedance of 50 Ω or 75 Ω and be properly terminated at each end.

Chip capacitors should be used for supply bypassing (see Figure 13).

One end should be connected to the ground plane and the other

within 1/8 inch of each power pin. An additional large

RF

RF

+VS

+VS

+VS

C1

0.1F

RG

IN

RO

RT

RG

C3

10F

RO

OUT

OUT

C2

0.1F

RS

–VS

IN

C4

10F

RT

–VS

Inverting Configuration

Supply Bypassing

–VS

Noninverting Configuration

Figure 13. Inverting and Noninverting Configurations for Evaluation Boards

Table I. Recommended Component Values

AD8001AN (PDIP)

Gain

AD8001AR (SOIC)

Gain

AD8001ART (SOT-23-5)

Gain

Component

–1

+1

+2

+10

+100

–1

+1

+2

+10

+100

–1

+1

RF (Ω)

RG (Ω)

RO (Nominal) (Ω)

RS (Ω)

RT (Nominal) (Ω)

Small Signal

BW (MHz)

0.1 dB Flatness

(MHz)

649

649

49.9

0

54.9

340

1050

470

51

49.9

1000

10

49.9

49.9

681

681

49.9

470

51

49.9

1000

10

49.9

49.9

880

49.9

460

49.9

260

49.9

20

604

604

49.9

0

54.9

370

953

49.9

750

750

49.9

49.9

710

49.9

440

49.9

260

49.9

20

845

845

49.9

0

54.9

240

70

105

130

100

120

110

105

–14–

+2

+10

+100

1000 768

768

49.9 49.9

470

51

49.9

1000

10

49.9

49.9

795

49.9

380

49.9

260

49.9

20

300

145

REV. D

AD8001

OUTLINE DIMENSIONS

8-Lead Plastic Dual In-Line Package [PDIP]

(N-8)

8-Lead Ceramic Dual In-Line Package [CERDIP]

(Q-8)

Dimensions shown in inches and (millimeters)

Dimensions shown in inches and (millimeters)

0.375 (9.53)

0.365 (9.27)

0.355 (9.02)

0.005 (0.13)

MIN

0.055 (1.40)

MAX

8

8

5

0.295 (7.49)

0.285 (7.24)

0.275 (6.98)

4

1

1

0.100 (2.54)

BSC

0.015

(0.38)

MIN

0.150 (3.81)

0.130 (3.30)

0.110 (2.79)

0.022 (0.56)

0.018 (0.46)

0.014 (0.36)

0.310 (7.87)

0.220 (5.59)

PIN 1

0.325 (8.26)

0.310 (7.87)

0.300 (7.62)

0.180

(4.57)

MAX

5

0.100 (2.54) BSC

0.150 (3.81)

0.135 (3.43)

0.120 (3.05)

0.320 (8.13)

0.290 (7.37)

0.405 (10.29) MAX

0.060 (1.52)

0.015 (0.38)

0.200 (5.08)

MAX

0.150 (3.81)

MIN

0.200 (5.08)

0.125 (3.18)

0.015 (0.38)

0.010 (0.25)

0.008 (0.20)

SEATING

PLANE

0.060 (1.52)

0.050 (1.27)

0.045 (1.14)

4

SEATING

0.070 (1.78) PLANE

0.030 (0.76)

0.023 (0.58)

0.014 (0.36)

0.015 (0.38)

0.008 (0.20)

15

0

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETERS DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

COMPLIANT TO JEDEC STANDARDS MO-095AA

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

8-Lead Standard Small Outline Package [SOIC]

(R-8)

5-Lead Small Outline Transistor Package [SOT-23]

(RT-5)

Dimensions shown in millimeters and (inches)

Dimensions shown in millimeters

5.00 (0.1968)

4.80 (0.1890)

4.00 (0.1574)

3.80 (0.1497)

8

5

1

4

2.90 BSC

5

6.20 (0.2440)

5.80 (0.2284)

2.80 BSC

1.60 BSC

1

1.27 (0.0500)

BSC

0.25 (0.0098)

0.10 (0.0040)

COPLANARITY

SEATING

0.10

PLANE

1.75 (0.0688)

1.35 (0.0532)

0.51 (0.0201)

0.31 (0.0122)

4

0.50 (0.0196)

ⴛ 45ⴗ

0.25 (0.0099)

2

3

PIN 1

0.95 BSC

1.30

1.15

0.90

8ⴗ

0.25 (0.0098) 0ⴗ 1.27 (0.0500)

0.40 (0.0157)

0.17 (0.0067)

1.90

BSC

1.45 MAX

COMPLIANT TO JEDEC STANDARDS MS-012AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

0.15 MAX

0.50

0.30

SEATING

PLANE

0.22

0.08

10ⴗ

5ⴗ

0ⴗ

COMPLIANT TO JEDEC STANDARDS MO-178AA

REV. D

–15–

0.60

0.45

0.30

AD8001

Location

Page

7/03—Data Sheet changed from REV. C to REV. D

Renumbered figures and TPCs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Universal

Changes to ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Updated OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

–16–

REV. D

C01043–0–7/03(D)

Revision History

a

Precision JFET-Input

Operational Amplifiers

OP15/OP17

FEATURES

Significant Performance Advantages over LF155 and

LF157 Devices

Low Input Offset Voltages: 500 V Max

Low Input Offset Voltage Drift: 2.0 V/ⴗC

Minimum Slew Rate Guaranteed on All Models

Temperature-Compensated Input Bias Currents

Bias Current Specified Warmed-Up Over Temperature

Internal Compensation

÷ Hz

Low Input Noise Current: 0.01 pA/÷

High Common-Mode Rejection Ratio: 100 dB

Models with MIL-STD 883 Processing Available

GENERAL DESCRIPTION

The ADI-JFET input series of devices offer clear advantages over

industry-generic devices and are superior in both cost and performance to many dielectrically-isolated and hybrid op amps. All devices

offer offset voltages as low as 0.5 mV with TCVOS guaranteed to

5 mV/∞C. A unique input bias cancellation circuit reduces the IB

by a factor 10 over conventional designs. In addition ADI specifies

IB and IOS with the devices warmed up and operating at 25∞C ambient.

These devices were designed to provide real precision performance

along with high speed. Although they can be nulled, the design

objective was to provide low offset-voltage without nulling. Systems

generally become more cost effective as the number of trim circuits

is decreased. ADI achieves this performance by use of an improved

bipolar compatible JFET process coupled with on chip, zener-zap

offset trimming.

OP15

156 Speed with 155 Dissipation: 80 mW Typ

Wide Bandwidth: 6 MHz

High Slew Rate: 13 V/s

Fast Settling to ±0.1%: 1,200 ns

The OP15 provides an excellent combinations of high speed and

low input offset voltage. In addition, the OP15 offers the speed

of the 156A op amp with the power dissipation of a 155A. The

combination of a low input offset voltage of 500 mV, slew rate of

13 V/ms, and settling time of 1,200 ns to 0.1% makes the OP15

an op amp of both precision and speed. The additional features

of low supply current coupled with an input bias current makes

the OP15 ideal for a wide range of applications.

OP17

Highest Slew Rate: 60 V/s

Fastest Settling to ±0.1%: 600 ns

Highest Gain Bandwidth Product (AVCL = 5 Min): 30 MHz

Guaranteed Input Bias Current @ 125ⴗC

The OP17 has a slew rate of 60 V/ms and is the best choice for

applications requiring high closed-loop gain with high speed. See

OP42 datasheet for unity gain applications and the OP215 datasheet

for a dual configuration of the OP15.

V+

J5

Q5

R8*

NULL

*R7, R8 ARE ELECTRONICALLY

ADJUSTED ON CHIP FOR

MINIMUM OFFSET VOLTAGE.

R7*

NULL

J8

Q16

Q6

Q7

R3

Q9

J6

Q19

Q24

Q8

R1

J11

NONINVERTING

INPUT

J1

Q17

J2

R2

–INV

INPUT

Q1

Q22

OUTPUT

Q2

Q3

R13

C2

Q10

Q4

J10

Q12

Q23

J9

Q11

J3

C1

7.4pF

J4

R3

R4

R5

3.6k⍀

Q16

Q13

R6

3.6k⍀

Q15

Q14

Q20

Q21

Q25

R11

V–

Figure 1. Simplified Schematic

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2002

OP15/OP17–SPECIFICATIONS

ELECTRICAL CHARACTERISTICS (@ V = ⴞ15 V, T = 25ⴗC, unless otherwise noted)

S

Parameter

A

OP15A, OP15E

OP17A, OP17E

Min

Typ

Max

Symbol

Conditions

Max

Unit

VOS

RS = 50 W

0.2

0.5

0.4

1.0

0.5

3.0

mV

Input Offset Current

OP15

IOS

TJ = 25∞C1

Device Operating

TJ = 25∞C1

Device Operating

3

5

3

5

10

22

10

25

6

10

6

10

20

40

20

50

12

20

12

20

50

100

50

125

pA

pA

pA

pA

TJ = 25∞C1

Device Operating

TJ = 25∞C1

Device Operating

± 15

± 18

± 15

± 20

± 50

± 110

± 50

± 130

± 30

± 40

± 30

± 40

± 100

± 200

± 100

± 250

± 60

± 80

± 60

± 80

± 200

± 400

± 200

± 500

pA

pA

pA

pA

Input Bias Current

OP15

IB

OP17

1012

Max

Min

OP15G

OP17G

Typ

Input Offset Voltage

OP17

Min

OP15F

OP17F

Typ

1012

W

50

200

V/mV

± 12

± 11

± 13

± 12.7

V

V

1012

Input Resistance

RIN

Large-Signal

Voltage Gain

AVO

RL ≥ 2 kW

VO = ± 10 V

100

240

75

220

Output Voltage

Swing

VO

RL = 10 kW

RL = 2 kW

± 12

± 11

± 13

± 12.7

± 12

± 11

± 13

± 12.7

Supply Current

ISY

OP15

OP17

Slew Rate2

SR

AVCL = 1, OP15

AVCL = 5, OP17

10

45

13

60

7.5

35

11

50

5

25

9

40

V/ms

V/ms

Gain Bandwidth3

Product

GBW

OP15

OP17

4.0

20

6.0

30

3.5

15

5.7

28

3.0

11

5.4

26

MHz

MHz

Closed-Loop

Bandwidth

CLBW

AVCL = 1, OP15

AVCL = 5, OP17

14

11

13

10

12

9

MHz

MHz

Settling Time

OP15

tS

To 0.01%

To 0.05%

To 0.10%

To 0.01%

To 0.05%

To 0.10%

4.5

1.5

1.2

1.5

0.7

0.6

4.5

1.5

1.2

1.5

0.7

0.6

4.7

1.6

1.3

1.6

0.8

0.7

ms

ms

ms

ms

ms

ms

OP17

Input Voltage Range

IVR

Common-Mode

Rejection Ratio

CMRR

Power Supply

Rejection Ratio

PSRR

Input Noise

Voltage Density

Input Noise

Current Density

Input Capacitance

2.7

4.6

4.0

7.0

± 10.5

VCM = ± 10.5 V

VCM = ± 10.3 V

86

2.7

4.6

4.0

7.0

± 10.5

100

86

2.8

4.8

5.0

8.0

± 10.3

V

100

82

mA

mA

dB

dB

96

VS = ± 10 V to ± 18 V

VS = ± 10 V to ± 18 V

10

en

fO = 100 Hz

fO = 1 kHz

20

15

20

15

20

15

nV/÷Hz

nV/÷Hz

in

fO = 100 Hz

fO = 1 kHz

0.01

0.01

0.01

0.01

0.01

0.01

pA/÷Hz

pA/÷Hz

3

3

3

pF

CIN

51

10

51

10

80

mV/V

mV/V

NOTES

1

Input bias current is specified for two different conditions. The T J = 25∞C specification is with the junction at ambient temperature; the device operating specification

is with the device operating in a warmed-up condition at 25∞C ambient. The warmed-up bias current value is correlated to the junction temperature value via the

curves of I B versus TJ and IB versus TA. ADI has a bias current compensation circuit which gives improved bias current over the standard JFET input op amps. I B and

IOS are measured at VCM = 0.

2

Settling time is defined here for a unity gain inverter connection using 2 k W resistors. It is the time required for the error voltage (the voltages at the inverting input pit

on the amplifier) to settle to within a specified percent of its final value from the time a 10 V step input is applied to the inverter. See settling time test circuit.

3

Sample tested.

4

Settling time is defined here for A V = –5 connection with RF = 2 kW. It is the time required for the error voltage (the voltage at the inverting input pin on the amplifier) to

settle to within 0.01% of its final value from the time a 2 V step input is applied to the inverter. See settling time test circuit.

–2–

REV. A

OP15/OP17

Electrical Characteristics (@ V = ±15 V, –55ⴗC £ T £ 125ⴗC, unless otherwise noted.)

S

Parameter

Input Offset Voltage

A

Symbol

Conditions

VOS

TCVOS

TCVOS

Min

Typ

Max

Units

RS = 50 W

0.4

0.9

mV

RP = 100 W

2

2

5

mV/∞C

mV/∞C

1

Average Input Offset Voltage Drift

Without External Trim

With External Trim

Input Offset Current2

OP17

IOS

TJ = 125∞C

TA = 125∞C, device operating

0.6

1.0

4.0

8.5

nA

nA

Input Bias Current2

OP17

IB

TJ = 125∞C

TA = 125∞C, device operating

± 1.2

± 2.0

± 5.0

± 11

nA

nA

Input Voltage Range

IVR

Common-Mode Rejection Ratio

CMRR

VCM = ± 10.4 V

Power Supply Rejection Ratio

PSRR

VS = ± 10 V to ± 18 V

Large Signal Voltage Gain

AVO

RL ≥ 2 kW, VO = ± 10 V

35

120

V/mV

Output Voltage Swing

VO

RL ≥ 10 kW

± 12

± 13

V

± 10.4

85

V

97

dB

15

mV/V

57

NOTES

1

Sample tested.

2

Input bias current is specified for two different conditions. The T J = 25∞C specification is with the junction at ambient temperature; the device operating specification

is with the device operating in a warmed-up condition at 25∞C ambient. The warmed-up bias current value is correlated to the junction temperature value via the

curves of I B versus TJ and IB versus TA. ADI has a bias current compensation circuit which gives improved bias current over the standard JFET input op amps. I B and

IOS are measured at VCM = 0.

ELECTRICAL CHARACTERISTICS

Parameter

Input Offset Voltage

OP15E/OP17E

Min

Typ

Max

OP15F/OP17F

Min

Typ

Max

OP15G/OP17G

Min

Typ

Max

Unit

1.5

0.7

3.8

mV

3

3

10

4

4

30

mV/∞C

mV/∞C

0.30

0.55

0.30

0.70

0.06

0.08

0.06

0.10

0.45

0.80

0.45

1.1

0.08

0.10

0.08

0.15

0.85

1.2

0.85

1.7

nA

nA

nA

nA

± 0.40

± 0.75

± 0.40

± 0.90

± 0.12

± 0.16

± 0.12

± 0.20

± 0.60

± 1.1

± 0.60

± 1.4

± 0.14

± 0.19

± 0.14

± 0.25

± 0.80

± 1.5

± 0.80

± 2.0

nA

nA

nA

nA

Symbol

Conditions

VOS

RS = 50 W

0.3

0.75

0.55

RP = 100 W

2

2

5

TJ = 70∞C

TA = 70∞C, Device Operating

TJ = 70∞C

TA = 70∞C, Device Operating

0.04

0.06

0.04

0.07

TJ = 70∞C

TA = 70∞C, Device Operating

TJ = 70∞C

TA = 70∞C, Device Operating

± 0.10

± 0.13

± 0.10

± 0.15

Average Input Offset

Voltage Drift1

Without External Trim TCVOS

With External Trim TCVOSn

Input Offset Current2 IOS

OP15

OP17

Input Bias Current2

OP15

(@ VS = ⴞ15 V, 0ⴗC £ TA £ 70ⴗC for E and F grades, –40ⴗC £ TA £ 85ⴗC for G grades

unless otherwise noted)

IB

OP17

± 10.4

± 10.4

± 10.25

V

80

dB

dB

Input Voltage Range

IVR

Common-Mode

Rejection Ratio

CMRR

Power Supply

Rejection Ratio

PSRR

Large Signal

Voltage Gain

AVO

RL ≥ 2 kW

VO = ± 10 V

65

200

50

180

35

160

V/mV

Output Voltage

Swing

VO

RL ≥ 10 kW

± 12

± 13

± 12

± 13

± 12

± 13

V

VCM = ± 10.4 V

VCM = ± 10.25 V

85

VS = ± 10 V to ± 18 V

VS = ± 10 V to ± 15 V

98

13

85

57

96

13

94

57

20

100

mV/V

mV/V

NOTES

1

Sample tested.

2

Input bias current is specified for two different conditions. The T J = 25∞C specification is with the junction at ambient temperature; the device operating specification

is with the device operating in a warmed-up condition at 25∞C ambient. The warmed-up bias current value is correlated to the junction temperature value via the

curves of I B versus TJ and IB versus TA. ADI has a bias current compensation circuit which gives improved bias current over the standard JFET input op amps. I B and

IOS are measured at VCM = 0.

REV. A

–3–

OP15/OP17–SPECIFICATIONS

ABSOLUTE MAXIMUM RATINGS 1

Supply Voltage

All Devices Except C, G (Packaged)

and GR Grades . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 22 V

C, G (Packaged) and GR Grades . . . . . . . . . . . . . . . . ± 18 V

Operating Temperature

A Grade . . . . . . . . . . . . . . . . . . . . . . . . . . –55∞C to +125∞C

E, F Grades . . . . . . . . . . . . . . . . . . . . . . . . . . . 0∞C to 70∞C

G Grade . . . . . . . . . . . . . . . . . . . . . . . . . . . –40∞C to +85∞C

Maximum Junction Temperature . . . . . . . . . . . . . . . . . 150∞C

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . .

All Devices Except C, G Grades . . . . . . . . . . . . . . . . ± 40 V

C, G Grades . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 30 V

Input Voltage2

All Devices Except C, G Grades . . . . . . . . . . . . . . . . ± 20 V

C, G Grades . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 16 V

Input Voltage

OP15E, OP15F . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 20 V

OP15G . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 16 V

OP17A, OP17E, OP17F . . . . . . . . . . . . . . . . . . . . . . ± 20 V

OP17G . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 16 V

Output Short-Circuit Duration

Indefinite

Storage Temperature Range . . . . . . . . . . . . –65∞C to +150∞C

Lead Temperature Range (Soldering, 60 sec) . . . . . . . . 300∞C

Package Type

JA*

JC

Unit

8-Lead Hermetic DIP (Z)

8-Lead SO (S)

TO-99 (J)

148

158

150

16

43

18

∞C/W

∞C/W

∞C/W

*JA is specified for worst-case mounting conditions, i.e., JA is specified for device

in socket for CERDIP and PDIP packages; JA is specified for device soldered to

printed circuit board for SO packages.

+20V

10k⍀

2

7

8

3

+3V

300⍀

4

10k⍀

–20V

Figure 2. Burn-In Circuit

NOTES

*Absolute Maximum Ratings apply to packaged parts, unless otherwise noted.

8-Lead CERDIP

(Z-Suffix)

8-Lead SOIC

(S-Suffix)

1

8 NC

BAL

–IN

2

7 V+

+IN

3

6 OUT

V–

4

5 BAL

BAL

8-Lead TO-99

(J-Suffix)

1

8 NC

–IN

2

7 V+

+IN

3

6 OUT

V–

4

5 BAL

ORDERING GUIDE

TA = 25∞C

VOS MAX

(mV)

Package Options

TO-99

CERDIP

0.5

OP17EJ

OP15EZ

OP17EZ

COM

1.0

OP15FJ*

OP17FJ

OP15FZ*

OP17FZ

COM

3.0

OP15GJ*

OP15GZ*

OP17GZ

SOIC

OP15GS*

Operating

Temperature

Range

XIND

For military processed devices, please refer to the Standard Microcircuit Drawing

(SMD) available at www.dscc.dl.mil/programs/milspec/default.asp.

SMD Part Number

ADI Equivalent

5962-8954201GA*

5962-8954201PA*

5962-8954301GA*

5962-8954301PA*

OP15AJMDA

OP15AZMDA

OP16AJMDA

OP16AZMDA

*Not recommended for new designs. Obsolete April 2002.

–4–

REV. A

Typical Performance Characteristics –OP15/OP17

30

100

WARMED-UP IN FREE AIR

VS = 15V

TA = 25ⴗC

VS = 15V

PEAK-TO-PEAK OUTPUT SWING – V

27

80

INPUT BIAS CURRENT – pA

24

–55ⴗC

21

+25ⴗC

18

15

+125ⴗC

12

9

60

a. UNDERCANCELLED IB = +16pA @ V CM = 0

b. PERFECTLY CANCELLED IB = 0pA @ V CM = 0

c. UNDERCANCELLED IB = –16pA @ V CM = 0

40

20

a

c

b

6

0

3

0

100

–20

–12 –10

100k

1k

10k

OUTPUT LOAD RESISTANCE – ⍀

–6 –4 –2

0

2

4

6

INPUT COMMON-MODE VOLTAGE – V

8

10

12

TPC 4. Input Bias Current vs. Common-Mode Voltage

TPC 1. Maximum Output Swing vs. Load Performance

1M

20

COMMON-MODE INPUT VOLTAGE RANGE – V

–8

RL = 2k⍀

OPEN-LOOP VOLTAGE GAIN – V/V

TA = 25ⴗC

15

10

POSITIVE

5

FROM –55ⴗC TO –125ⴗC

CHANGE IN CMVR IS < 0.2V

500k

400k

–55ⴗC

300k

200k

25ⴗC

125ⴗC

100k

NEGATIVE

0

10k

0

5

10

SUPPLY VOLTAGE – V

15

20

5

TPC 2. Common-Mode Input Voltage Range vs. Supply

Voltage

40

TA = 25ⴗC

VS = 15V

100Hz < f < 10kHz

10Hz < f < 10kHz FOR RS > 4M⍀

a AMPLIFIER NOISE

b JOHNSON RESISTOR NOISE

c AMPLIFIER NOISE MEASURED

WITH SOURCE RESISTOR

c

PEAK-TO-PEAK OUTPUT SWING – V

INPUT NOISE VOLTAGE – V

10

20

TPC 5. Open-Loop Voltage Gain vs. Supply Voltage

1k

100

10

15

SUPPLY VOLTAGE – V

b

1

0.1

RL = 2k⍀

TA = 25ⴗC

30

20

10

a

0.01

100k

0

1M

10M

100M

SOURCE RESISTANCE – ⍀

1G

10G

5

10

SUPPLY VOLTAGE – V

15

20

TPC 6. Output Voltage Swing vs. Supply Voltage

TPC 3. Voltage Noise vs. Source Resistance

REV. A

0

–5–

OP15/OP17

1n

VS = 15V

TA = 25ⴗC

ISY = 4.0mA FOR MAX CURVES

2.5mA FOR TYP CURVES

7

INPUT BIAS CURRENT – A

NULLED OFFSET VOLTAGE DRIFT – V/ⴗC

9

5

VOS

3

1

TYPICAL DRIFT BAND

–1

155A MAX

OP15A MAX

100p

155A TYP

–3

OP15 TYP

–5

10k

100k

RP-TRIMMING POTENTIOMETER VALUE – ⍀

10p

1M

0

TPC 7. Nulled Offset Voltage Drift vs. Potentiometer Size

20

40

60

80

100

TIME AFTER POWER APPLIED – s

120

140

TPC 10. OP15 Bias Current vs. Time in Free Air

6

1n

VS = 15V

156A/157A MAX

INPUT BIAS CURRENT – A

OFFSET VOLTAGE – mV